By Intel® FPGAs 116

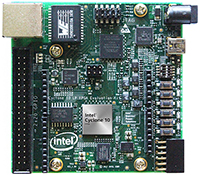

Built on a power-optimized 60 nm process, Intel® Cyclone® 10 LP FPGAs extend the low-power leadership of the previous generation Cyclone® V FPGAs. The latest generation devices reduce core static power by up to 50 percent compared to the previous generations. All Intel Cyclone 10 LP FPGAs require only two core power supplies for operation, simplifying the power distribution network and saving board costs, board space, and design time. The flexibility of the Intel Cyclone 10 LP FPGA enables the user to design in a smaller, lower cost device, lowering total system costs.

The logic and routing core fabric sea of gates is surrounded on each side by I/O elements with a phase-locked loop (PLLs) in each corner. Embedded memory blocks (M9K) and 18 bit x 18 bit multipliers blocks are arranged in vertical columns. The architecture also includes highly efficient interconnect and low-skew clock networks, providing connectivity between logic structures for clock and data signals.