By Analog Devices Inc 60

ADI's AD4000/AD4004/AD4008 are low noise, low power, high speed, 16-bit, successive approximation register (SAR) analog-to-digital converters (ADCs) at 2 MSPS, 1 MSPS, and 500 kSPS, respectively. The high-Z mode coupled with a long acquisition phase eliminates the need for a dedicated high power, high-speed ADC driver, thus broadening the range of low power precision amplifiers that can drive this ADC directly while still achieving optimum performance. The input span compression feature enables the ADC driver amplifier and the ADC to operate off common supply rails without the need for a negative supply while preserving the full ADC code range. The low serial peripheral interface (SPI) clock rate requirement reduces the digital input/output power consumption, broadens processor options, and simplifies the task of sending data across digital isolation. Operating from a 1.8 V supply, these ADCs sample an analog input (IN+) between 0 V to VREF with respect to a ground sense (IN−) with VREF ranging from 2.4 V to 5.1 V.

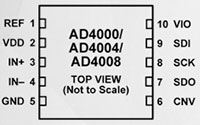

The reference voltage is applied externally and can be set independently of the supply voltage. The SPI-compatible versatile serial interface features seven different modes including the ability, using the SDI input, to daisy-chain several ADCs on a single 3-wire bus and provides an optional busy indicator. The AD4004 is compatible with 1.8 V, 2.5 V, 3 V, and 5 V logic, using the separate VIO supply. The AD4000/AD4004/AD4008 are available in an MSOP or LFCSP with operation specified from -40°C to +125°C. The AD4000/AD4004/AD4008 are ideal for medical equipment, machine automation, and battery-powered equipment applications.

| Features | ||

|

|