XC9536 In-System Programmable CPLD

DS064 (v6.3) April 3, 2006 www.xilinx.com 5

Product Specification

R

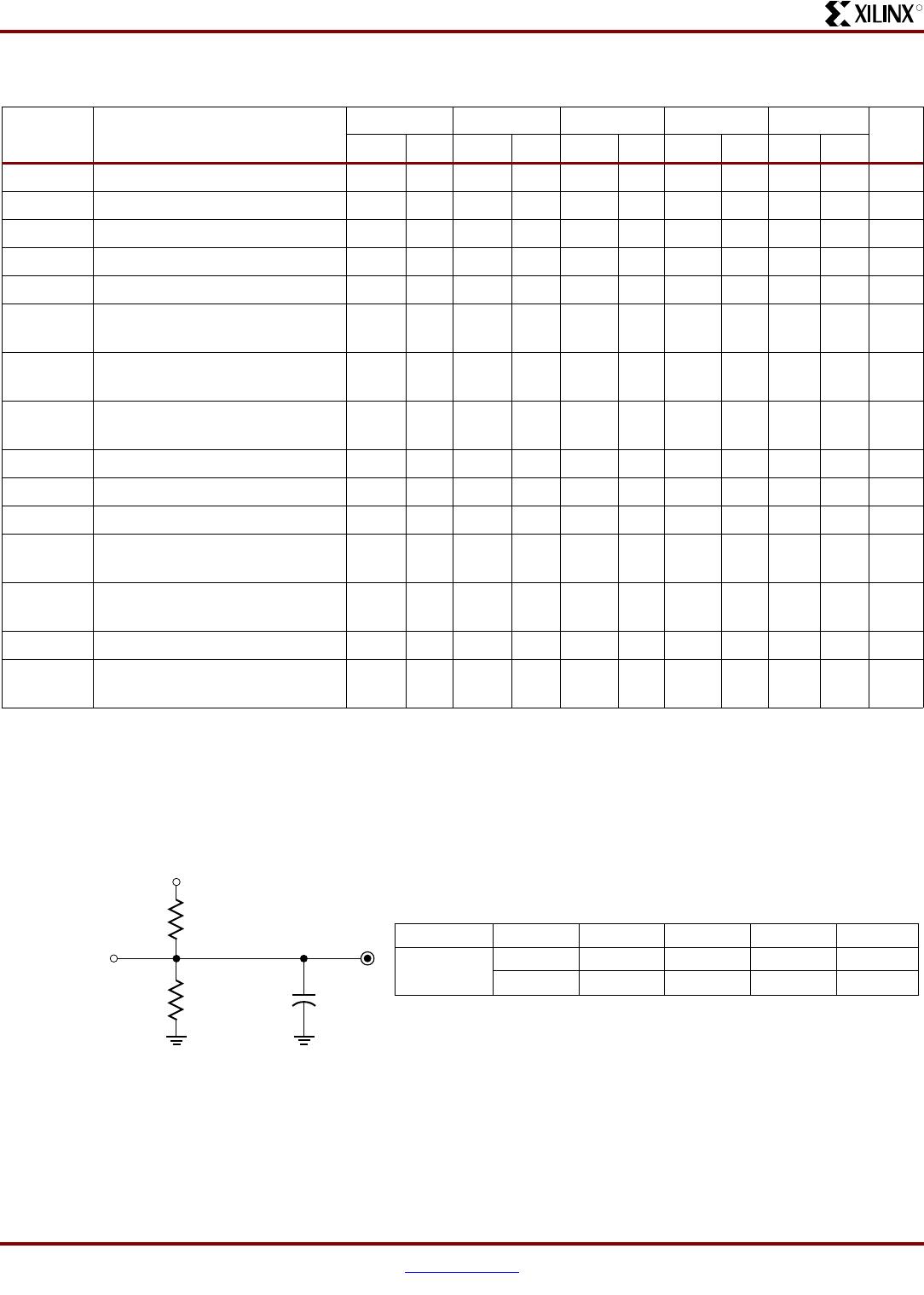

Internal Timing Parameters

Symbol Parameter

XC9536-5 XC9536-6 XC9536-7 XC9536-10 XC9536-15

UnitsMinMaxMinMaxMinMaxMinMaxMinMax

Buffer Delays

T

IN

Input buffer delay - 1.5 - 1.5 - 2.5 - 3.5 - 4.5 ns

T

GCK

GCK buffer delay - 1.5 - 1.5 - 1.5 - 2.5 - 3.0 ns

T

GSR

GSR buffer delay - 4.0 - 4.0 - 4.5 - 6.0 - 7.5 ns

T

GTS

GTS buffer delay - 5.0 - 5.0 - 5.5 - 6.0 - 11.0 ns

T

OUT

Output buffer delay - 2.0 - 2.0 - 2.5 - 3.0 - 4.5 ns

T

EN

Output buffer enable/disable delay - 0 - 0 - 0 - 0 - 0 ns

Product Term Control Delays

T

PTCK

Product term clock delay - 3.0 - 3.0 - 3.0 - 3.0 - 2.5 ns

T

PTSR

Product term set/reset delay - 1.0 - 1.0 - 2.0 - 2.5 - 3.0 ns

T

PTTS

Product term 3-state delay - 5.5 - 5.5 - 4.5 - 3.5 - 5.0 ns

Internal Register and Combinatorial Delays

T

PDI

Combinatorial logic propagation delay - 0.5 - 0.5 - 0.5 - 1.0 - 3.0 ns

T

SUI

Register setup time 2.5 - 2.5 - 1.5 - 2.5 - 3.5 - ns

T

HI

Register hold time 1.0 - 1.0 - 3.0 - 3.5 - 4.5 - ns

T

COI

Register clock to output valid time - 0.5 - 0.5 - 0.5 - 0.5 - 0.5 ns

T

AOI

Register async. S/R to output delay - 6.0 - 6.0 - 6.5 - 7.0 - 8.0 ns

T

RAI

Register async. S/R recover before

clock

5.0 - 5.0 - 7.5 - 10.0 - 10.0 - ns

T

LOGI

Internal logic delay - 1.0 - 1.0 - 2.0 - 2.5 - 3.0 ns

T

LOGILP

Internal low power logic delay - 9.0 - 9.0 - 10.0 - 11.0 - 11.5 ns

Feedback Delays

T

F

FastCONNECT feedback delay - 6.0 - 6.0 - 8.0 - 9.5 - 11.0 ns

Time Adders

T

PTA

(1)

Incremental product term allocator

delay

- 0.8 - 0.8 - 1.0 - 1.0 - 1.0 ns

T

SLEW

Slew-rate limited delay - 3.5 - 3.5 - 4.0 - 4.5 - 5.0 ns

Notes:

1. T

PTA

is multiplied by the span of the function as defined in the XC9500 family data sheet.