©2014 Silicon Storage Technology, Inc. DS20005053B 04/14

7

4 Mbit (x16) Multi-Purpose Flash Plus

SST39VF401C / SST39VF402C / SST39LF401C / SST39LF402C

Data Sheet

Device Operation

Commands are used to initiate the memory operation functions of the device. Commands are written

to the device using standard microprocessor write sequences. A command is written by asserting WE#

low while keeping CE# low. The address bus is latched on the falling edge of WE# or CE#, whichever

occurs last. The data bus is latched on the rising edge of WE# or CE#, whichever occurs first.

The SST39VF401C/402C and SST39LF401C/402C also have the Auto Low Power mode which puts

the device in a near standby mode after data has been accessed with a valid Read operation. This

reduces the I

DD

active read current from typically 5 mA to typically 3 µA. The Auto Low Power mode

reduces the typical I

DD

active read current to the range of 2 mA/MHz of Read cycle time. The device

exits the Auto Low Power mode with any address transition or control signal transition used to initiate

another Read cycle, with no access time penalty. Note that the device does not enter Auto-Low Power

mode after power-up with CE# held steadily low, until the first address transition or CE# is driven high.

Read

The Read operation of the SST39VF401C/402C and SST39LF401C/402C is controlled by CE# and OE#,

both have to be low for the system to obtain data from the outputs. CE# is used for device selection.

When CE# is high, the chip is deselected and only standby power is consumed. OE# is the output con-

trol and is used to gate data from the output pins. The data bus is in high impedance state when either

CE# or OE# is high. Refer to the Read cycle timing diagram for further details (Figure 6).

Word-Program Operation

The SST39VF401C/402C and SST39LF401C/402C are programmed on a word-by-word basis. Before

programming, the sector where the word exists must be fully erased. The Program operation is accom-

plished in three steps. The first step is the three-byte load sequence for Software Data Protection. The

second step is to load word address and word data. During the Word-Program operation, the

addresses are latched on the falling edge of either CE# or WE#, whichever occurs last. The data is

latched on the rising edge of either CE# or WE#, whichever occurs first. The third step is the internal

Program operation which is initiated after the rising edge of the fourth WE# or CE#, whichever occurs

first. The Program operation, once initiated, will be completed within 10 µs. See Figures 7 and 8 for

WE# and CE# controlled Program operation timing diagrams and Figure 22 for flowchar ts. During the

Program operation, the only valid reads are Data# Polling and Toggle Bit. During the internal Program

operation, the host is free to perform additional tasks. Any commands issued during the internal Pro-

gram operation are ignored. During the command sequence, WP# should be statically held high or low.

Sector/Block-Erase Operation

The Sector- (or Block-) Erase operation allows the system to erase the device on a sector-by-sector (or

block-by-block) basis. The SST39VF401C/402C and SST39LF401C/402C offer both Sector-Erase and

Block-Erase mode.

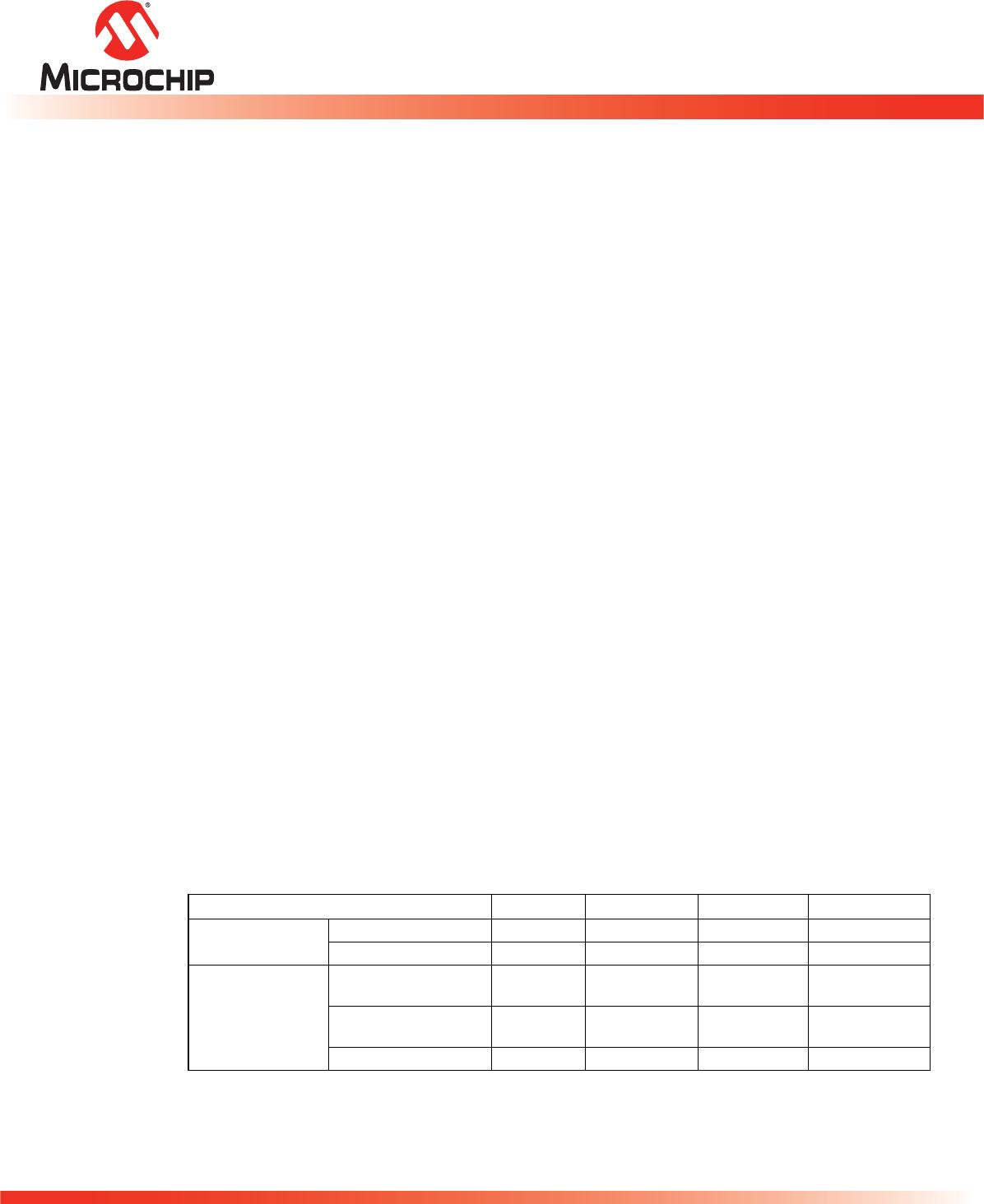

The sector architecture is based on a uniform sector size of 2 KWord. The Block-Erase mode is based

on non-uniform block sizes—seven 32 KWord, one 16 KWord, two 4 KWord, and one 8 KWord blocks.

See Figure 2 for top and bottom boot device block addresses. The Sector-Erase operation is initiated

by executing a six-byte command sequence with Sector-Erase command (50H) and sector address

(SA) in the last bus cycle. The Block-Erase operation is initiated by executing a six-byte command

sequence with Block-Erase command (30H) and block address (BA) in the last bus cycle. The sector

or block address is latched on the falling edge of the sixth WE# pulse, while the command (30H or

50H) is latched on the rising edge of the sixth WE# pulse. The internal Erase operation begins after the