©2014 Silicon Storage Technology, Inc. DS20005053B 04/14

16

4 Mbit (x16) Multi-Purpose Flash Plus

SST39VF401C / SST39VF402C / SST39LF401C / SST39LF402C

Data Sheet

Electrical Specifications

Absolute Maximum Stress Ratings (Applied conditions greater than those listed under “Absolute

Maximum Stress Ratings” may cause permanent damage to the device. This is a stress rating only and

functional operation of the device at these conditions or conditions greater than those defined in the

operational sections of this data sheet is not implied. Exposure to absolute maximum stress rating con-

ditions may affect device reliability.)

Temperature Under Bias .............................................. -55°C to +125°C

Storage Temperature ................................................ -65°C to +150°C

D. C. Voltage on Any Pin to Ground Potential .............................-0.5V to V

DD

+0.5V

Transient Voltage (<20 ns) on Any Pin to Ground Potential ..................-2.0V to V

DD

+2.0V

Voltage on A

9

Pin to Ground Potential .....................................-0.5V to 13.2V

Package Power Dissipation Capability (T

A

= 25°C) ................................... 1.0W

Surface Mount Solder Reflow ...................................... 260°C for 10 seconds

Output Short Circuit Current

1

.................................................. 50mA

1. Outputs shorted for no more than one second. No more than one output shorted at a time.

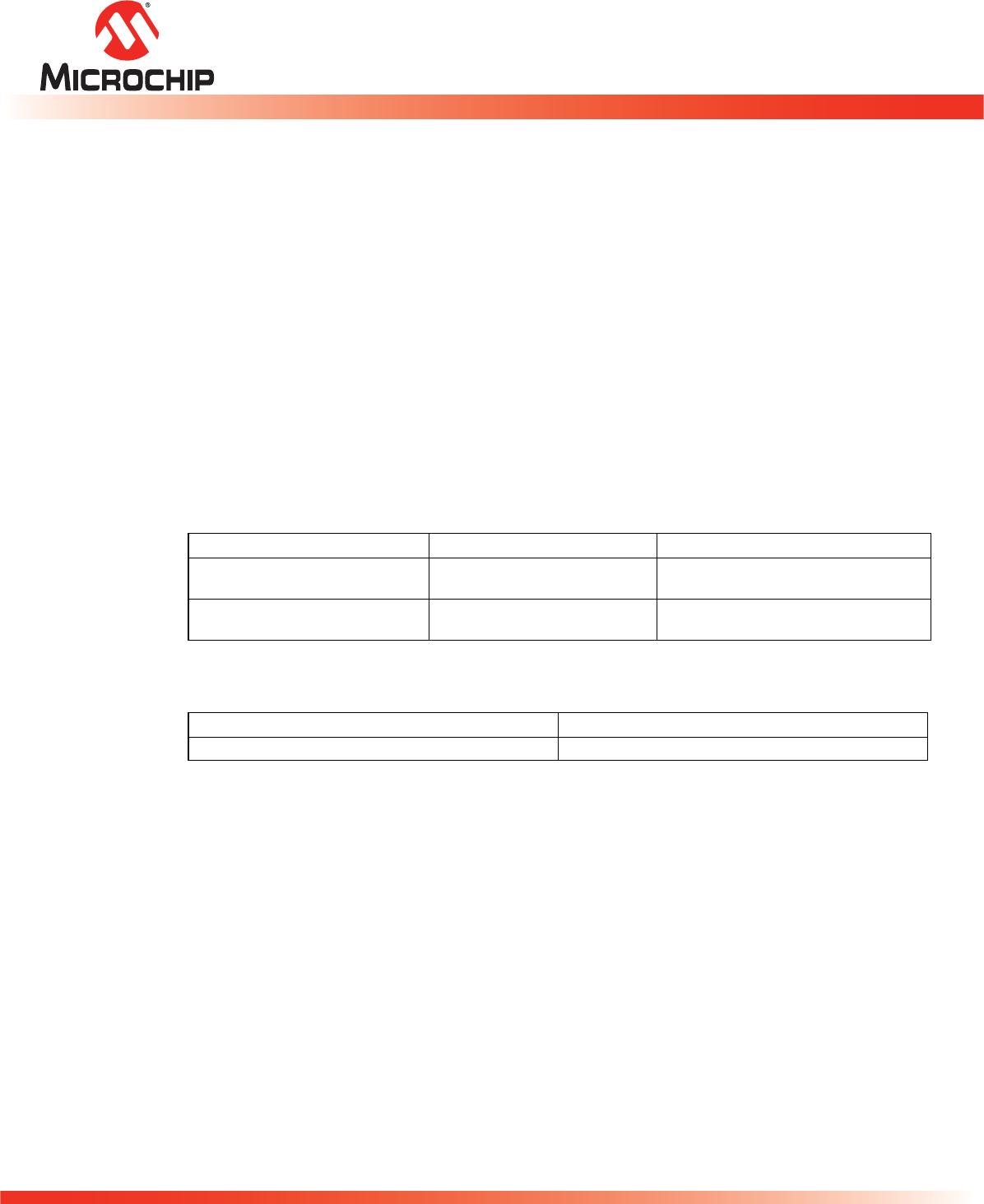

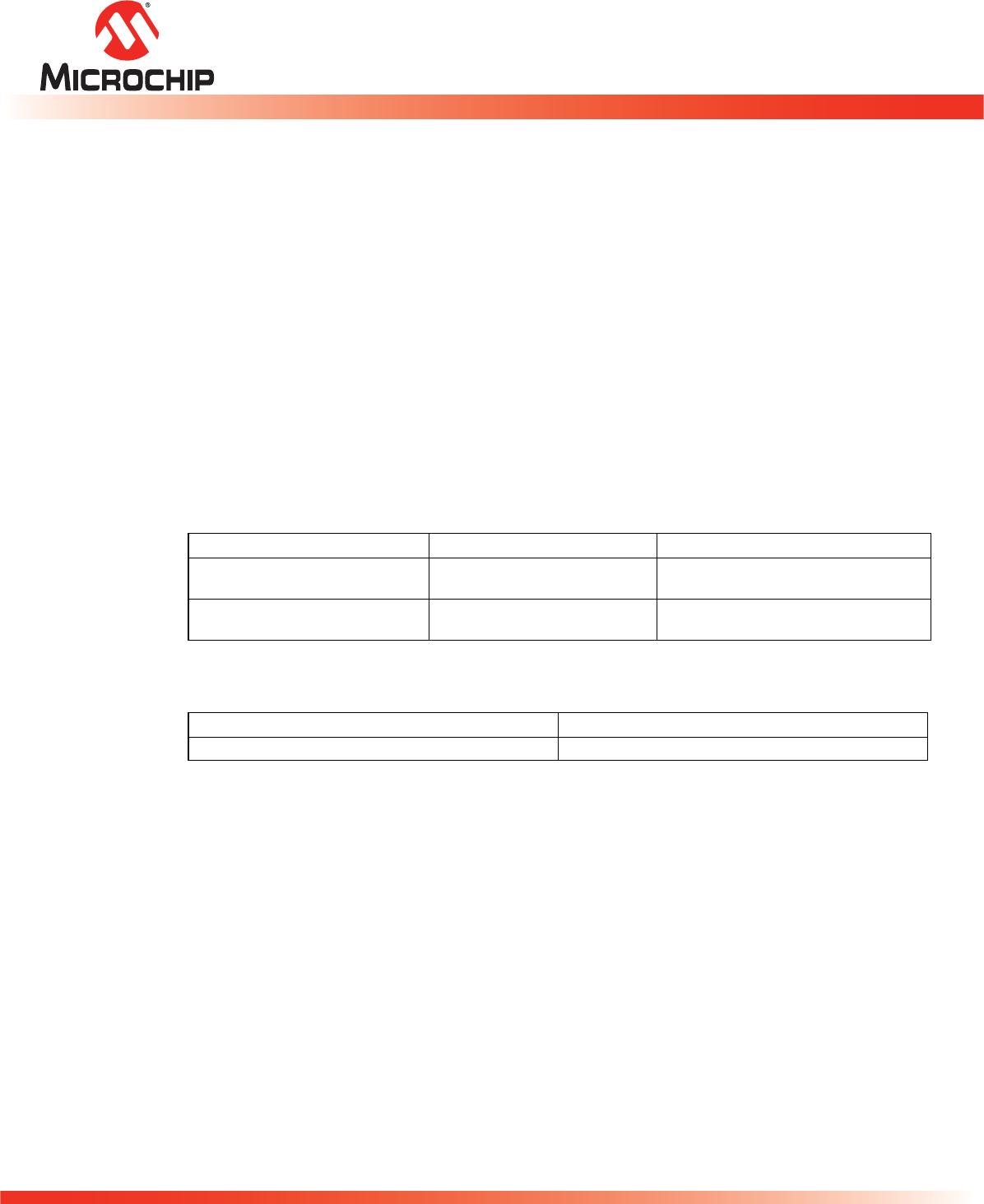

Table 11: Operating Range

Range Ambient Temp V

DD

Commercial 0°C to +70°C 2.7-3.6V for SST39VF401C/402C or

3.0-3.6V for SST39LF401C/402C

Industrial -40°C to +85°C 2.7-3.6V for SST39VF401C/402C or

3.0-3.6V for SST39LF401C/402C

T11.0 25053

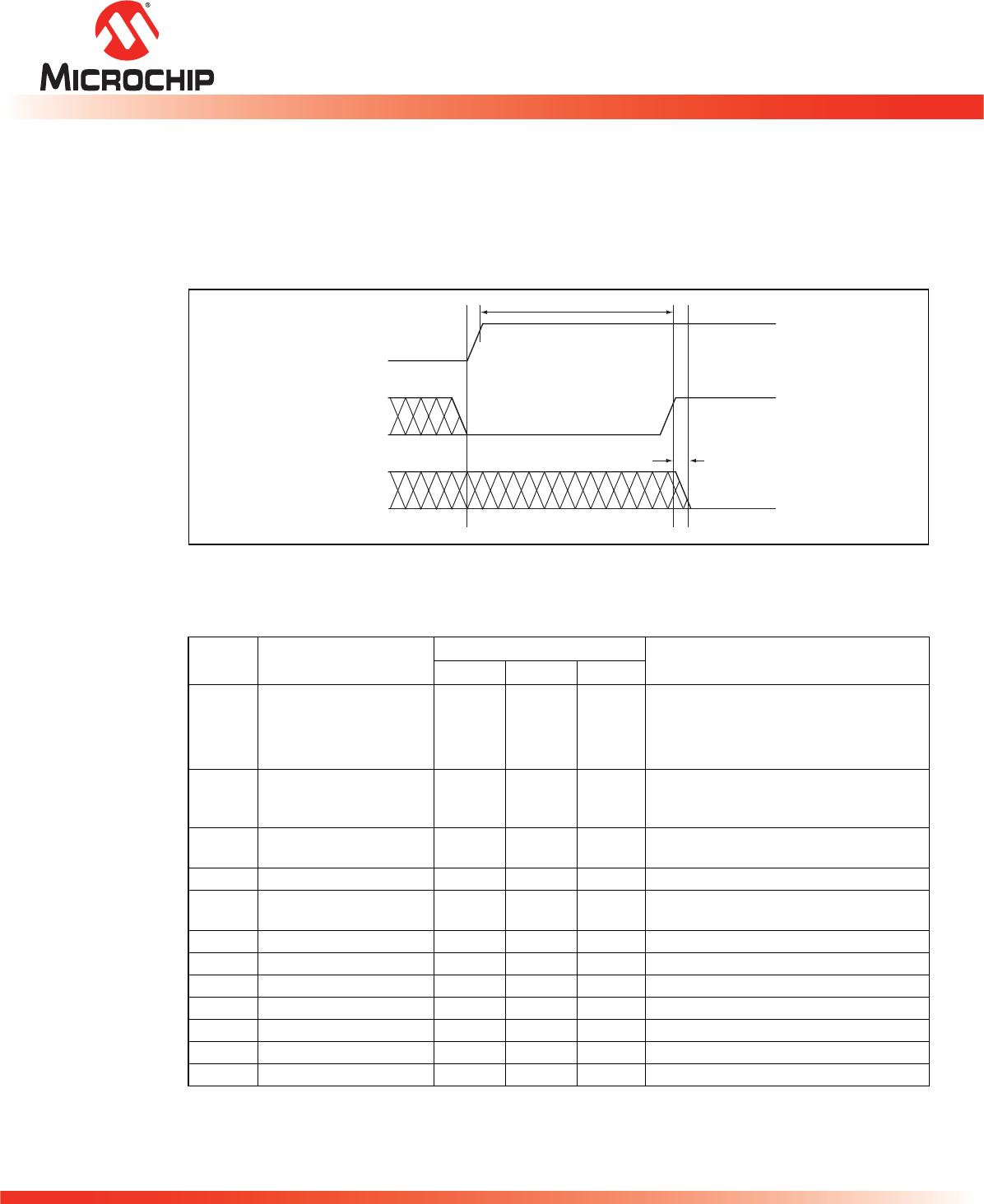

Table 12: AC Conditions of Test

1

1. See Figures 20 and 21

Input Rise/Fall Time Output Load

5ns C

L

=30pF

T12.1 25053