Data Sheet ADuM6132

APPLICATIONS INFORMATION

TYPICAL APPLICATION USAGE

The architecture of the ADuM6132 is ideal for motor drive and

inverter applications where the low-side channels are common

to the controller. This arrangement requires only two isolation

regions in a package. All the isolated signals and the isolated

power are grouped on one side of the package to maintain full

package creepage and clearance. The low-side driver, as well as the

control signals, share a common reference and are also grouped.

To maximize the effectiveness of external bypass capacitors, the

isoPower dc-to-dc converter is not internally tied to the data

channels, and should be treated as a completely independent

subsystem, except for a UVLO function (see the Undervoltage

Lockout section). This means that power must be applied to V

DD

to operate the dc-to-dc converter. Power must also be applied to

V

DDL

and V

DDB

to operate the data input and the Channel B

driver output. On the secondary side, the power generated at

the V

ISO

pin must be applied as an input power supply to the

V

DDA

pin. GND

ISO

and GND

A

must also be connected.

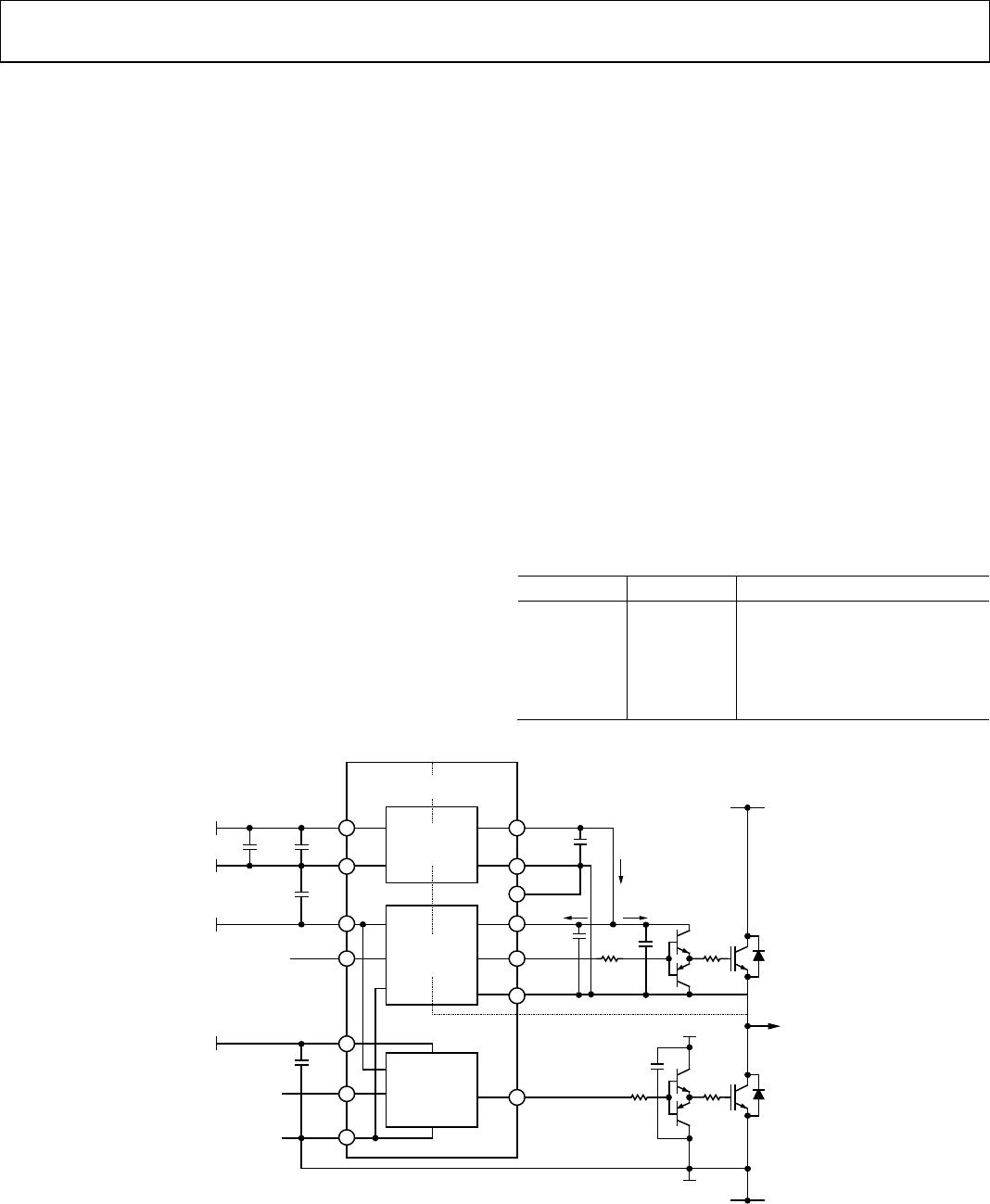

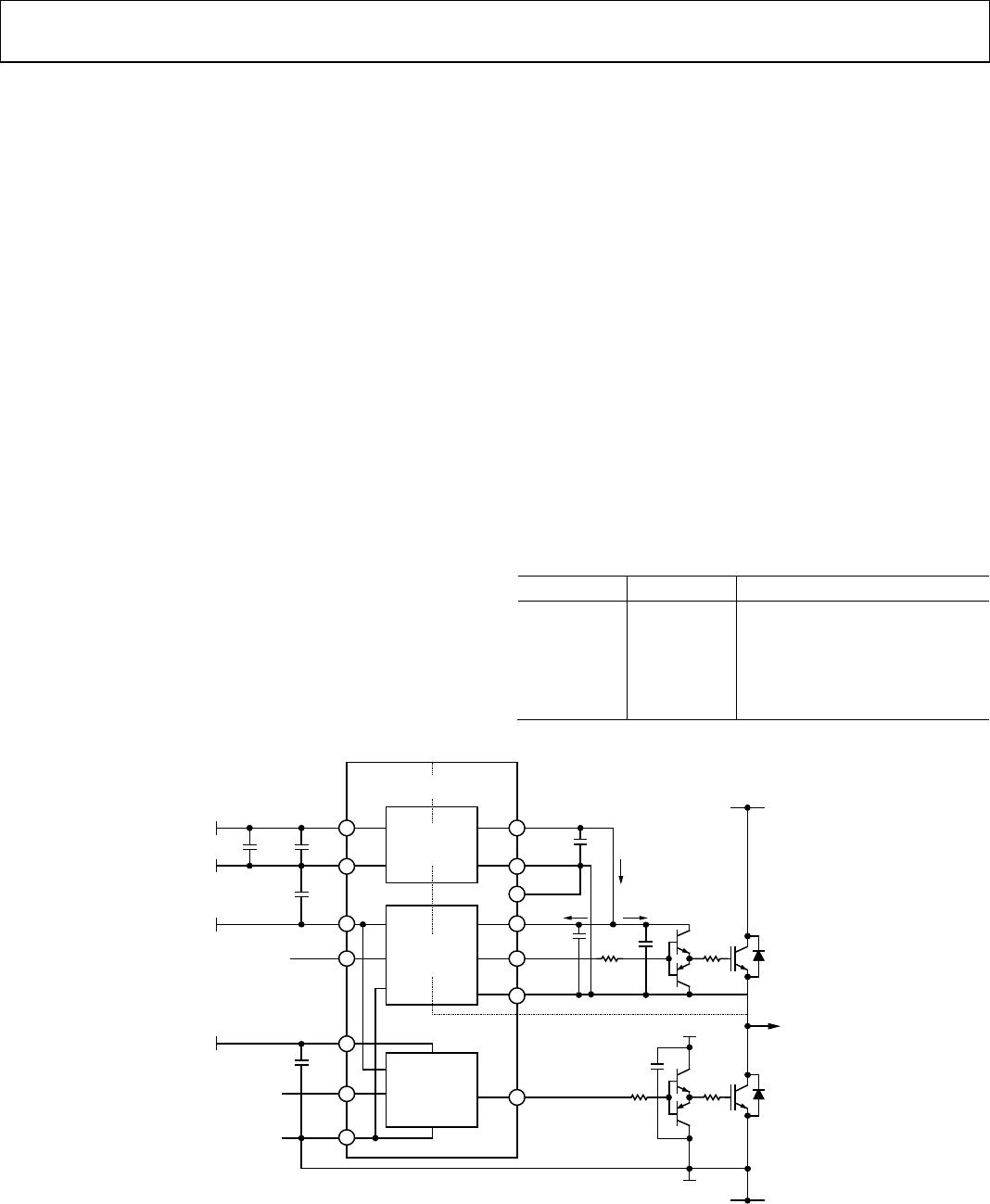

The ADuM6132 is intended for use in driving low gate

capacitance transistors (200 pF typically). Most high voltage

applications involve larger transistors than this. To accom-

modate these applications, users can implement a buffer

configuration with the ADuM6132, as shown in Figure 16. In

many cases, this buffer configuration is the least expensive

option to drive high capacitance devices and provides the

greatest amount of design flexibility. The precise buffer/high

voltage transistor combination can be selected to suit the

requirements of the application.

PCB LAYOUT

The ADuM6132 digital isolator with integrated 275 mW

isoPower dc-to-dc converter requires no external interface

circuitry for the logic interfaces. Power supply bypassing is

required at the input and output supply pins (see Figure 17).

The power supply section of the ADuM6132 uses a very high

oscillator frequency to efficiently pass power through its chip

scale transformers. In addition, the normal operation of the

data section of the iCoupler introduces switching transients

on the power supply pins. Bypass capacitors are required for

several operating frequencies. Noise suppression requires a low

ESR, high frequency capacitor; ripple suppression and proper

regulation require a large value capacitor in parallel (see Table 10).

The total lead length between both ends of the capacitor and

the input power supply pin should not exceed 20 mm.

Table 10. Recommended Bypass Capacitors

Supply Pins Bypass Capacitors

V

DD

1, 2 0.1 μF, 10 μF

V

DDB

7, 8 0.1 μF

V

DDL

2, 3 0.1 μF

V

DDA

13, 14 0.1 μF

V

ISO

15, 16 0.1 μF, 10 μF

+5V

+15V

V

DD

GND

V

ISO

GND

ISO

1

2

V

DDL

3

V

IA

4

V

DDB

7

GND

8

16

15

GND

ISO

9

GND

A

14

V

DDA

13

V

OA

12

ISOLATED

DC-TO-DC

CONVERTER

ISOLATED

GATE

DRIVE

NONISOLATED

GATE

DRIVE

ADuM6132

0.1µF

0.1µF

0.1µF

10µF

+5V

GND

V

IB

5

R

G

I

DDA

I

AVAIL

I

ISO

R

BUF

C

BUF

0.1µF

BUFFER

BUFFER

V

DC+

V

DC–

R

G

R

BUF

C

BUF

+15V

GND

V

OB

6

07393-016

0.1µF

Figure 16. Typical Application Circuit

Rev. B | Page 11 of 16