ADuM6132 Data Sheet

In applications involving high common-mode transients, care

should be taken to ensure that board capacitive coupling across

the isolation barrier is minimized. Furthermore, the board

layout should be designed so that any coupling that does occur

affects all pins on a given component side equally. Failure to

ensure this may cause voltage differentials between pins that

exceed the absolute maximum ratings of the device (see Table 7),

leading to latch-up or permanent damage.

V

DD

GND

V

DDL

V

IA

V

ISO

GND

ISO

GND

A

V

DDA

V

IB

V

OA

V

OB

NC

V

DDB

NC

GND GND

ISO

07393-017

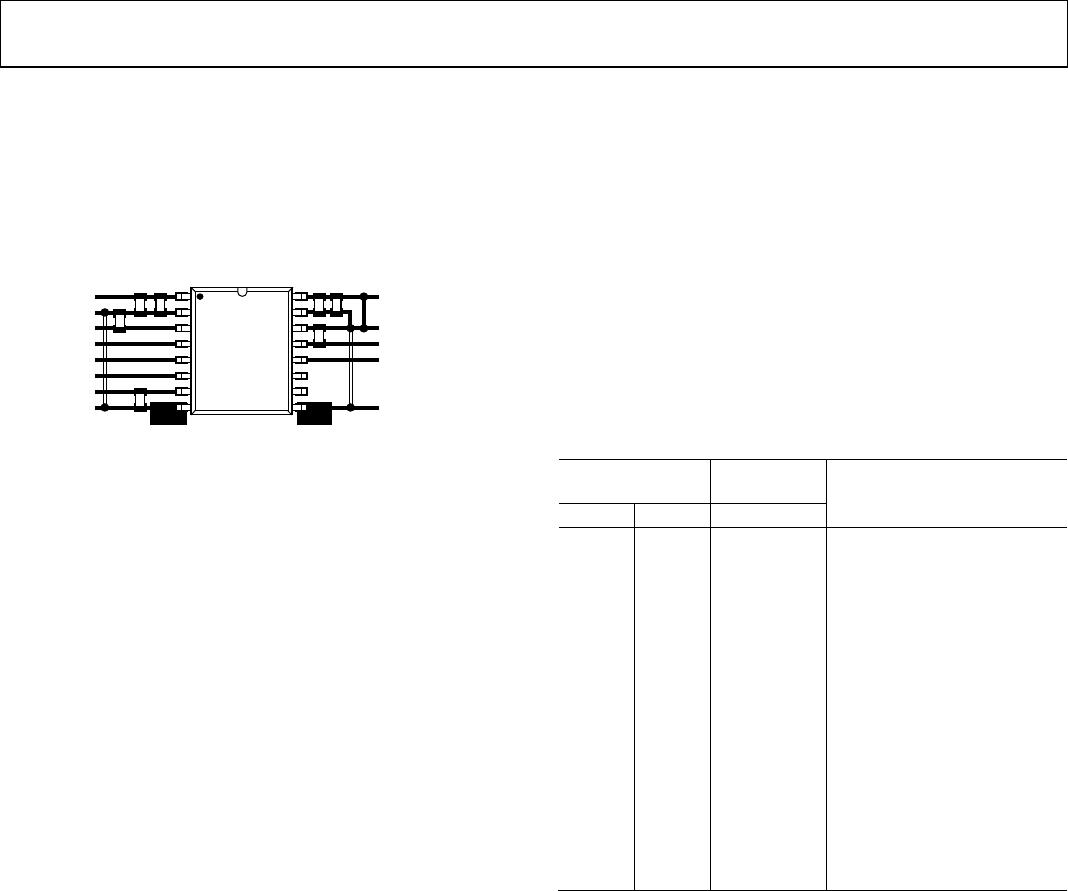

Figure 17. Recommended PCB Layout

The ADuM6132 is a power device that dissipates approximately

1 W of power when fully loaded and running at maximum speed.

Because it is not possible to apply a heat sink to an isolation

device, the device depends primarily on heat dissipation into

the PCB through the GND pins. If the device will be used at

high ambient temperatures, provide a thermal path from the

GND pins to the PCB ground plane.

The board layout in Figure 17 shows enlarged pads for Pin 8

(GND) and Pin 9 (GND

ISO

). Multiple vias should be implemented

from the pad to the ground plane. This layout significantly reduces

the temperatures inside the chip. The dimensions of the expanded

pads are left to the discretion of the designer and the available

board space. See the AN-0971 Application Note for board

layout recommendations.

THERMAL ANALYSIS

The ADuM6132 consists of several internal die attached to

two lead frame paddles. For the purposes of thermal analysis,

the part is treated as a thermal unit with the highest junction

temperature determining θ

JA

, as shown in Ta ble 2 . The value of

θ

JA

is based on measurements taken with the part mounted on

a JEDEC standard 4-layer board with fine width traces and still

air. Under normal operating conditions, the ADuM6132 oper-

ates at full load across the full temperature range without derating

the output current. However, following the recommendations in

the PCB Layout section decreases the thermal resistance to the

PCB, allowing increased thermal margin at high ambient

temperatures.

Under V

ISO

output short-circuit conditions, as shown in

Figure 9, the package power dissipation quickly exceeds the safe

operating limit of 1.44 W for ambient temperatures up to 85°C.

At low input voltage, the power dissipation can approach 2 W.

Because internal compensation of the PWM makes low V

DD

a

worst-case condition, input voltage limiting is not an effective

strategy for protecting the ADuM6132 from output load fault

conditions. Therefore, the preferred protection methods, where

required, are either limiting ambient temperature to 60°C or the

use of a fuse.

UNDERVOLTAGE LOCKOUT

The ADuM6132 has undervoltage lockout (UVLO) circuits on

the V

DDL

, V

DDA

, and V

DDB

supplies. For each supply, the respective

UVLO circuit monitors the supply voltage and takes a predeter-

mined action based on whether the supply voltage is above or

below a given threshold. These thresholds are specified in Table 1.

In the recommended configuration shown in Figure 16, only

two independent supplies are controlled by the user: V

DDB

and

V

DDL

/V

DD

(V

DDL

= V

DD

in Figure 16). V

DDA

is supplied by the

internal dc-to-dc converter via the V

ISO

= V

DDA

external connec-

tion. Nevertheless, the V

DDA

UVLO functionality is included in

Table 11 to show how the V

OA

output behaves when the internal

dc-to-dc converter powers on and off.

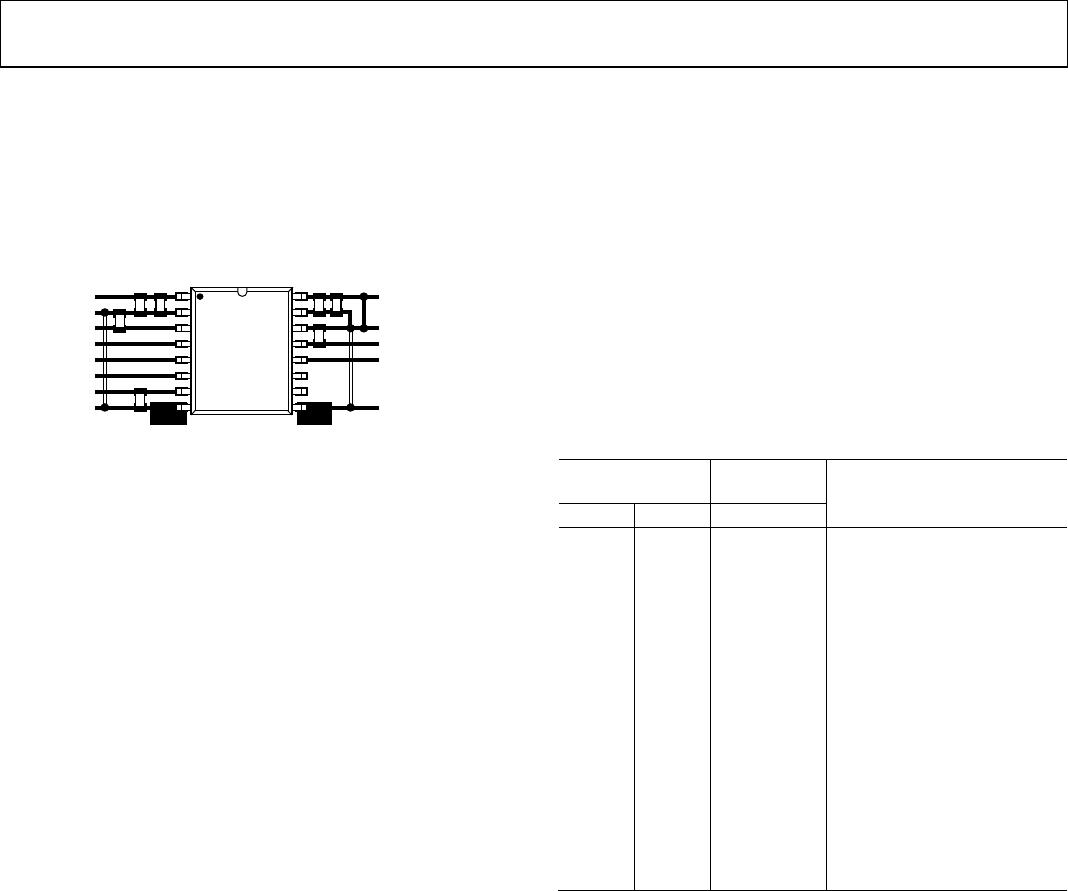

Table 11. Undervoltage Lockout Functionality

1

User-Provided

Supplies

V

ISO

Powered

Supply

V

DDL

V

DDB

V

DDA

Effect

H H H Normal operation.

Internal dc-to-dc converter is

active.

V

OA

/V

OB

output logic states

match V

IA

/V

IB

input logic states.

H H L Internal dc-to-dc converter is

active but V

ISO

is below UVLO

threshold.

V

OA

output is driven low.

V

OB

output operates normally.

X L X Internal dc-to-dc converter is

turned off (V

ISO

= 0 V).

V

OA

output is driven low.

V

OB

output is driven low.

L X X Internal dc-to-dc converter is

turned off (V

ISO

= 0 V).

V

OA

output is driven low.

V

OB

output is driven low.

1

H: supply voltage > UVLO threshold; L: supply voltage < UVLO threshold;

X: supply voltage level is irrelevant.

When all three supplies are above their respective UVLO

thresholds, the ADuM6132 operates normally. The internal

dc-to-dc converter is active, and both outputs operate as

determined by their respective input logic signals. If either of

the user-provided supplies is below its UVLO threshold, the

ADuM6132 is put into a disabled mode. In this mode, the

internal dc-to-dc converter is turned off and both outputs are

driven low.

The V

OB

output is driven low by either the V

DDL

or V

DDB

UVLO circuit (whichever is below its threshold). The V

OA

output is driven low when the internal dc-to-dc converter is

turned off. The V

ISO

supply voltage drops to 0 V, causing V

DDA

to drop also because V

ISO

and V

DDA

are externally connected.

When V

DDA

is below its UVLO threshold, the V

DDA

UVLO

circuit drives V

OA

low.

Rev. B | Page 12 of 16