Si8220/21

Rev. 1.2 13

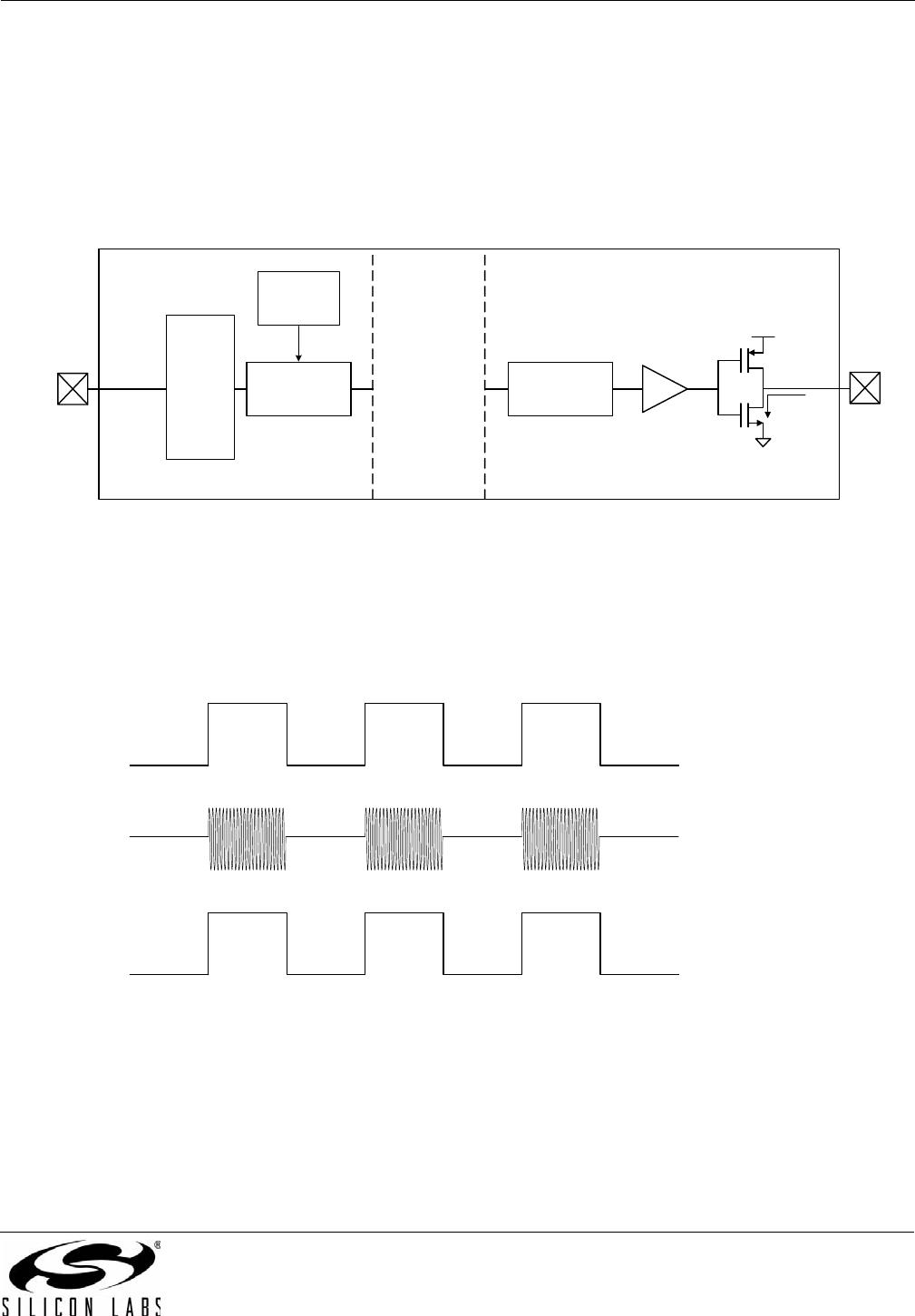

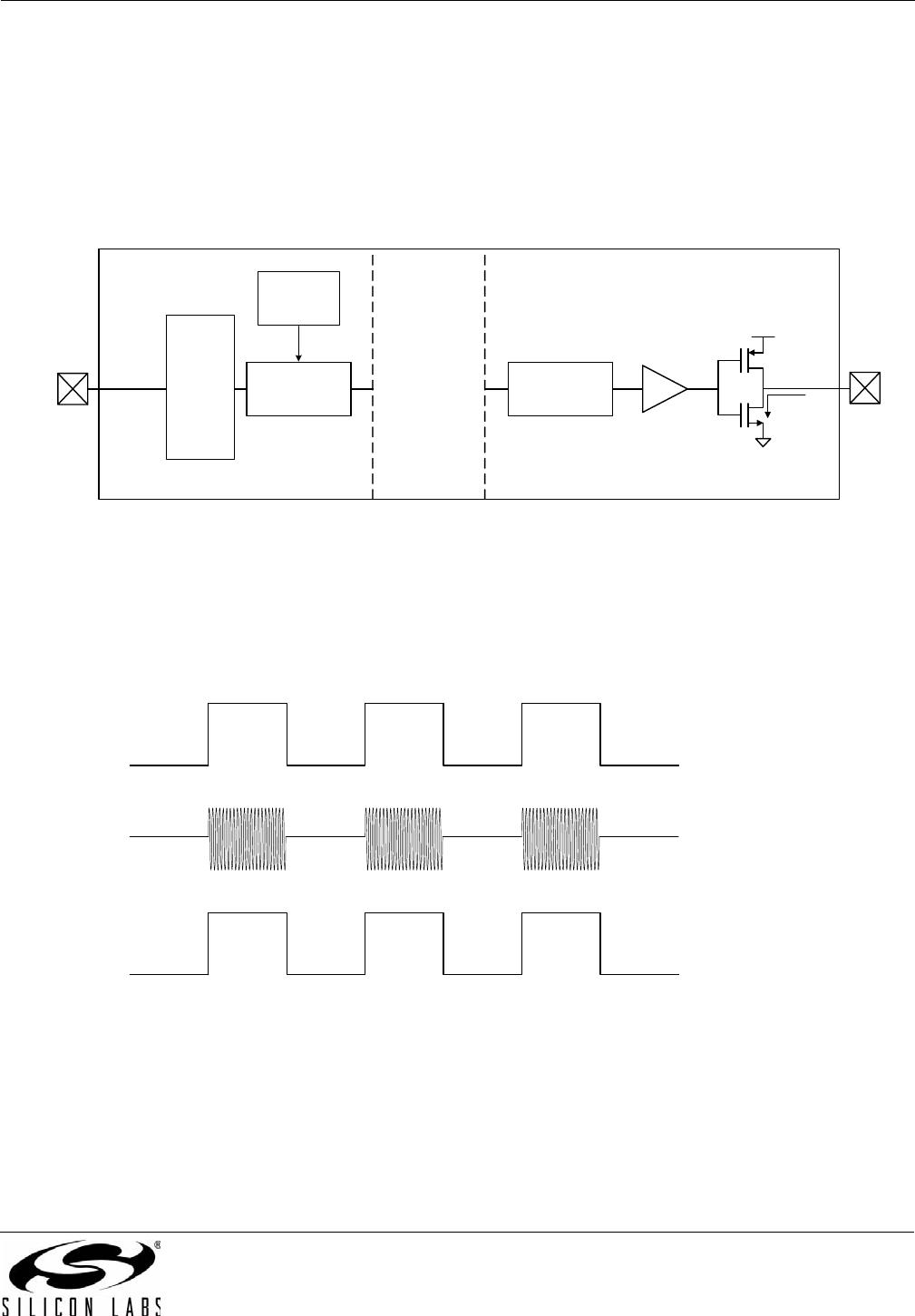

4. Functional Description

4.1. Theory of Operation

The Si8220/21 is a functional upgrade for popular opto-isolated drivers, such as the Avago HPCL-3120, HPCL-

0302, Toshiba TLP350, and others. The operation of an Si8220/21 channel is analogous to that of an opto coupler,

except an RF carrier is modulated instead of light. This simple architecture provides a robust isolated data path and

requires no special considerations or initialization at start-up. A simplified block diagram for the Si8220/21 is shown

in Figure 6.

Figure 6. Simplified Channel Diagram

A channel consists of an RF Transmitter and RF Receiver separated by a semiconductor-based isolation barrier.

Referring to the Transmitter, input A modulates the carrier provided by an RF oscillator using on/off keying. The

Receiver contains a demodulator that decodes the input state according to its RF energy content and applies the

result to output B via the output driver. This RF on/off keying scheme is superior to pulse code schemes as it

provides best-in-class noise immunity, low power consumption, and better immunity to magnetic fields. See

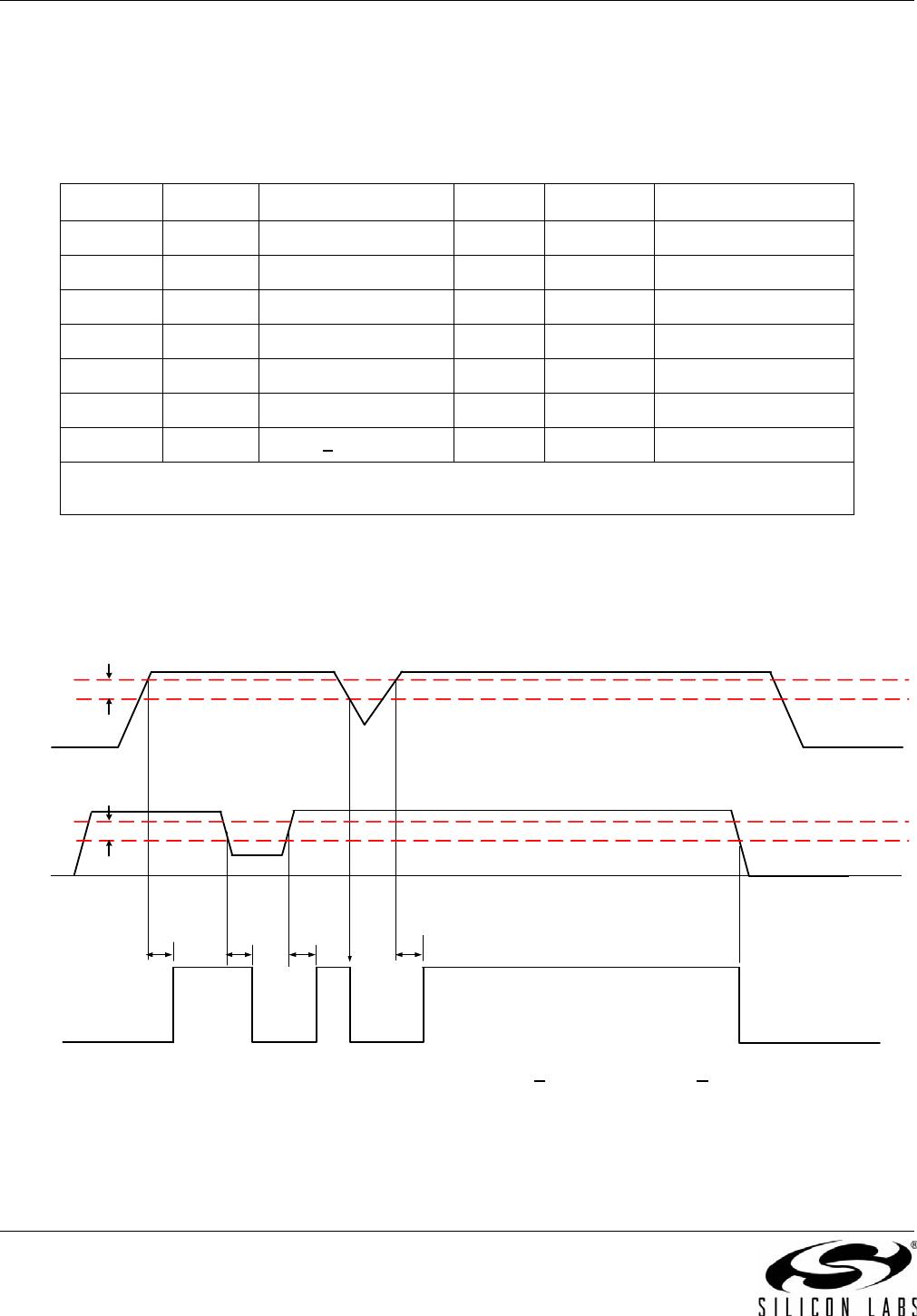

Figure 7 for more details.

Figure 7. Modulation Scheme

RF

OSCILLATOR

MODULATOR DEMODULATOR

A

B

Semiconductor-

Based Isolation

Barrier

Transmitter

Receiver

LED

Emulator

0.5 to 2.5 A

peak

Gnd

V

DD

Input Signal

Output Signal

Modulation Signal