Si8220/21

22 Rev. 1.2

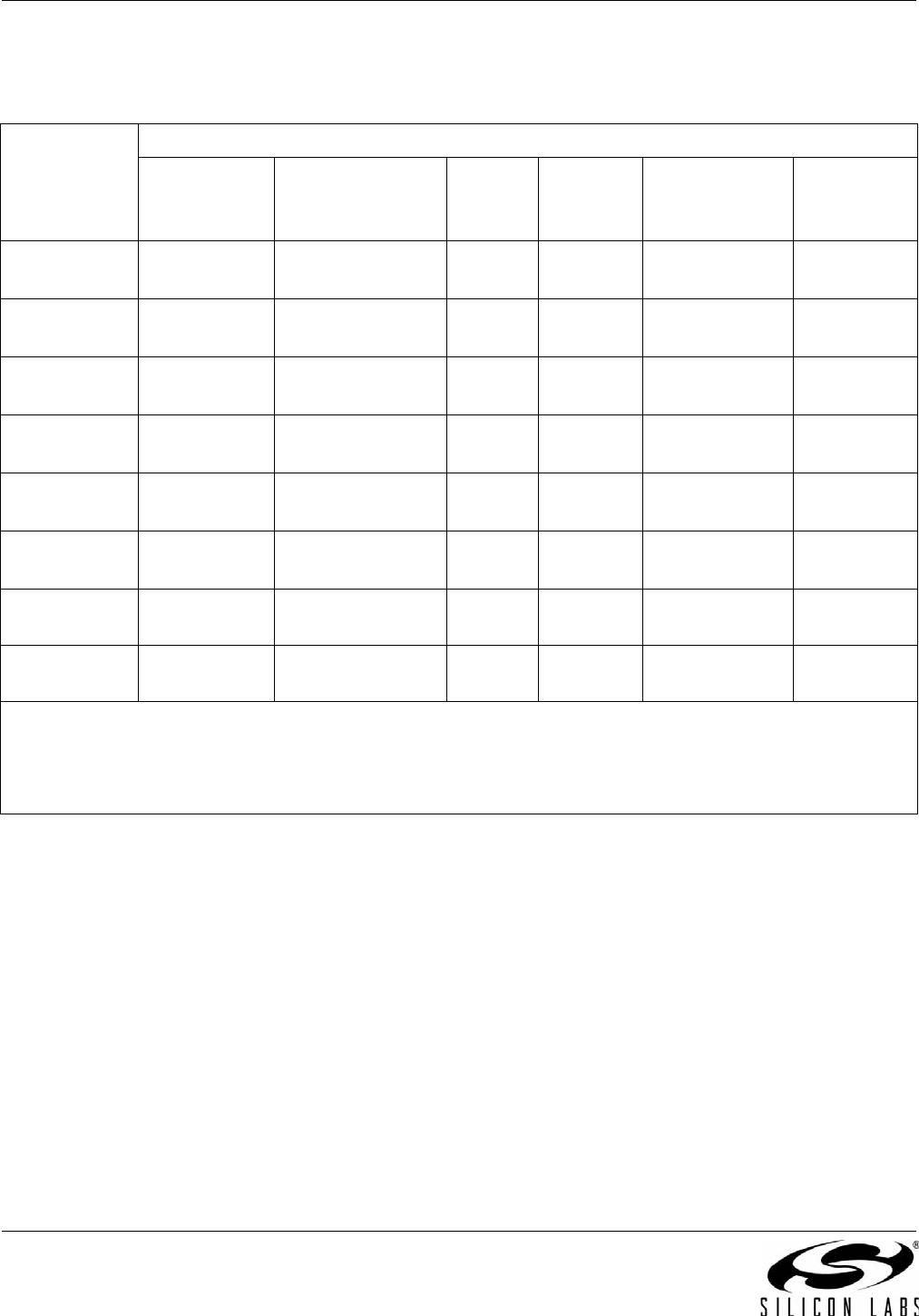

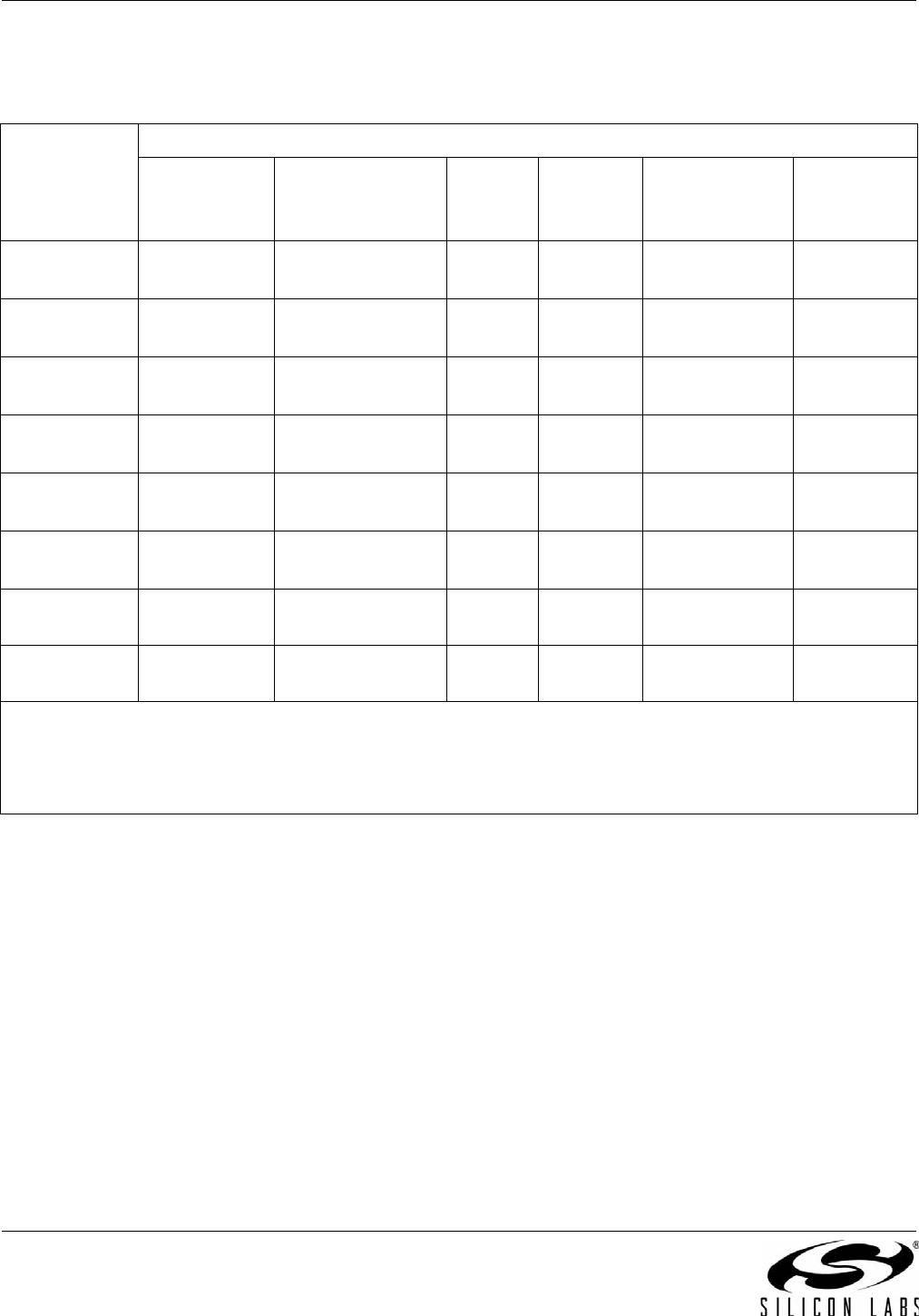

9. Ordering Guide

Table 14. Si8220/21 Ordering Guide*

New Ordering

Part Number

(OPN)

Ordering Options

Input

Configuration

Peak Output

Current

(Cross Reference)

UVLO

Voltage

Insulation

Rating

Temp Range Pkg Type

Si8220BB-A-IS Opto input 2.5 A

(HCPL-3120)

8V

default

2.5 kVrms –40 to +125 °C SOIC-8

Si8220CB-A-IS Opto input 2.5 A

(HCPL-3120)

10 V 2.5 kVrms –40 to +125 °C SOIC-8

Si8220DB-A-IS Opto input 2.5 A

(HCPL-3120)

12.5 V 2.5 kVrms –40 to +125 °C SOIC-8

Si8220BD-A-IS Opto input 2.5 A

(HCPL-3120)

8V

default

5.0 kVrms –40 to +125 °C WB SOIC-16

Si8220CD-A-IS Opto input 2.5 A

(HCPL-3120)

10 V 5.0 kVrms –40 to +125 °C WB SOIC-16

Si8220DD-A-IS Opto input 2.5 A

(HCPL-3120)

12.5 V 5.0 kVrms –40 to +125 °C WB SOIC-16

Si8221CC-A-IS Opto input 0.5 A

(HCPL-0302)

10 V 3.75 kVrms –40 to +125 °C SOIC-8

Si8221DC-A-IS Opto input 0.5 A

(HCPL-0302)

12.5 V 3.75 kVrms –40 to +125 °C SOIC-8

*Note: All packages are RoHS-compliant with peak reflow temperatures of 260 °C according to the JEDEC industry standard

classifications and peak solder temperatures.

Moisture sensitivity level is MSL2A for wide-body SOIC-16 packages.

Moisture sensitivity level is MSL2A for narrow-body SOIC-8 packages.

“Si” and “SI” are used interchangeably.