MAX1620/MAX1621

Digitally Adjustable LCD Bias Supplies

______________________________________________________________________________________ 13

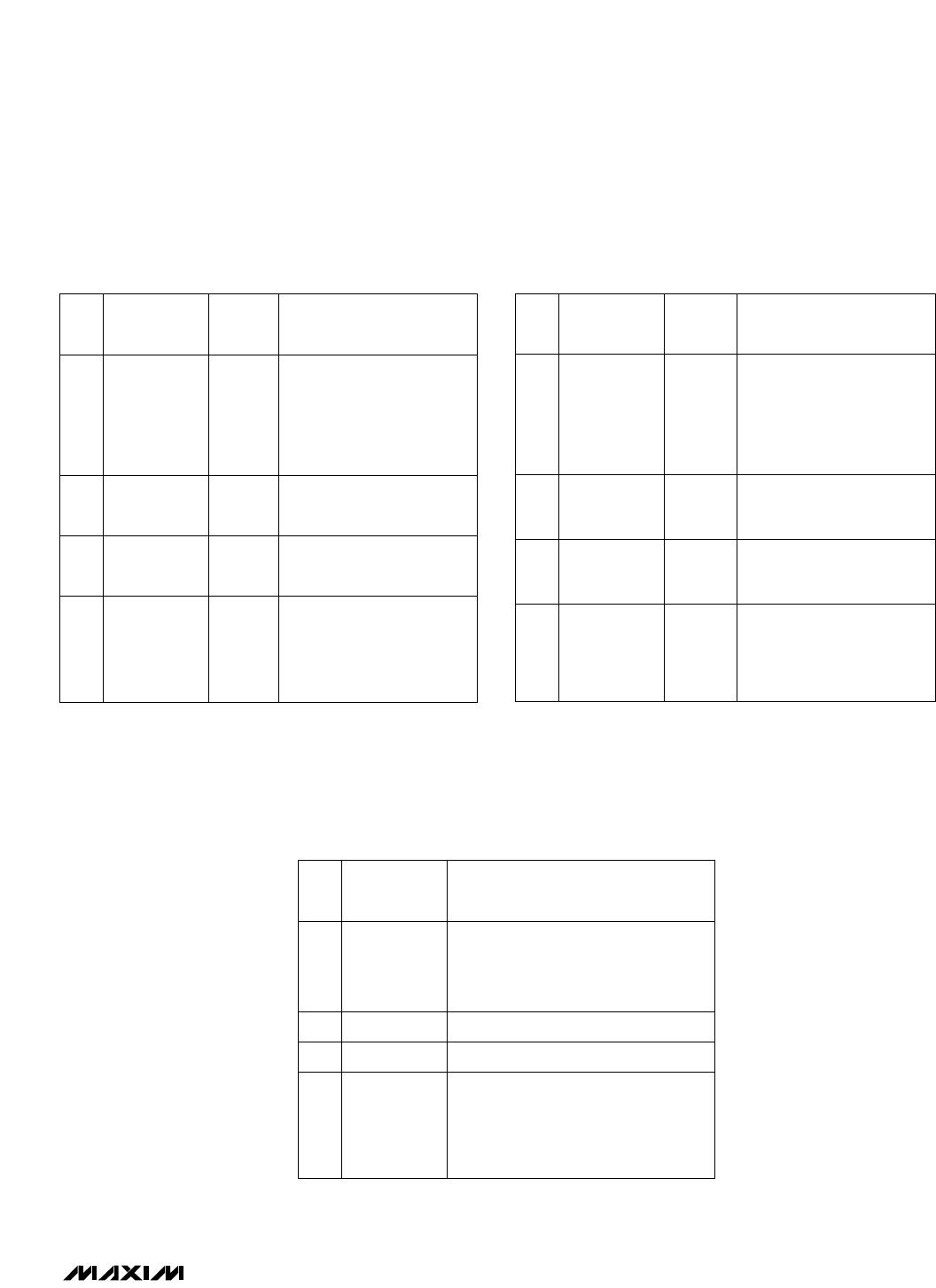

Reserved for future use.

DAC Register Data

Reserved for future use.

If the voltage applied to POK is

greater than 0.992V and the

MAX1621 is not shut down, this bit

returns 1; otherwise, it returns 0.

DESCRIPTION

—5

D4 (MSB)

D3

D2

D1

D0

4

3

2

1

0

—6

POK7

NAMEBIT

With SUS = high,

1 = LCD on, and

0 = LCD off.

DAC Input Data

With SUS = high,

1 = operating, and

0 = shutdown.

Register Select. A one in

this bit writes the next two

bits into the OPR register

and the remaining five bits

into the DAC register

(Figure 7).

DESCRIPTION

1OPR-LCDON5

1

0

0

0

0

D4 (MSB)

D3

D2

D1

D0

4

3

2

1

0

1

OPR-SHDN

6

—REGSEL7

NAME

POR

STATE*

BIT

Table 2. MAX1621 Configuration Byte

with REGSEL = 1 (write to OPR register)

*

Initial register state after power-up.

Table 3. MAX1621 Status Bits

With SUS = low,

1 = LCD on, and

0 = LCD off.

DAC Input Data

With SUS = low,

1 = operating, and

0 = shutdown.

Register Select. A zero in

this bit writes the next two

bits into the SUS register

and the remaining five bits

into the DAC register

(Figure 7).

DESCRIPTION

0

SUS-LCDON

5

1

0

0

0

0

D4 (MSB)

D3

D2

D1

D0

4

3

2

1

0

0

SUS-SHDN

6

—REGSEL7

POR

STATE*

BIT NAME

*

Initial register state after power-up.

Table 1. MAX1621 Configuration Byte

with REGSEL = 0 (write to SUS register)