X28HC64

3

FN8109.4

June 27, 2016

Submit Document Feedback

Device Operation

Read

Read operations are initiated by both OE and CE LOW. The read

operation is terminated by either CE

or OE returning HIGH. This

two line control architecture eliminates bus contention in a

system environment. The data bus will be in a high impedance

state when either OE

or CE is HIGH.

Write

Write operations are initiated when both CE and WE are LOW and

OE is HIGH. The X28HC64 supports both a CE and WE controlled

write cycle. That is, the address is latched by the falling edge of

either CE

or WE, whichever occurs last. Similarly, the data is

latched internally by the rising edge of either CE or WE, whichever

occurs first. A byte write operation, once initiated, will

automatically continue to completion, typically within 2ms.

Page Write Operation

The page write feature of the X28HC64 allows the entire memory

to be written in 0.25 seconds. Page write allows two to sixty-four

bytes of data to be consecutively written to the X28HC64 prior to

the commencement of the internal programming cycle. The host

can fetch data from another device within the system during a

page write operation (change the source address), but the page

address (A

6

through A

12

) for each subsequent valid write cycle to

the part during this operation must be the same as the initial page

address.

The page write mode can be initiated during any write operation.

Following the initial byte write cycle, the host can write an

additional one to sixty-three bytes in the same manner. Each

successive byte load cycle, started by the WE

HIGH to LOW

transition, must begin within 100µs of the falling edge of the

preceding WE

. If a subsequent WE HIGH to LOW transition is not

detected within 100µs, the internal automatic programming

cycle will commence. There is no page write window limitation.

Effectively the page write window is infinitely wide, so long as the

host continues to access the device within the byte load cycle

time of 100µs.

Write Operation Status Bits

The X28HC64 provides the user two write operation status bits.

These can be used to optimize a system write cycle time. The

status bits are mapped onto the I/O bus as shown in Figure 2.

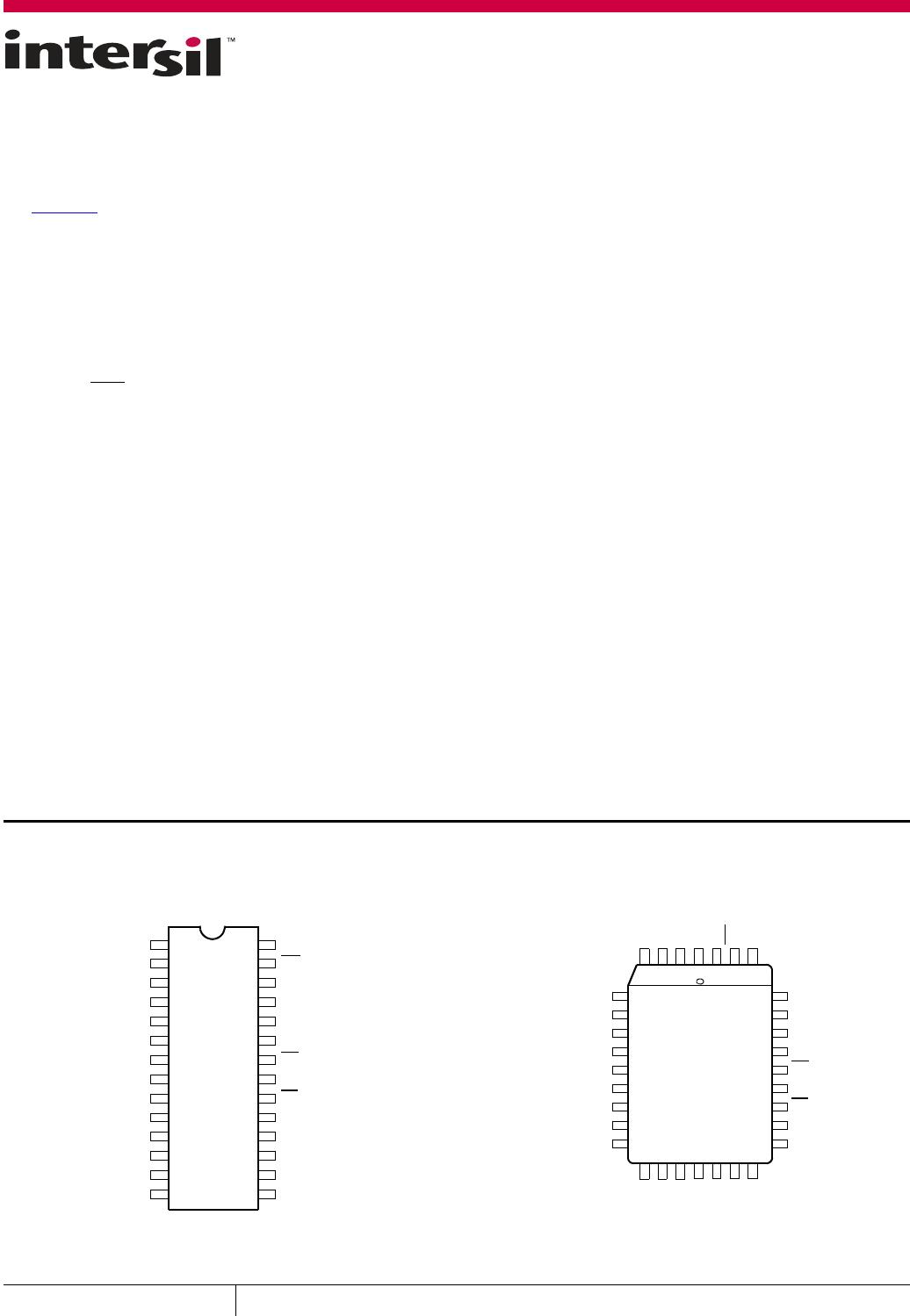

Pin Descriptions

SYMBOL DESCRIPTION

A

0

-A

12

Address Inputs. The Address inputs

select an 8-bit memory location

during a read or write operation.

I/O

0

-I/O

7

Data Input/Output. Data is written

to or read from the X28HC64

through the I/O pins.

WE

Write Enable. The Write Enable

input controls the writing of data to

the X28HC64.

CE

Chip Enable. The Chip Enable input

must be LOW to enable all

read/write operations. When CE is

HIGH, power consumption is

reduced.

OE

Output Enable. The Output Enable

input controls the data output

buffers and is used to initiate read

operations.

V

CC

+5V

V

SS

Ground

NC No Connect

Block Diagram

FIGURE 1. BLOCK DIAGRAM

X BUFFERS

LATCHES AND

DECODER

I/O BUFFERS

AND LATCHES

Y BUFFERS

LATCHES

DECODER

CONTROL

LOGIC AND

TIMING

65,536-BIT

EEPROM

ARRAY

I/O

0

–I/O

7

DATA INPUTS/OUTPUTS

CE

OE

V

CC

V

SS

A

0

–A

12

WE

ADDRESS

INPUTS

AND

5TBDP 43210I/O

RESERVED

TOGGLE BIT

DATA

POLLING

FIGURE 2. STATUS BIT ASSIGNMENT