XC95288XL High Performance CPLD

4 www.xilinx.com DS055 (v2.1 April 3, 2007

1-800-255-7778 Product Specification

R

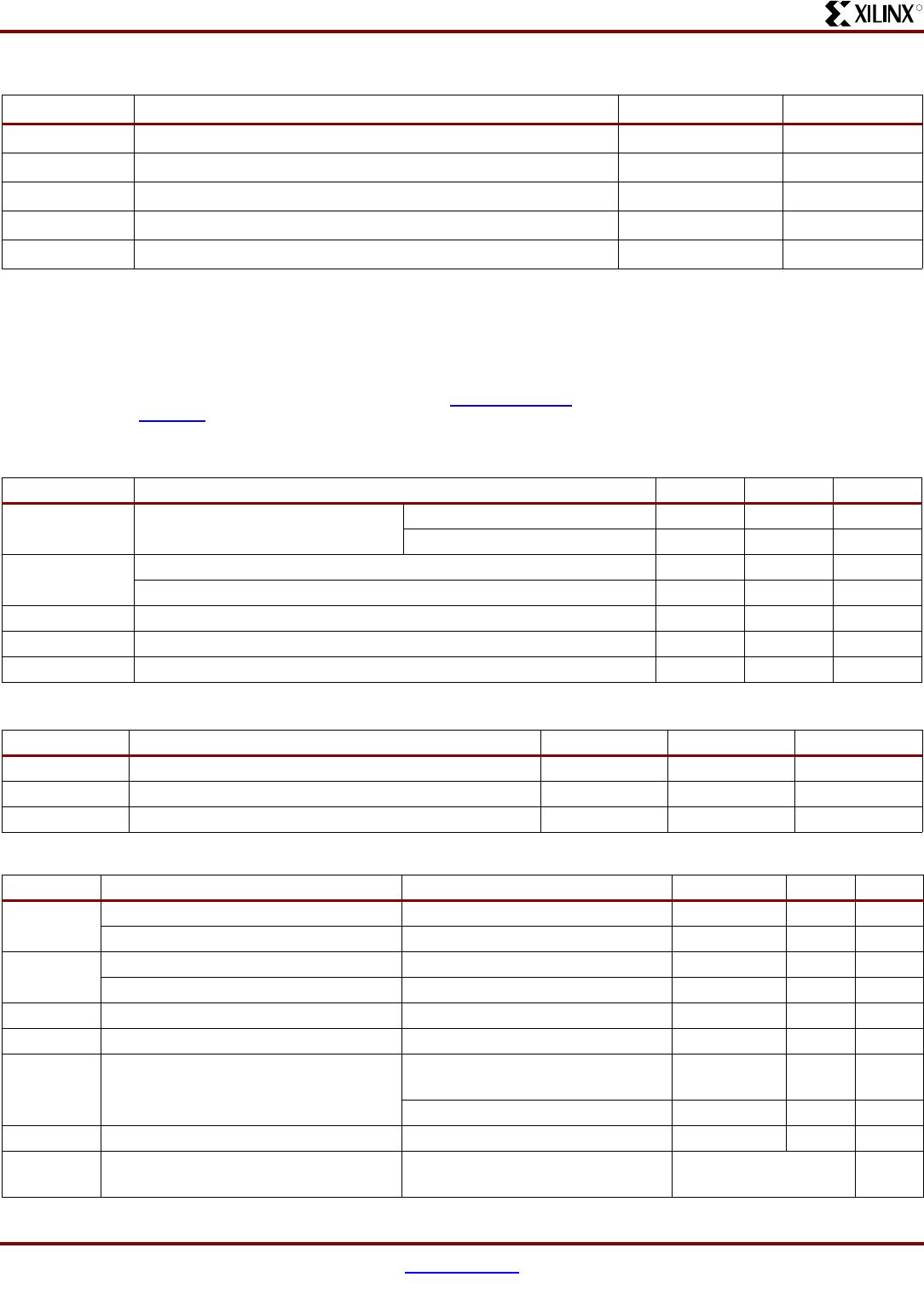

Absolute Maximum Ratings

(2)

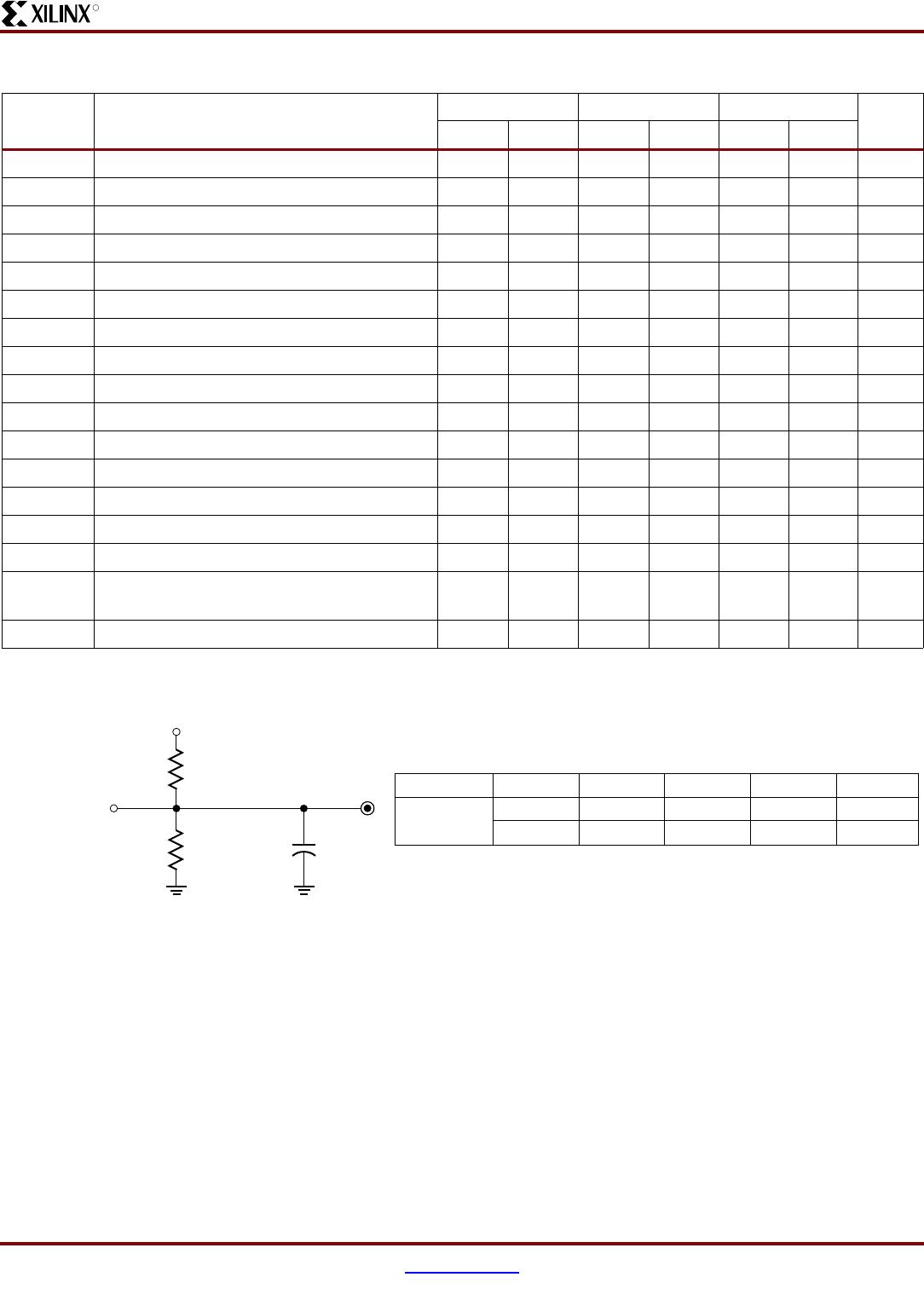

Recommended Operation Conditions

Quality and Reliability Characteristics

DC Characteristic Over Recommended Operating Conditions

Symbol Description Value Units

V

CC

Supply voltage relative to GND –0.5 to 4.0 V

V

IN

Input voltage relative to GND

(1)

–0.5 to 5.5 V

V

TS

Voltage applied to 3-state output

(1)

–0.5 to 5.5 V

T

STG

Storage temperature (ambient)

(3)

–65 to +150

o

C

T

J

Junction temperature +150

o

C

Notes:

1. Maximum DC undershoot below GND must be limited to either 0.5V or 10 mA, whichever is easier to achieve. During transitions, the

device pins may undershoot to –2.0V or overshoot to +7.0V, provided this over- or undershoot lasts less than 10 ns and with the

forcing current being limited to 200 mA. External I/O voltage may not exceed V

CCINT

by 4.0V.

2. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress

ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions

is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.

3. For soldering guidelines and thermal considerations, see the Device Packaging

information on the Xilinx website. For Pb-free

packages, see XAPP427.

Symbol Parameter Min Max Units

V

CCINT

Supply voltage for internal logic

and input buffers

Commercial T

A

= 0

o

C to 70

o

C3.0 3.6 V

Industrial T

A

= –40

o

C to +85

o

C3.0 3.6 V

V

CCIO

Supply voltage for output drivers for 3.3V operation 3.0 3.6 V

Supply voltage for output drivers for 2.5V operation 2.3 2.7 V

V

IL

Low-level input voltage 0 0.80 V

V

IH

High-level input voltage 2.0 5.5 V

V

O

Output voltage 0 V

CCIO

V

Symbol Parameter Min Max Units

T

DR

Data Retention 20 - Years

N

PE

Program/Erase Cycles (Endurance) 10,000 - Cycles

V

ESD

Electrostatic Discharge (ESD) 2,000 - Volts

Symbol Parameter Test Conditions Min Max Units

V

OH

Output high voltage for 3.3V outputs I

OH

= –4.0 mA 2.4 - V

Output high voltage for 2.5V outputs I

OH

= –500 μA90% V

CCIO

-V

V

OL

Output low voltage for 3.3V outputs I

OL

= 8.0 mA - 0.4 V

Output low voltage for 2.5V outputs I

OL

= 500 μA-0.4V

I

IL

Input leakage current V

CC

= Max; V

IN

= GND or V

CC

-±10μA

I

IH

I/O high-Z leakage current V

CC

= Max; V

IN

= GND or V

CC

-±10μA

I

IH

I/O high-Z leakage current V

CC

= Max; V

CCIO

= Max;

V

IN

= GND or 3.6V

-±10μA

V

CC

Min < V

IN

< 5.5V - ±50 μA

C

IN

I/O capacitance V

IN

= GND; f = 1.0 MHz - 10 pF

I

CC

Operating supply current

(low power mode, active)

V

IN

= GND, No load; f = 1.0 MHz 85 (Typical) mA