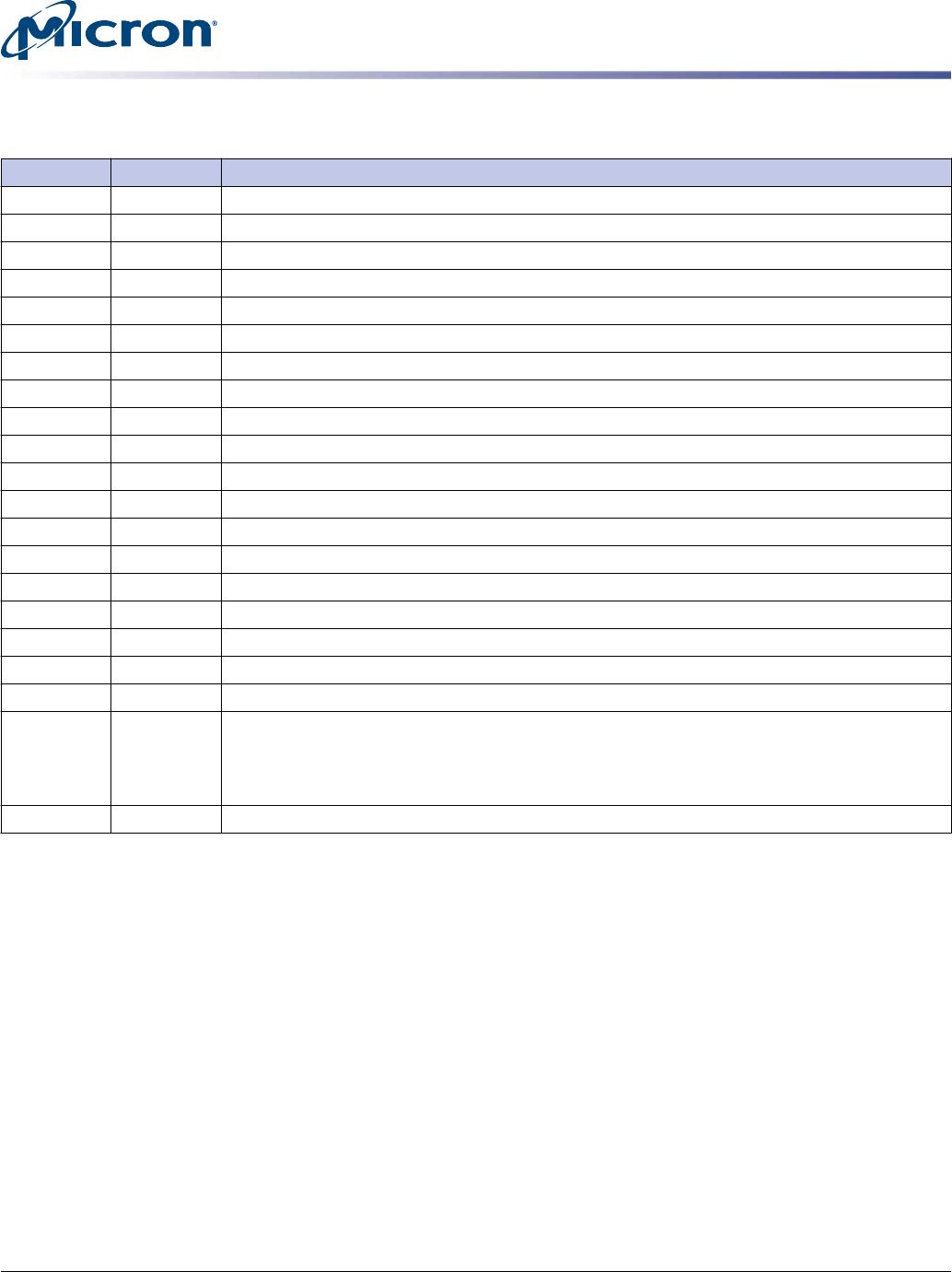

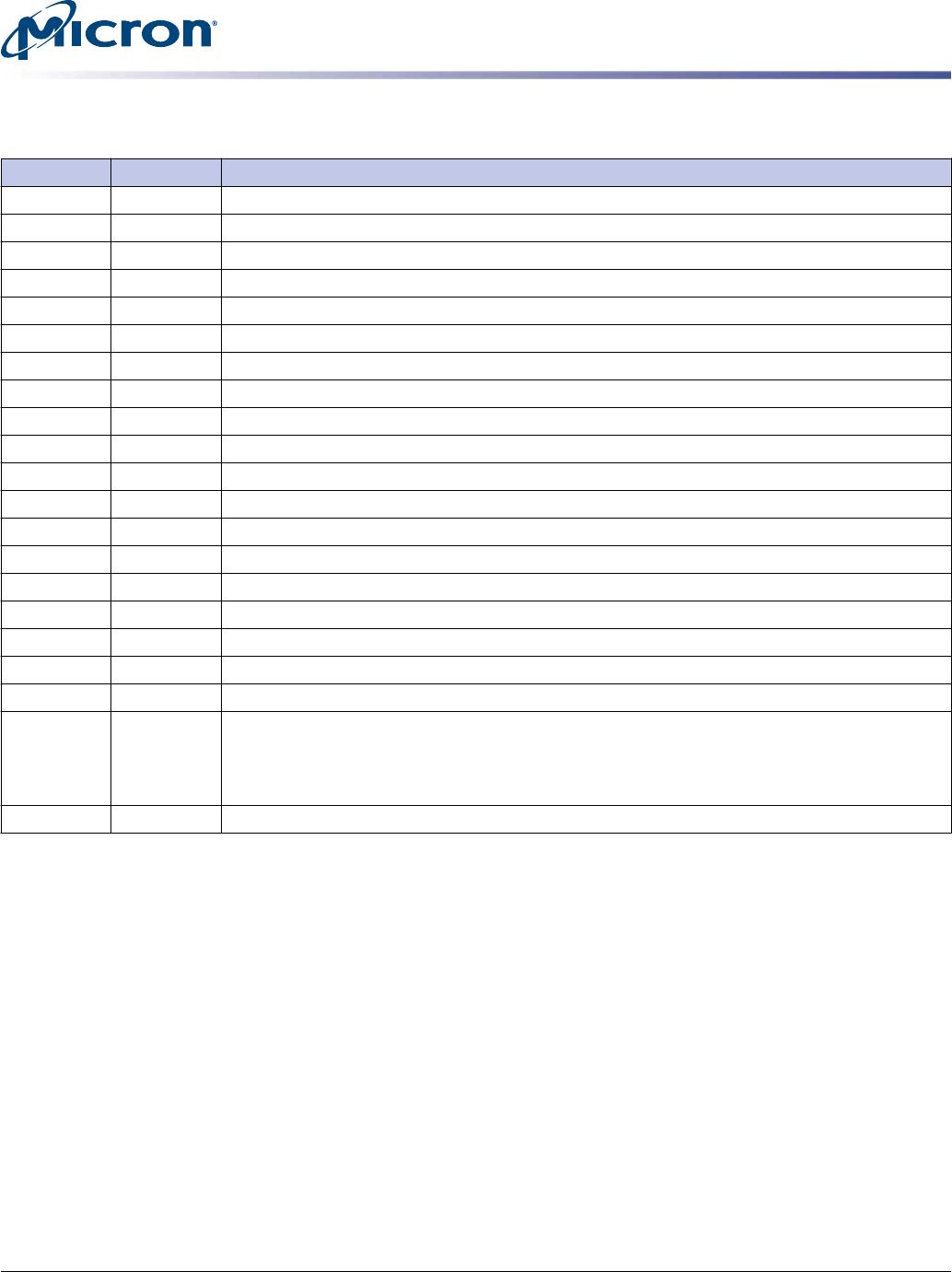

Table 5: Pin Descriptions

Symbol Type Description

PS[9:0] Input Primary southbound data, positive lines.

PS#[9:0] Input Primary southbound data, negative lines.

SCK Input System clock input, positive line.

SCK# Input System clock Input, negative line.

SCL Input Serial presence-detect (SPD) clock input.

SS[9:0] Input Secondary southbound data, positive lines.

SS#[9:0] Input Secondary southbound data, negative lines.

PN[13:0] Output Primary northbound data, positive lines.

PN#[13:0] Output Primary northbound data, negative lines.

SN[13:0] Output Secondary northbound data, positive lines.

SN#[13:0] Output Secondary northbound data, negative lines.

SA[2:0] I/O SPD address inputs, also used to select the FBDIMM number in the AMB.

SDA I/O SPD data input/output.

RESET# Supply AMB reset signal.

V

CC

Supply AMB core power and AMB channel interface power (1.5V).

V

DD

Supply DRAM power and AMB DRAM I/O power (1.8V).

V

DDSPD

Supply SPD/AMB SMBUS power (3.3V).

V

SS

Supply Ground.

V

TT

Supply DRAM address/command/clock termination power (V

DD

/2).

M_TEST – The M_Test pin provides an external connection for testing the margin of V

REF

, which is pro-

duced by a voltage divider on the module. It is not intended to be used in normal system op-

eration and must not be connected (DNU) in a system. This test pin may have other features

on future card designs and will be included in this specification at that time.

DNU – Do not use.

1GB (x72, SR) 240-Pin DDR2 SDRAM FBDIMM

Pin Assignments and Descriptions

PDF: 09005aef83de8266

htf9c128x72fz.pdf - Rev. B 4/14 EN

4

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2009 Micron Technology, Inc. All rights reserved.