TwinDie™ 1.35V DDR3L SDRAM

MT41K2G4 – 128 Meg x 4 x 8 Banks x 2 Ranks

MT41K1G8 – 64 Meg x 8 x 8 Banks x 2 Ranks

Description

The 8Gb (TwinDie™) DDR3L SDRAM (1.35V) uses

Micron’s 4Gb DDR3L SDRAM die (essentially two

ranks of the 4Gb DDR3L SDRAM). Refer to Micron’s

4Gb DDR3 SDRAM data sheet for the specifications

not included in this document. Specifications for base

part number MT41K1G4 correlate to TwinDie manu-

facturing part number MT41K2G4; specifications for

base part number MT41K512M8 correlate to TwinDie

manufacturing part number MT41K1G8.

Features

• Uses 4Gb Micron die

• Two ranks (includes dual CS#, ODT, CKE, and ZQ

balls)

• Each rank has eight internal banks for concurrent

operation

• V

DD

= V

DDQ

= 1.35V (1.283–1.45V); backward com-

patible to V

DD

= V

DDQ

= 1.5V ±0.075V

• 1.35V center-terminated push/pull I/O

• JEDEC-standard ball-out

• Low-profile package

• T

C

of 0°C to 95°C

– 0°C to 85°C: 8192 refresh cycles in 64ms

– 85°C to 95°C: 8192 refresh cycles in 32ms

– Industrial temperature (IT) available (Rev. E)

Options Marking

• Configuration

– 128 Meg x 4 x 8 banks x 2 ranks 2G4

– 64 Meg x 8 x 8 banks x 2 ranks 1G8

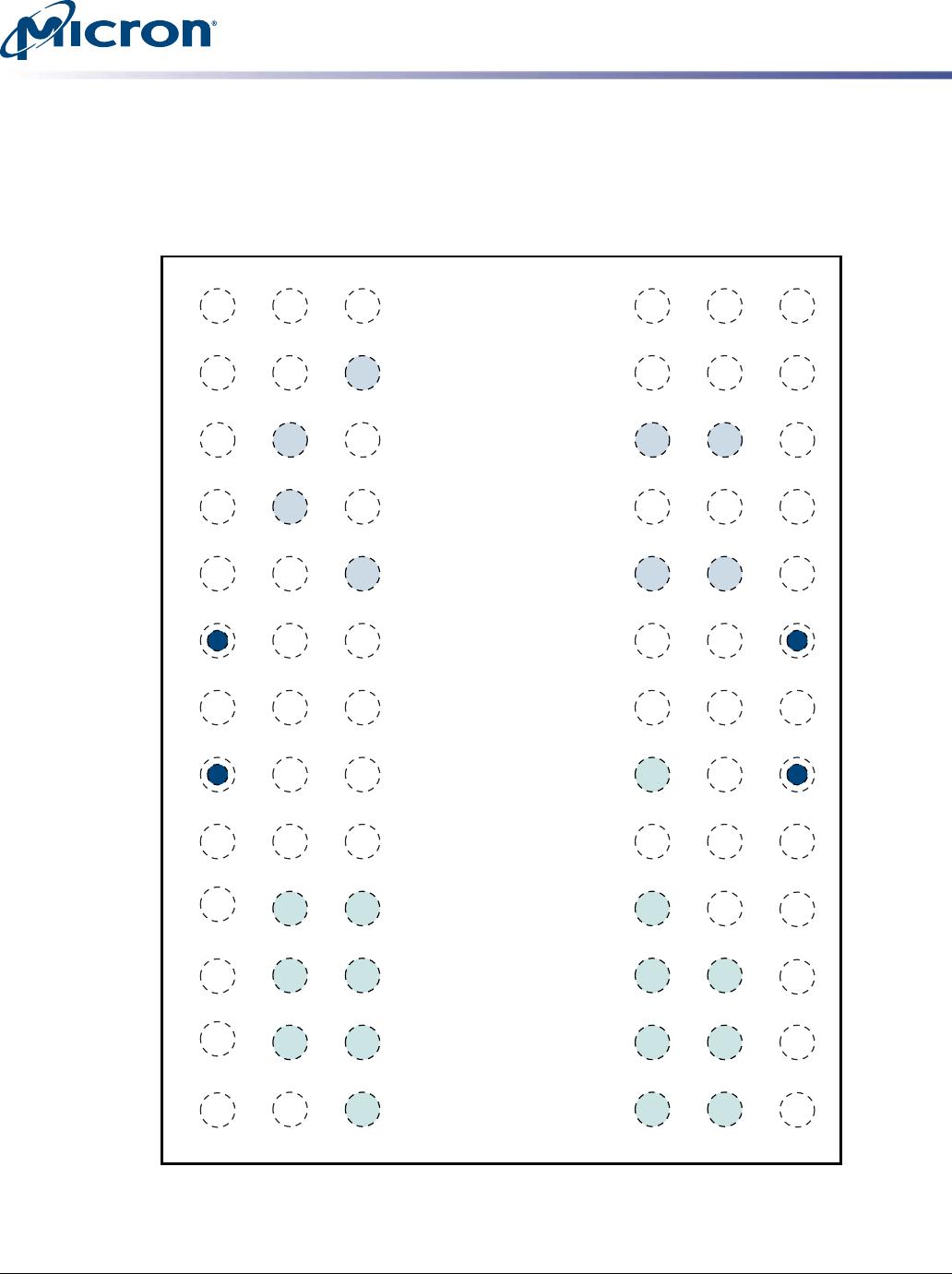

• FBGA package (Pb-free)

– 78-ball FBGA

(10.5mm x 12mm x 1.2mm) Die

Rev :D

THE

– 78-ball FBGA

(9.5mm x 11.5mm x 1.2mm) Die

Rev :E

TRF

• Timing – cycle time

1

– 1.071ns @ CL = 13 (DDR3L-1866) -107

– 1.25ns @ CL = 11 (DDR3L-1600) -125

– 1.5ns @ CL = 9 (DDR3L-1333) -15E

– 1.87ns @ CL = 7 (DDR3L-1066) -187E

• Self refresh

– Standard None

• Operating temperature

– Commercial (0°C ≤ T

C

≤ 95°C) None

– Industrial (-40°C ≤ T

C

≤ 95°C) Rev. E IT

• Revision :D/:E

Note:

1. CL = CAS (READ) latency.

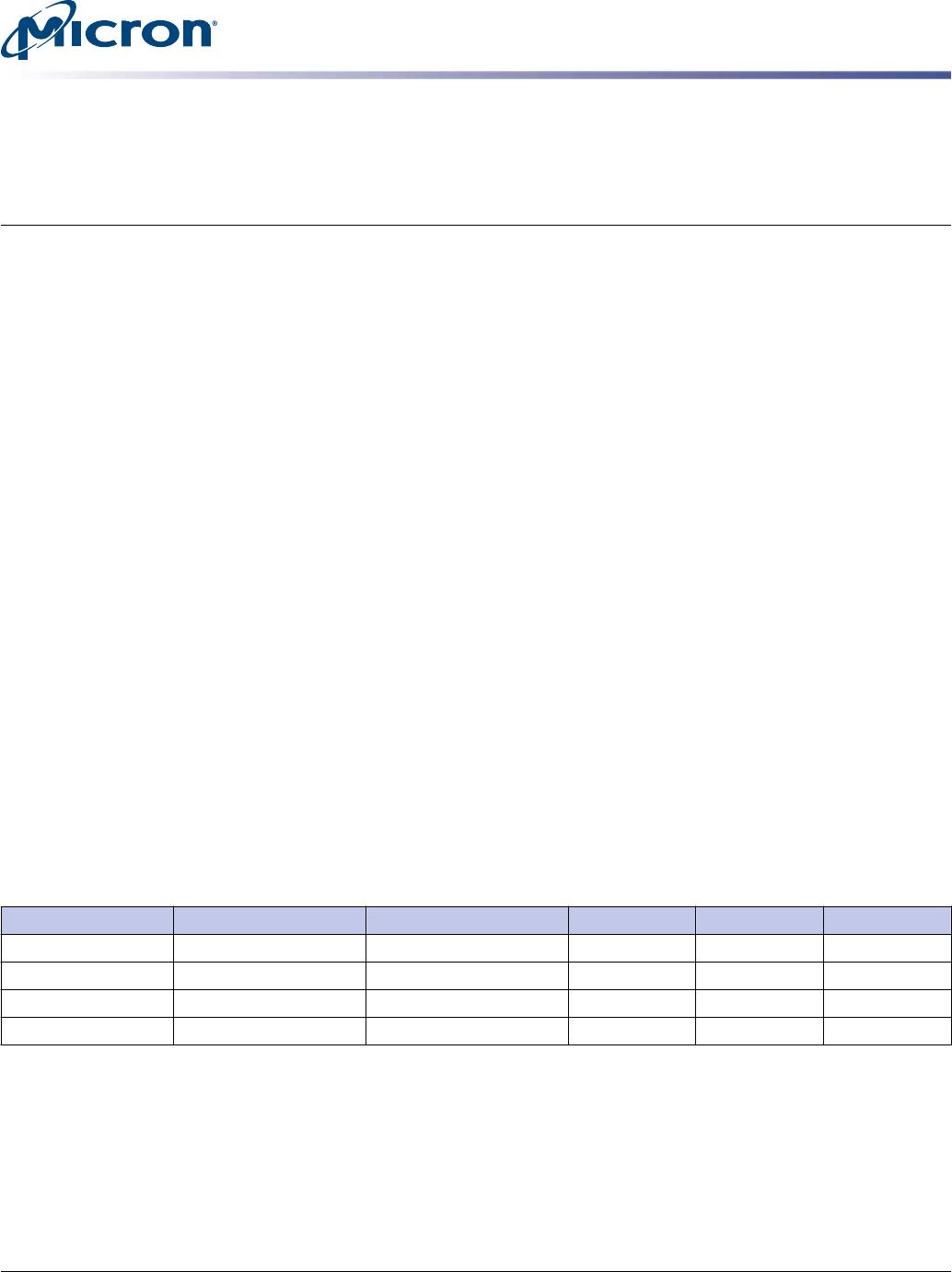

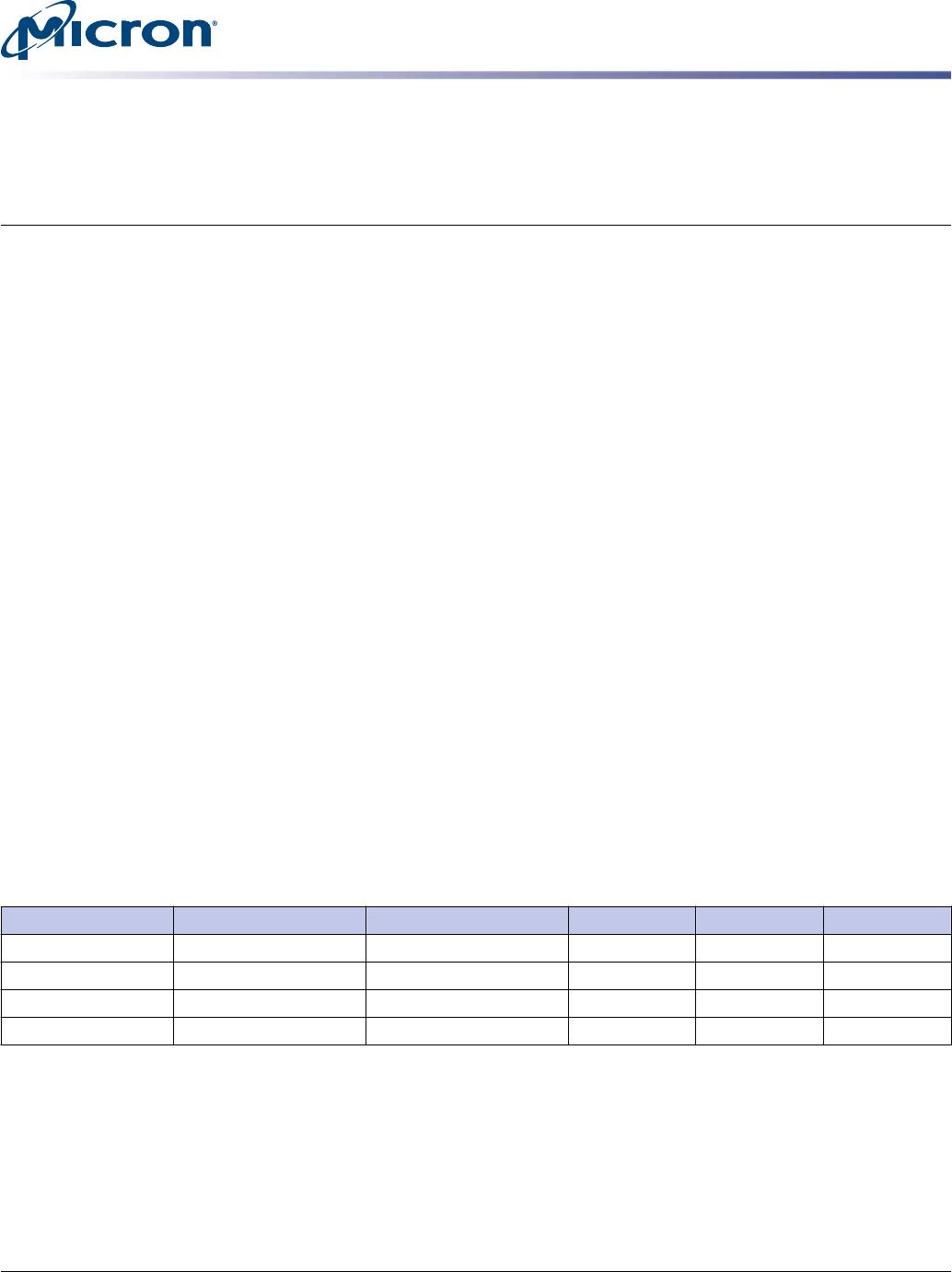

Table 1: Key Timing Parameters

Speed Grade Data Rate (MT/s) Target

t

RCD-

t

RP-CL

t

RCD (ns)

t

RP (ns) CL (ns)

-107

1

,

2

,

3

1866 13-13-13 13.91 13.91 13.91

-125

1

,

2

1600 11-11-11 13.75 13.75 13.75

-15E

1

1333 9-9-9 13.5 13.5 13.5

-187E 1066 7-7-7 13.1 13.1 13.1

Notes:

1. Backward compatible to 1066, CL = 7 (-187E).

2. Backward compatible to 1333, CL = 9 (-15E).

3. Backward compatible to 1600, CL = 11 (-125).

8Gb: x4, x8 TwinDie DDR3L SDRAM

Description

PDF: 09005aef84787542

DDR3L_8Gb_x4_x8_2CS_TwinDie.pdf - Rev. F 05/13 EN

1

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Products and specifications discussed herein are subject to change by Micron without notice.