LTC1981/LTC1982

6

APPLICATIONS INFORMATION

WUU

U

Figure 3. Direct Interface to 3.3V Logic

V

CC

GATE 1

SHDN 1

GND

1/2 LTC1982

5V

LOAD

1981/82 F03

3.3V

5V

Si3442DV

Figure 1. Powering a Large Capactive Load

Figure 2. Direct Interface to 5V Logic

Logic-Level MOSFET Switches

The LTC1981/LTC1982 are designed to operate with logic-

level N-channel MOSFET switches. Although there is some

variation among manufacturers, logic-level MOSFET

switches are typically rated with V

GS

= 4V with a maximum

continuous V

GS

rating of ±8V. RDS (ON) and maximum

V

DS

ratings are similar to standard MOSFETs and there is

generally little price differential. When operating at supply

voltages of 5V or greater, care must be taken when

selecting the MOSFET. The LTC1981/LTC1982 limit the

output voltage to between 6.9V and 7.5V. The V

GS

devel-

oped for the MOSFET may be too low to sufficiently turn on

the MOSFET. MOSFETs rated at 2.5V, or less, will be better

suited for applications where the supply voltages ap-

proach 5V.

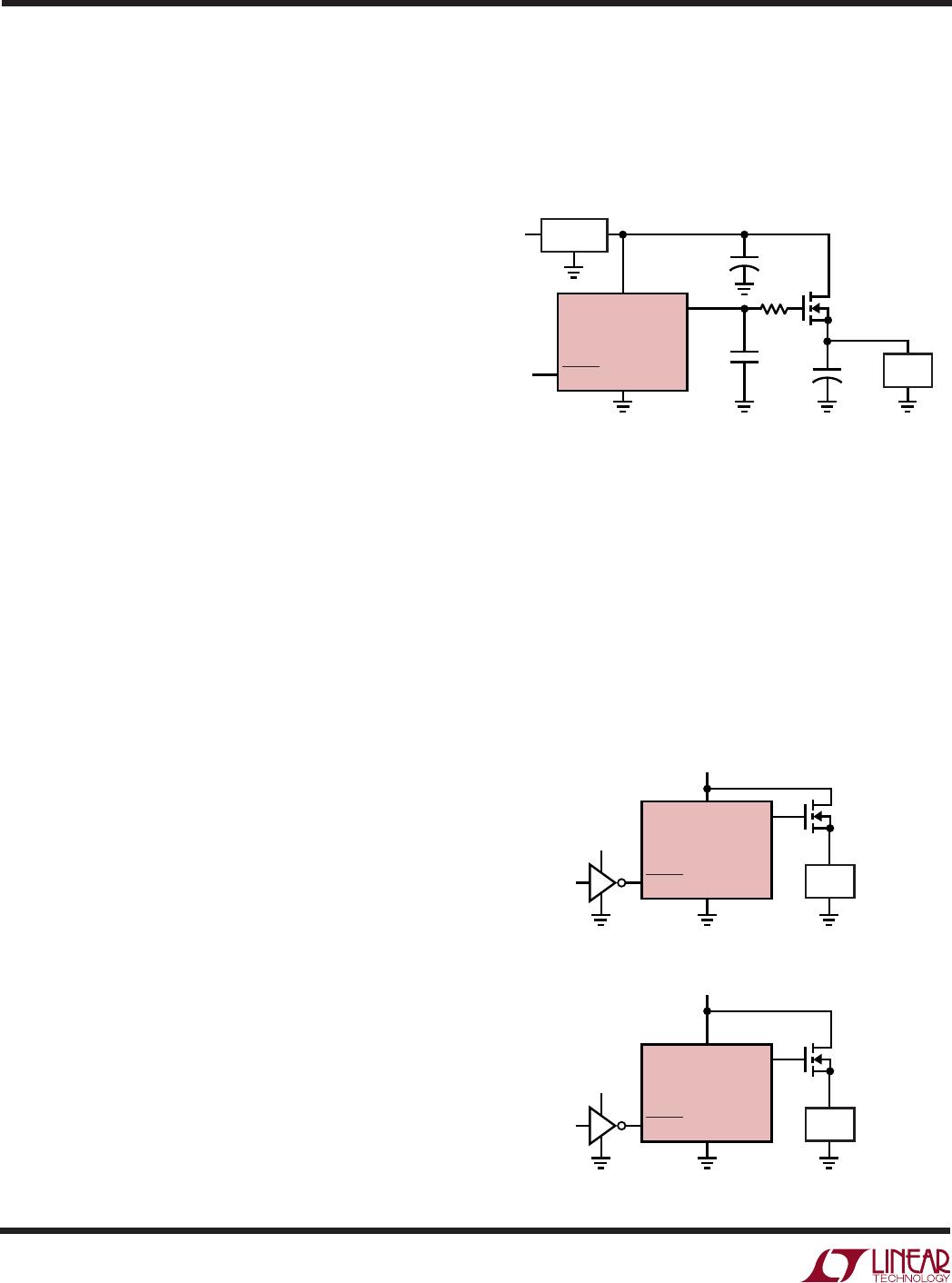

Powering Large Capacitive Loads

Electrical subsystems in portable battery-powered equip-

ment are typically bypassed with large filter capacitors to

reduce supply transients and supply induced glitching. If

not properly powered however, these capacitors may

themselves become the source of supply glitching. For

example, if a 100µF capacitor is powered through a switch

with a slew rate of 0.1V/µs, the current during start-up is:

I

START

= C(∆V/∆t)

= (100 • 10

–6

)(1 • 10

5

)

= 10A

Obviously, this is too much current for the regulator (or

output capacitor) to supply and the output will glitch by as

much as a few volts.

The start up current can be substantially reduced by

limiting the slew rate at the gate of an N-channel as shown

in Figure 1. The gate drive output of the LTC1981/LTC1982

have an internal 30k resistor (15k LTC1981) in series with

each of the output gate drive pins (see Functional Block

Diagram). Therefore, it only needs an external 0.1µF

capacitor (0.22µF for the LTC1981) to create enough RC

delay to substantially slow the slew rate of the MOSFET

gate to approximately 0.6V/ms. Since the MOSFET is

operating as a source follower, the slew rate at the source

is essentially the same as that at the gate, reducing the

startup current to approximately 60mA which is easily

managed by the system regulator. R1 is required to

eliminate the possibility of parasitic MOSFET oscillations

during switch transitions. It is a good practice to isolate the

gates of paralleled MOSFETs with 1k resistors to decrease

the possibility of interaction between switches.

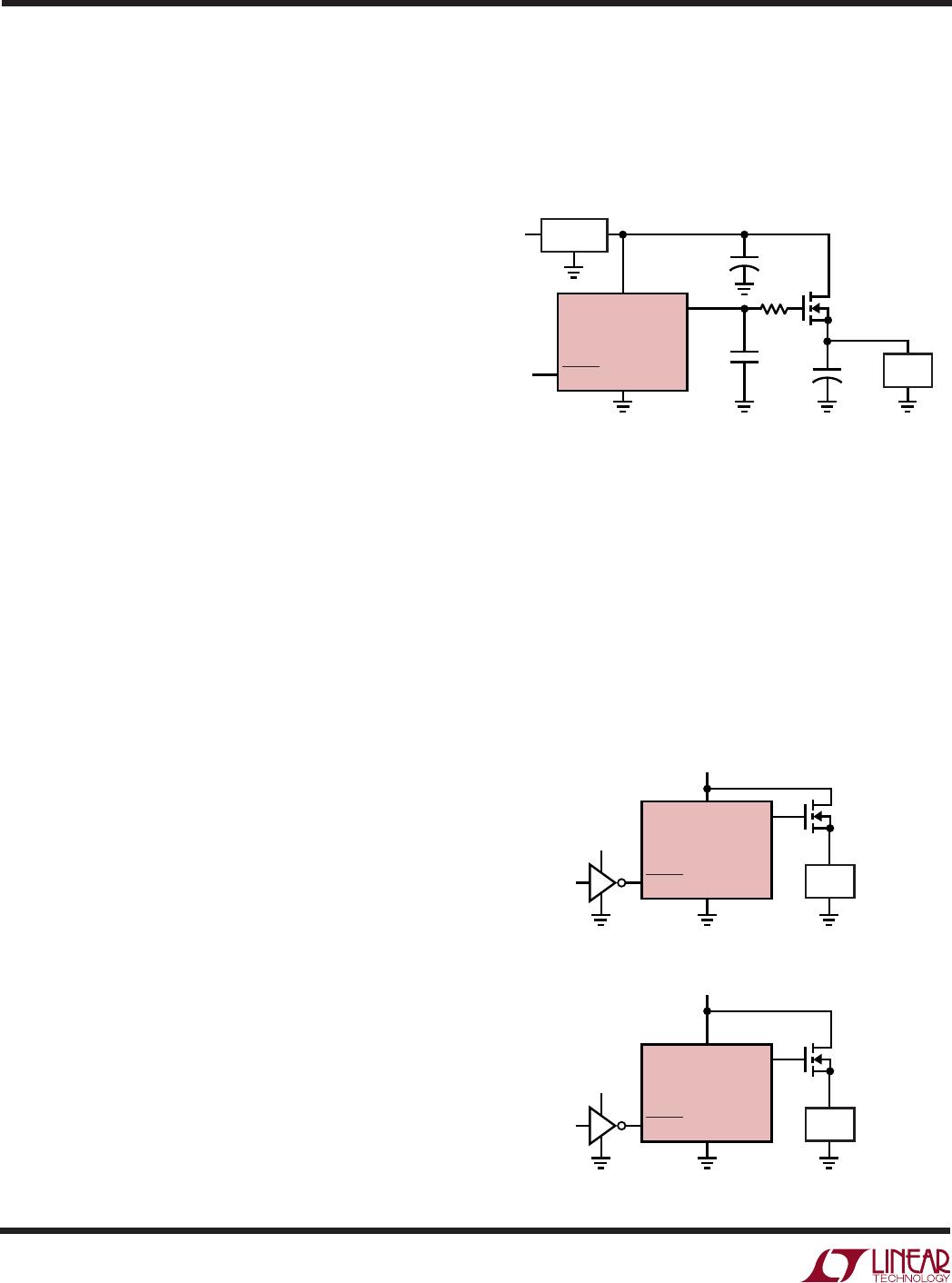

Mixed 5V/3V Systems

Because the input ESD protection diodes are referenced to

the GND pin instead of the supply pin, it is possible to drive

the LTC1981/LTC1982 inputs from 5V CMOS or TTL logic

even though the LTC1981/LTC1982 is powered from a

3.3V supply as shown in Figure 2. Likewise, because the

input threshold voltage high is never greater than 1.6V, the

reverse situation is true. The LTC1981/LTC1982 can be

driven with 3V CMOS or TTL even when the supply to the

device is as high as 5V as shown in Figure 3.

V

CC

GATE 1

SHDN 1

GND

1/2 LTC1982

+

LT1129-3.3

+

V

IN

ON/OFF

3.3µF

R1

1k

C1

0.1µF

C

L

100µF

3.3V

LOAD

1981/82 F01

3.3V

Si3442DV

V

CC

GATE 1

SHDN 1

GND

1/2 LTC1982

3.3V

LOAD

1981/82 F02

3.3V

Si3442DV

5V