CY15B064J

64-Kbit (8K × 8) Serial (I

2

C) Automotive-A

F-RAM

Cypress Semiconductor Corporation • 198 Champion Court • San Jose, CA 95134-1709 • 408-943-2600

Document Number: 002-10221 Rev. *B Revised March 24, 2017

64-Kbit (8K × 8) Serial (I

2

C) Automotive-A F-RAM

Features

■ 64-Kbit ferroelectric random access memory (F-RAM) logically

organized as 8K × 8

❐ High-endurance 100 trillion (10

14

) read/writes

❐ 151-year data retention (See the Data Retention and

Endurance table)

❐ NoDelay™ writes

❐ Advanced high-reliability ferroelectric process

■ Fast two-wire Serial interface (I

2

C)

❐ Up to 1-MHz frequency

❐ Direct hardware replacement for serial (I

2

C) EEPROM

❐ Supports legacy timings for 100 kHz and 400 kHz

■ Low power consumption

❐ 100 A (typ) active current at 100 kHz

❐ 3 A (typ) standby current

■ Voltage operation: V

DD

= 2.7 V to 3.65 V

■ Automotive-A temperature: –40 C to +85 C

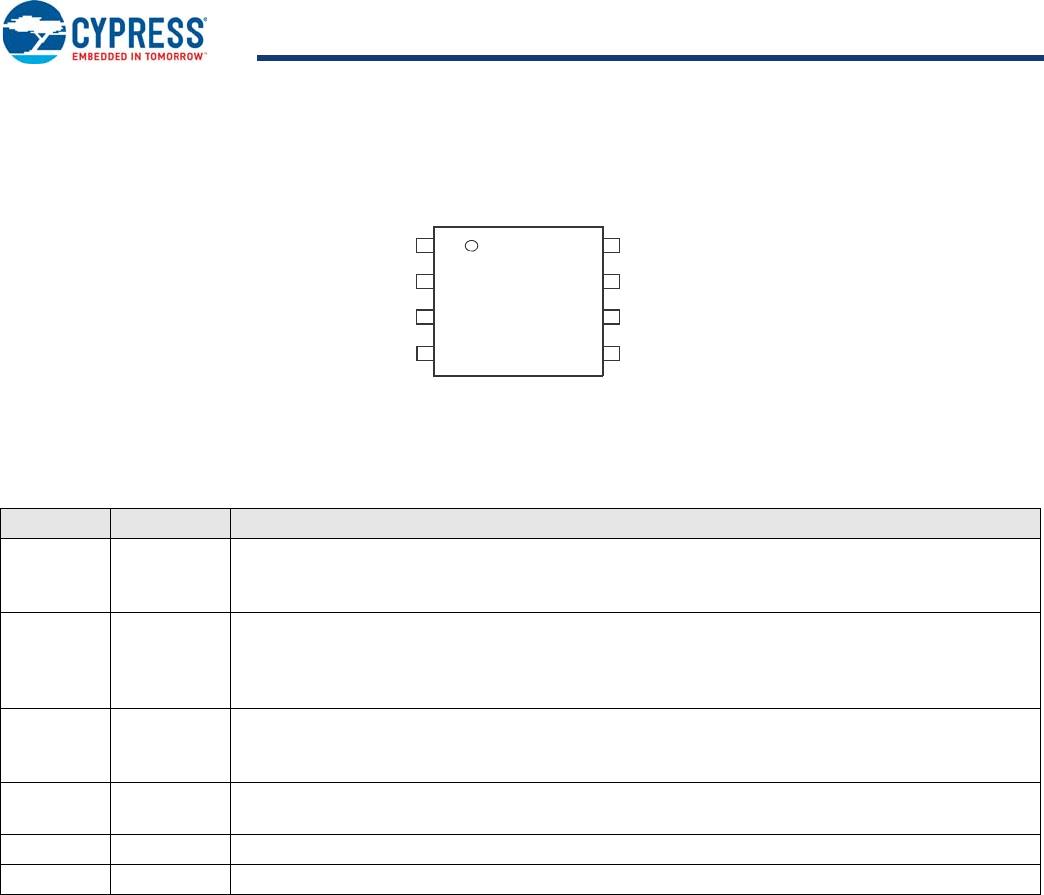

■ 8-pin small outline integrated circuit (SOIC) package

■ Restriction of hazardous substances (RoHS) compliant

Functional Description

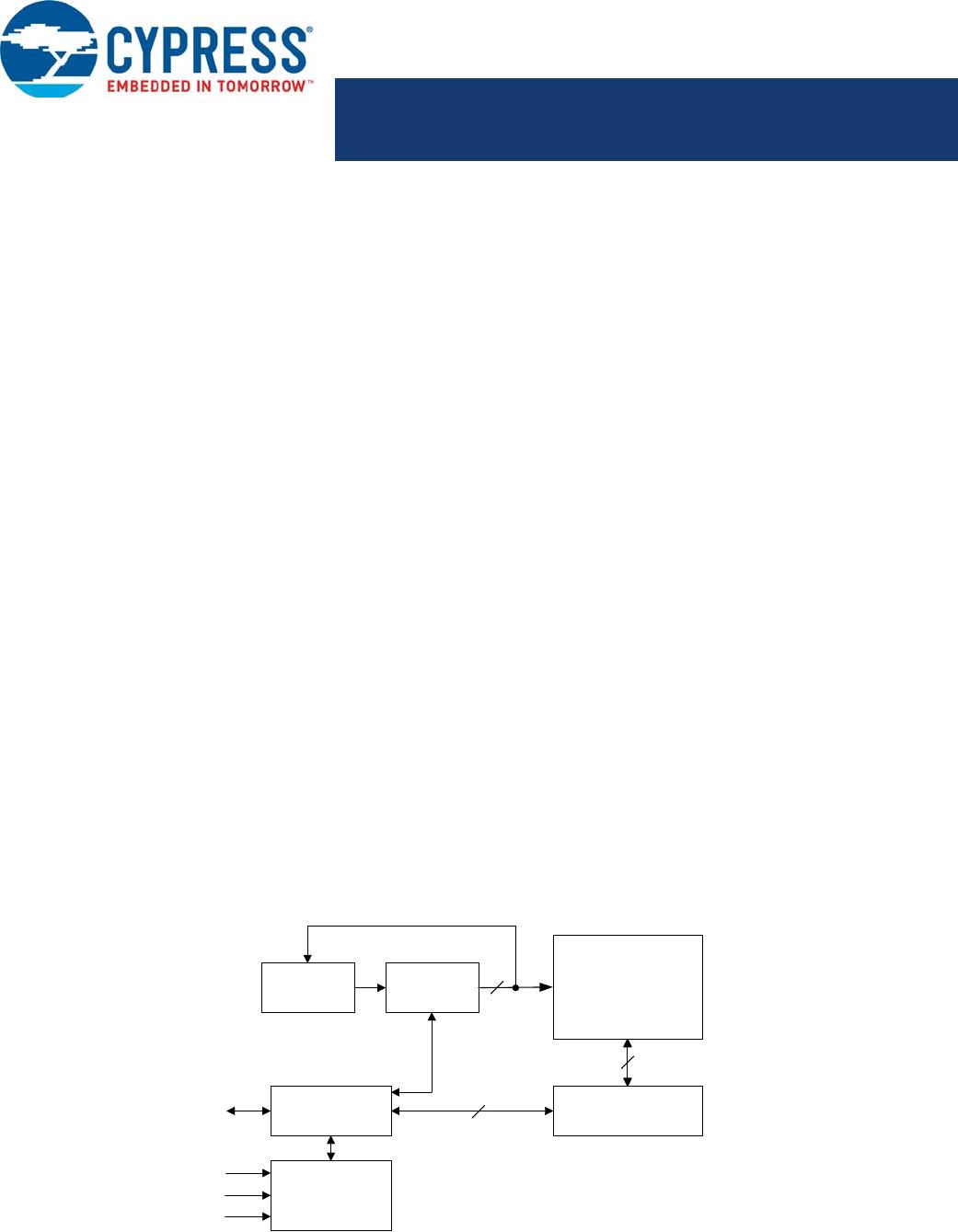

The CY15B064J is a 64-Kbit nonvolatile memory employing an

advanced ferroelectric process. A ferroelectric random access

memory or F-RAM is nonvolatile and performs reads and writes

similar to a RAM. It provides reliable data retention for 151 years

while eliminating the complexities, overhead, and system-level

reliability problems caused by EEPROM and other nonvolatile

memories.

Unlike EEPROM, the CY15B064J performs write operations at

bus speed. No write delays are incurred. Data is written to the

memory array immediately after each byte is successfully

transferred to the device. The next bus cycle can commence

without the need for data polling. In addition, the product offers

substantial write endurance compared with other nonvolatile

memories. Also, F-RAM exhibits much lower power during writes

than EEPROM since write operations do not require an internally

elevated power supply voltage for write circuits. The CY15B064J

is capable of supporting 10

14

read/write cycles, or 100 million

times more write cycles than EEPROM.

These capabilities make the CY15B064J ideal for nonvolatile

memory applications, requiring frequent or rapid writes.

Examples range from data logging, where the number of write

cycles may be critical, to demanding industrial controls where the

long write time of EEPROM can cause data loss. The

combination of features allows more frequent data writing with

less overhead for the system.

The CY15B064J provides substantial benefits to users of serial

(I

2

C) EEPROM as a hardware drop-in replacement. The device

specifications are guaranteed over an automotive-a temperature

range of –40 C to +85 C.

Address

Latch

8 K x 8

F-RAM Array

Data Latch

8

SDA

Counter

Serial to Parallel

Converter

Control Logic

SCL

WP

A2-A0

13

8