©2011 Silicon Storage Technology, Inc. DS25080A 11/11

13

2 Mbit SPI Serial Flash

SST25LF020A

Not Recommended for New Designs

Microchip Technology Company

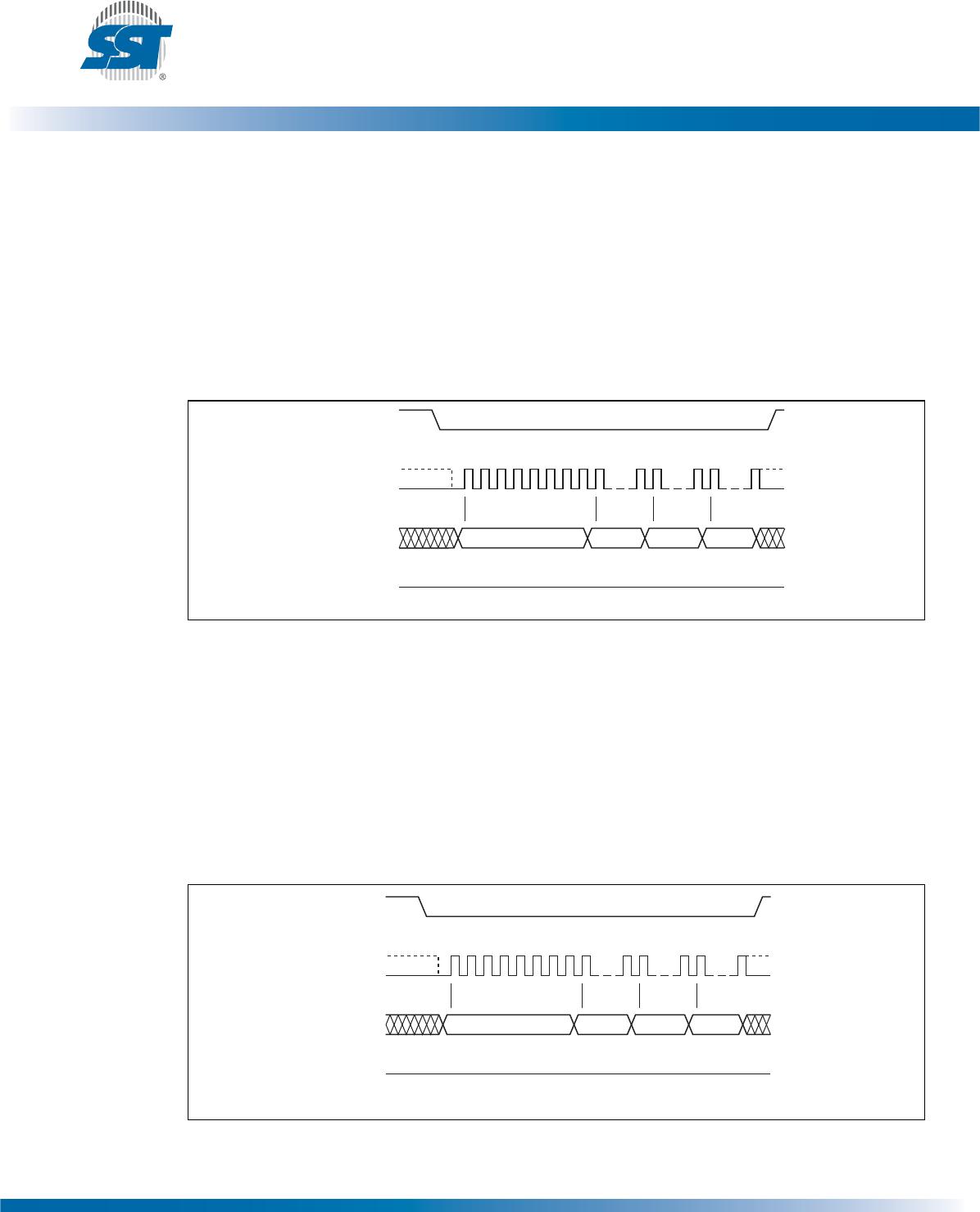

Sector-Erase

The Sector-Erase instruction clears all bits in the selected 4 KByte sector to FFH. A Sector-Erase

instruction applied to a protected memory area will be ignored. Prior to any Write operation, the Write-

Enable (WREN) instruction must be executed. CE# must remain active low for the duration of the any

command sequence. The Sector-Erase instruction is initiated by executing an 8-bit command, 20H, fol-

lowed by address bits [A

23

-A

0

]. Address bits [A

MS

-A

12

](A

MS

= Most Significant address) are used to

determine the sector address (SA

X

), remaining address bits can be V

IL

or V

IH.

CE# must be driven high

before the instruction is executed. The user may poll the Busy bit in the software status register or wait

T

SE

for the completion of the internal self-timed Sector-Erase cycle. See Figure 9 for the Sector-Erase

sequence.

Figure 9: Sector-Erase Sequence

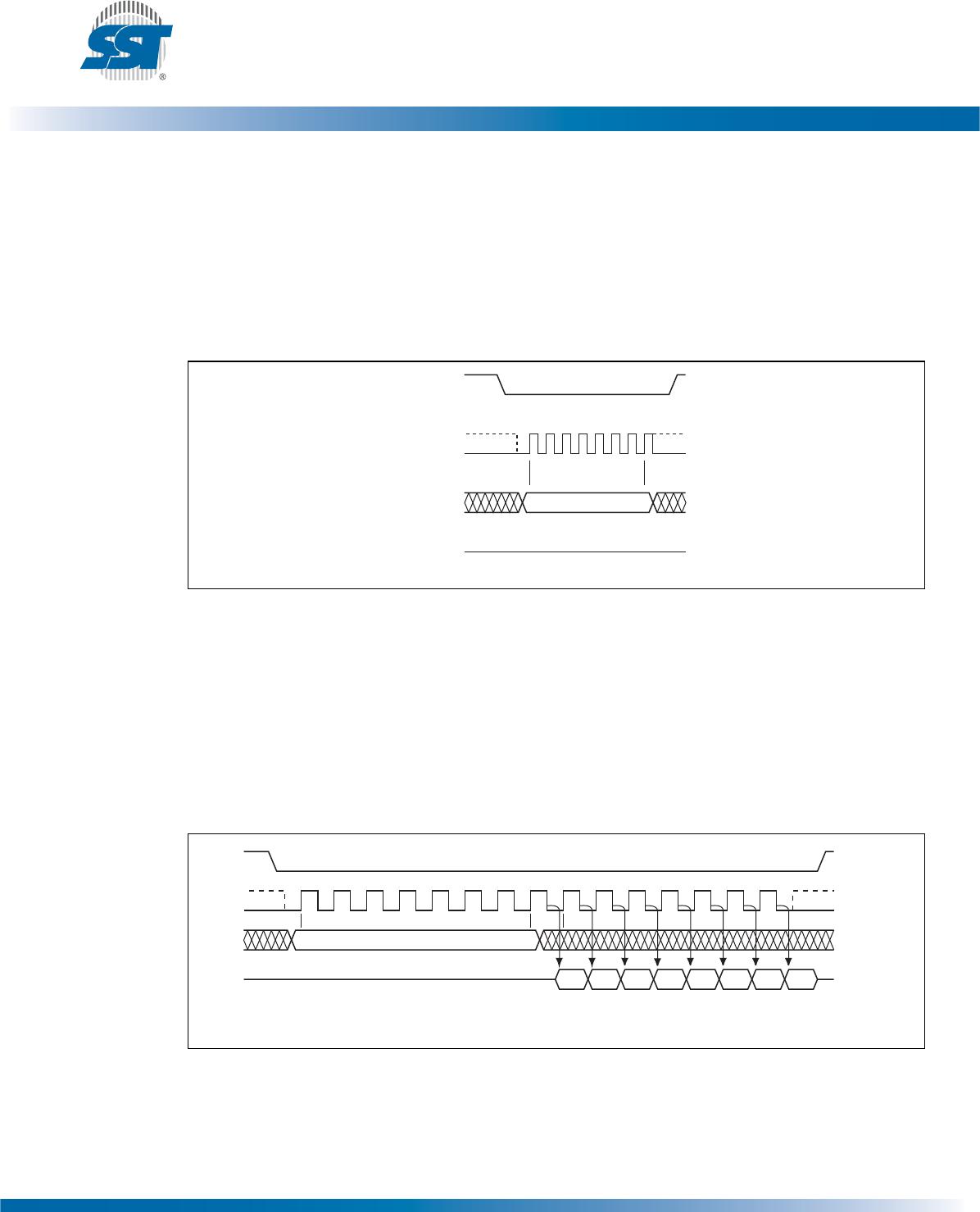

Block-Erase

The Block-Erase instruction clears all bits in the selected 32 KByte block to FFH. A Block-Erase

instruction applied to a protected memory area will be ignored. Prior to any Write operation, the Write-

Enable (WREN) instruction must be executed. CE# must remain active low for the duration of any com-

mand sequence. The Block-Erase instruction is initiated by executing an 8-bit command, 52H, followed

by address bits [A

23

-A

0

]. Address bits [A

MS

-A

15

](A

MS

= Most significant address) are used to deter-

mine block address (BA

X

), remaining address bits can be V

IL

or V

IH

. CE# must be driven high before the

instruction is executed. The user may poll the Busy bit in the software status register or wait T

BE

for the com-

pletion of the internal self-timed Block-Erase cycle. See Figure 10 for the Block-Erase sequence.

Figure 10: Block-Erase Sequence

CE#

SO

SI

SCK

ADD.

012345678

ADD. ADD.

20

HIGH IMPEDANCE

15 16

23

24

31

MODE 0

MODE 3

1242 F08.0

MSBMSB

CE#

SO

SI

SCK

ADD.

012345678

ADD. ADD.

52

HIGH IMPEDANCE

15 16

23

24

31

MODE 0

MODE 3

1242 F09.0

MSB MSB