Electrical Characteristics – AC and DC Output Measurement Levels

Single-Ended Outputs

Table 7: Single-Ended Output Levels

Parameter Symbol DDR4-1600 to DDR4-3200 Unit

DC output high measurement level (for IV curve linearity) V

OH(DC)

1.1 × V

DDQ

V

DC output mid measurement level (for IV curve linearity) V

OM(DC)

0.8 × V

DDQ

V

DC output low measurement level (for IV curve linearity) V

OL(DC)

0.5 × V

DDQ

V

AC output high measurement level (for output slew rate) V

OH(AC)

(0.7 + 0.15) × V

DDQ

V

AC output low measurement level (for output slew rate) V

OL(AC)

(0.7 - 0.15) × V

DDQ

V

Note:

1. The swing of ±0.15 × V

DDQ

is based on approximately 50% of the static single-ended

output peak-to-peak swing with a driver impedance of RZQ/7 and an effective test load

of 50Ω to V

TT

= V

DDQ

.

Using the same reference load used for timing measurements, output slew rate for fall-

ing and rising edges is defined and measured between V

OL(AC)

and V

OH(AC)

for single-

ended signals.

Table 8: Single-Ended Output Slew Rate Definition

Description

Measured

Defined byFrom To

Single-ended output slew rate for rising edge V

OL(AC)

V

OH(AC)

[V

OH(AC)

- V

OL(AC)

]/ΔTR

se

Single-ended output slew rate for falling edge V

OH(AC)

V

OL(AC)

[V

OH(AC)

- V

OL(AC)

]/ΔTF

se

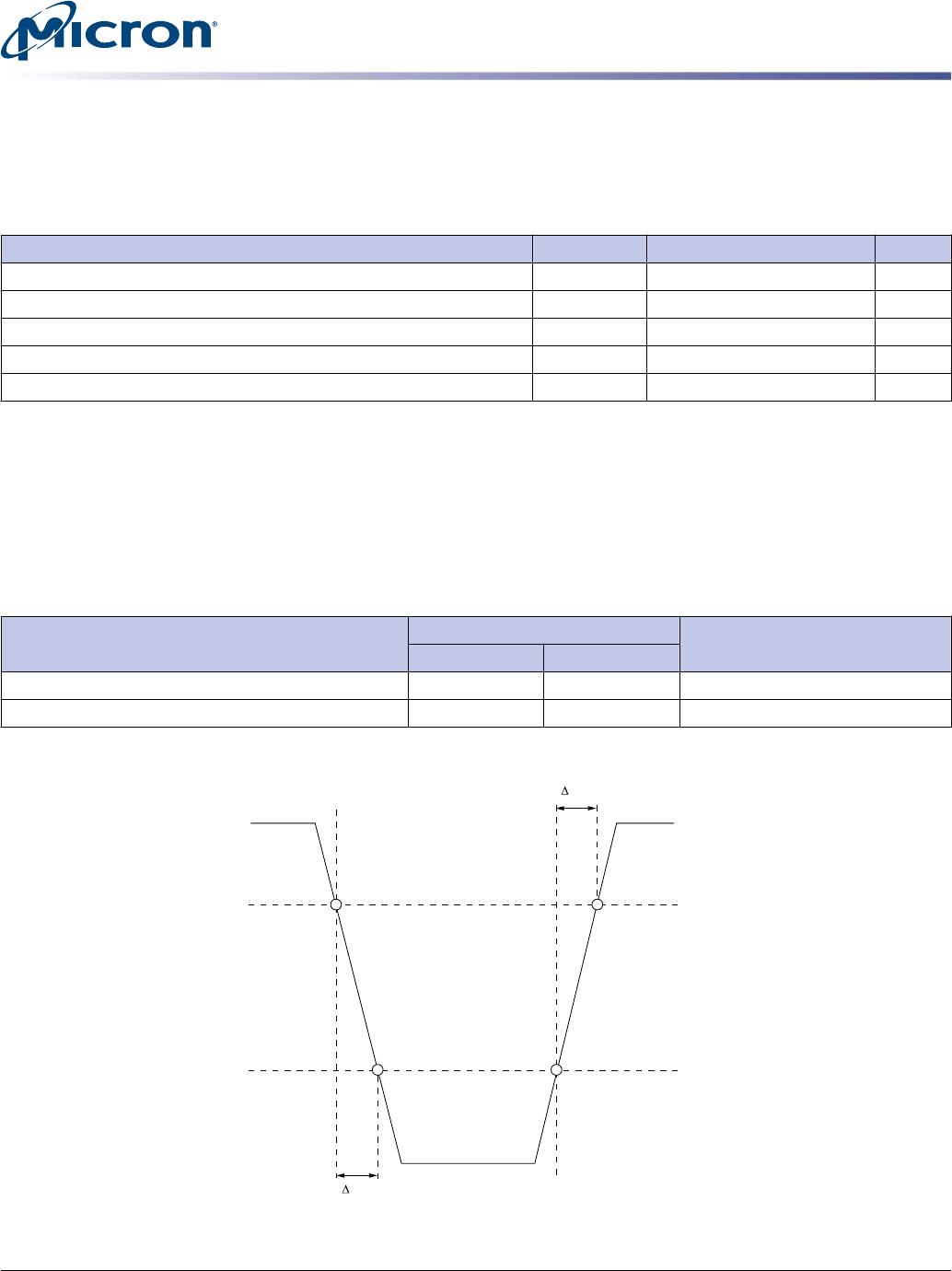

Figure 6: Single-ended Output Slew Rate Definition

TR

se

TF

se

V

OH(AC)

V

OL(AC)

Single-Ended Output Voltage (DQ)

16Gb: x4, x8 TwinDie DDR4 SDRAM

Electrical Characteristics – AC and DC Output Measurement

Levels

PDF: 09005aef85fd40a1

DDR4_16Gb_x4_x8_2CS_TwinDie.pdf - Rev. D 12/16 EN

12

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2015 Micron Technology, Inc. All rights reserved.