LTC4371

13

4371f

For more information www.linear.com/LTC4371

applicaTions inForMaTion

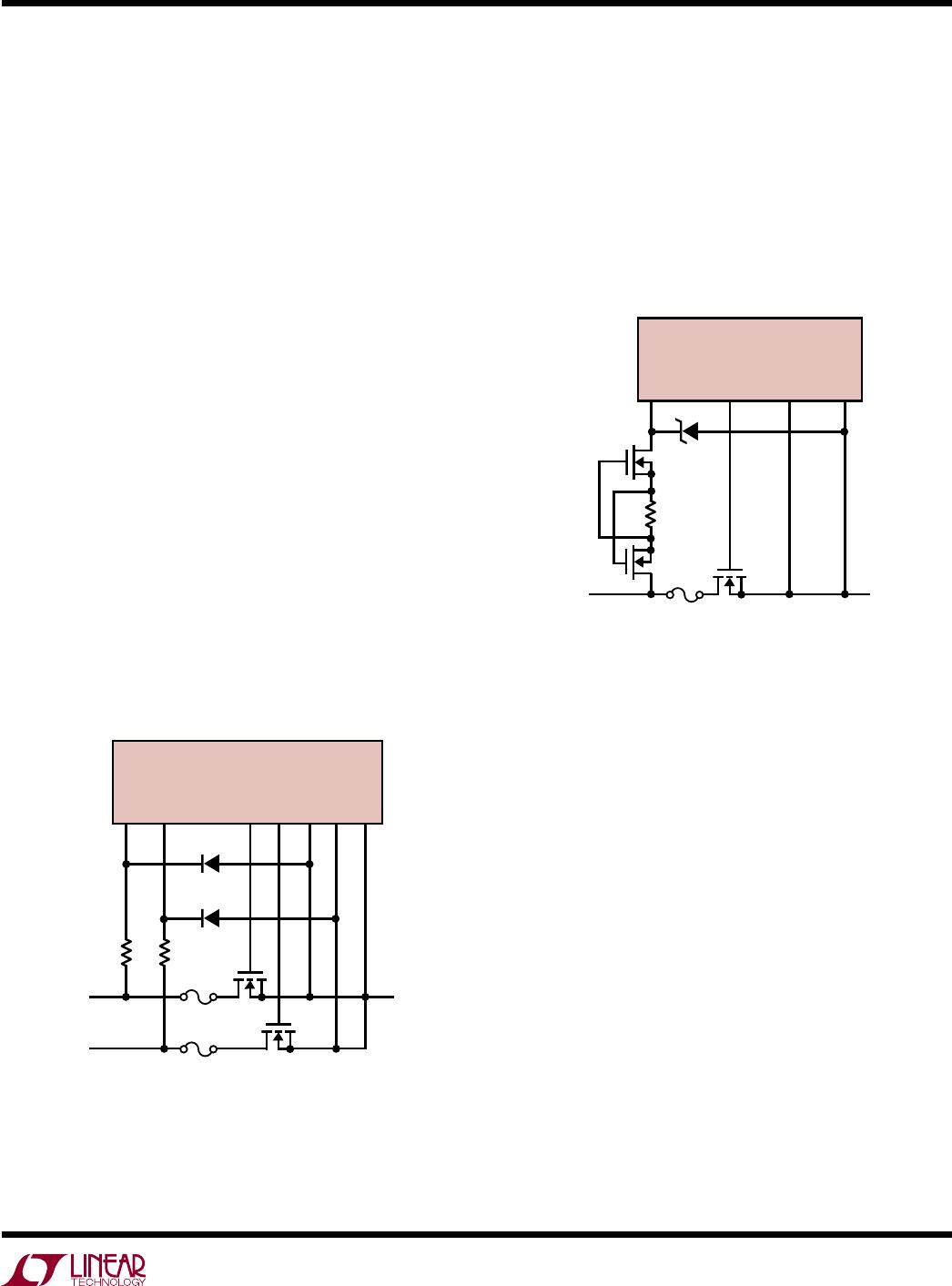

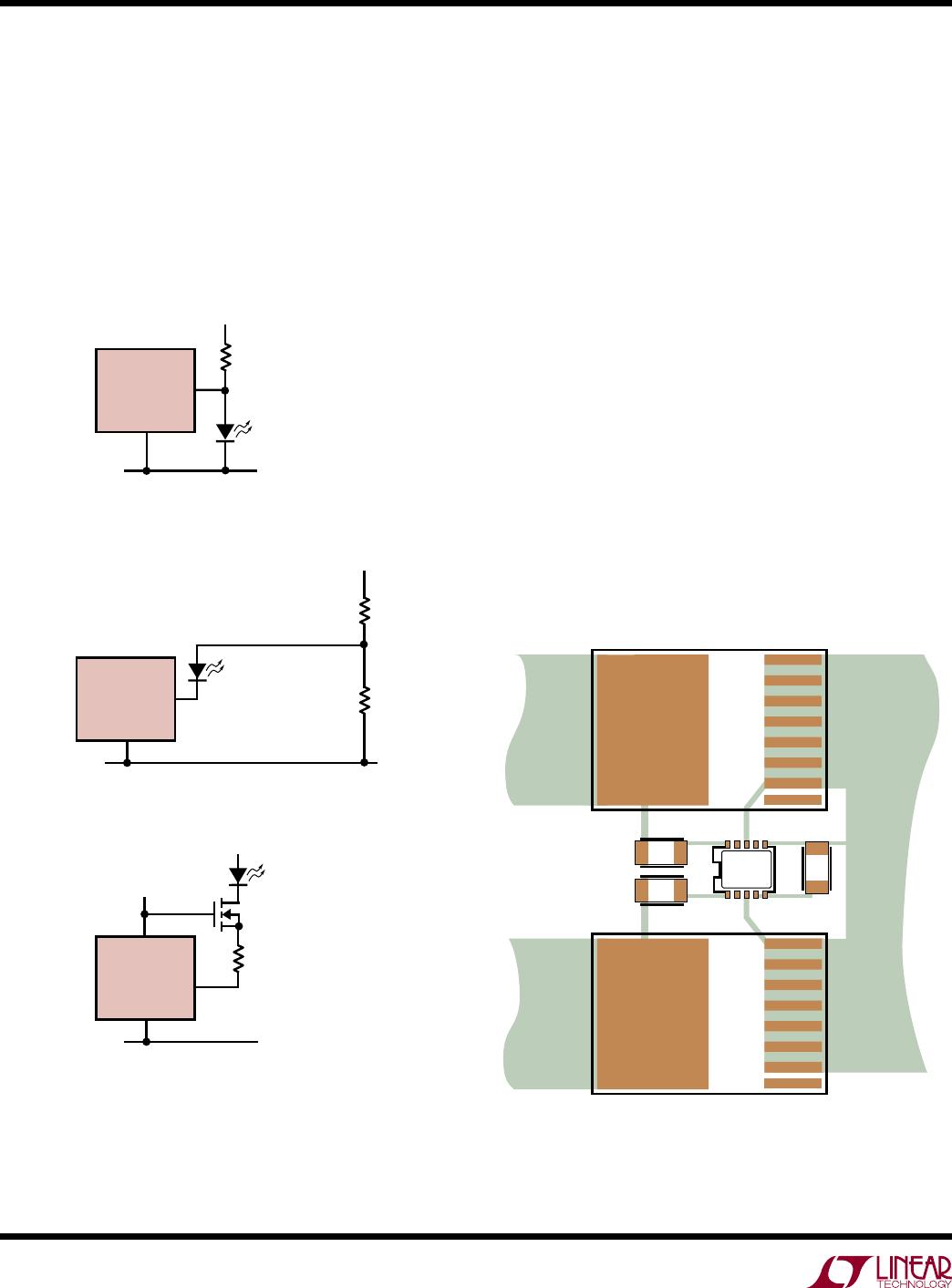

Figure 11. Fuse and Open MOSFET Detection

Figure 12. Back-to-Back Drain Pin Limiter for ±600V

Fuse and Open MOSFET Detection

The LTC4371 monitors ∆V

SD

of each channel as measured

across SA – DA and SB – DB. If ∆V

SD

of either channel

exceeds 200mV and the associated gate pin is driven fully

on, FAULTB pulls low to indicate a fault. Conditions lead

-

ing to high ∆V

SD

include excessive load current (I

LOAD

×

R

DS(ON)

> 200mV), an open circuit MOSFET or an open

fuse placed in series with the MOSFET. A high ∆V

SD

fault

is detected on only the highest voltage input supply, i.e.

the path that should be supplying power is, as a result of

one of the aforementioned conditions, unable to do so.

Temporary conditions, such as the initial 700mV drop

experienced when an input first rises to the point of sup

-

plying current but before the gate has been driven on, are

masked since the gate must also be high for fault detection.

The ∆V

SD

monitor can be used to detect open fuses, as

shown in Figure11. An open fuse gives the same signa-

ture as an open MOSFET: ∆

V

SD

increases beyond 200mV

when the affected input surpasses the opposing channel.

The connection shown in Figure 11 introduces a new

problem: an open fuse and open MOSFET exposes the DA

and DB pins to high negative voltage with respect to V

SS

.

Diodes D1 and D2 clamp the DA, DB pins from exceeding

the absolute maximum of –40V with respect to V

SS

.

Figure12 shows a protection method that extends DA and

DB pin operation to ±600V. The drain pins are clamped

by an 82V Zener diode. As shown, the DA pin is clamped

at 82V with respect to V

SS

in the positive direction, and

700mV below V

SS

in the negative direction. When a high

input voltage of either polarity is present, back-to-back

depletion mode N-channel MOSFETs limit the current in

the Zener diode to V

GS(TH)

/R

DA

(100μA for R

DA

= 20kΩ),

a value that is indefinitely sustainable.

FAULTB Pin

The open drain FAULTB pin pulls low when the ∆V

SD

of

either channel exceeds 200mV, while its gate is driven

fully on. FAULTB can sink 5mA to drive an LED for visual

indication, or an opto isolator to communicate across an

isolation barrier. The FAULTB pin voltage is limited to 17V

absolute maximum with respect to V

SS

in the high state

and cannot be pulled up to return except in low voltage

applications.

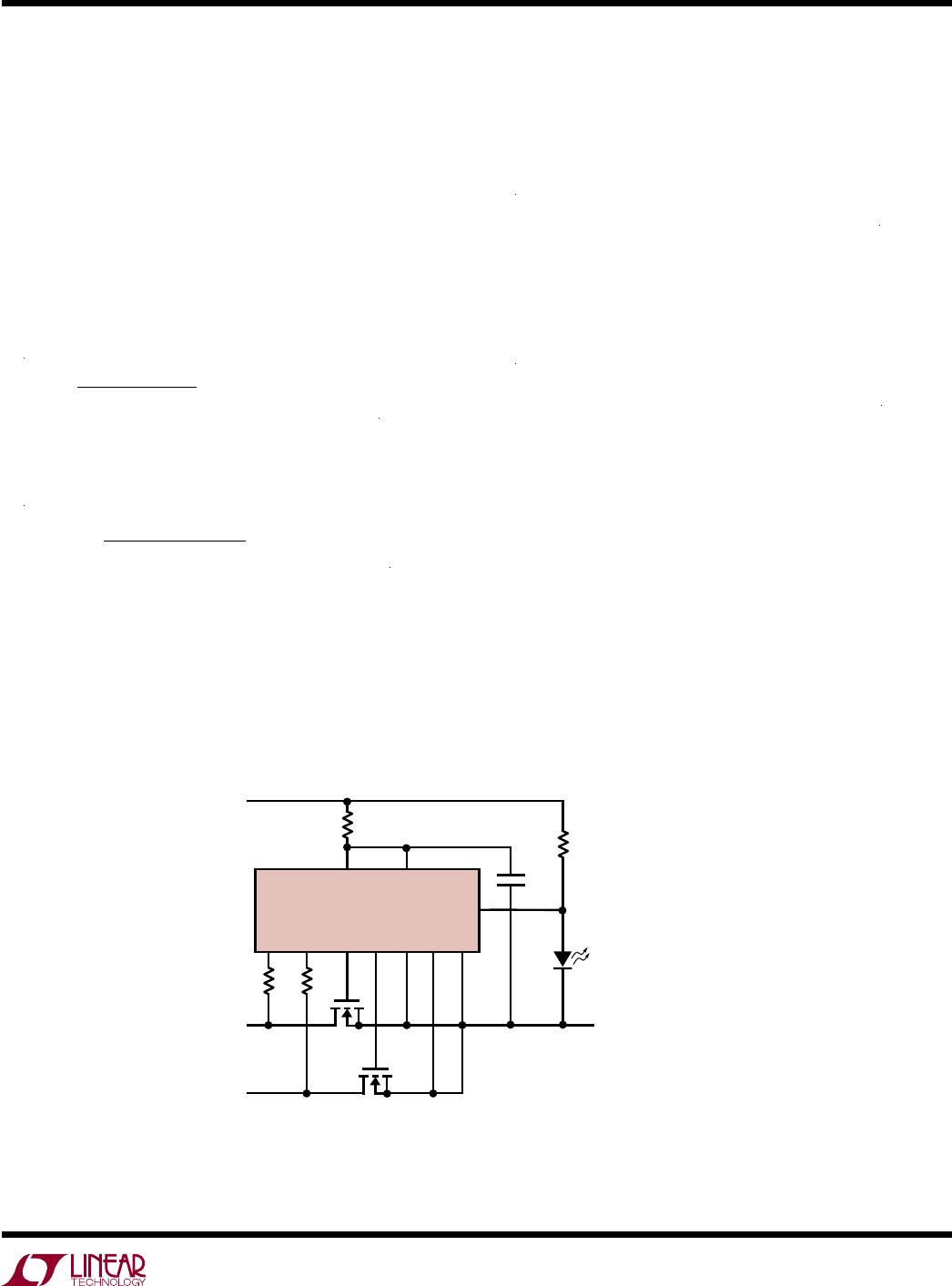

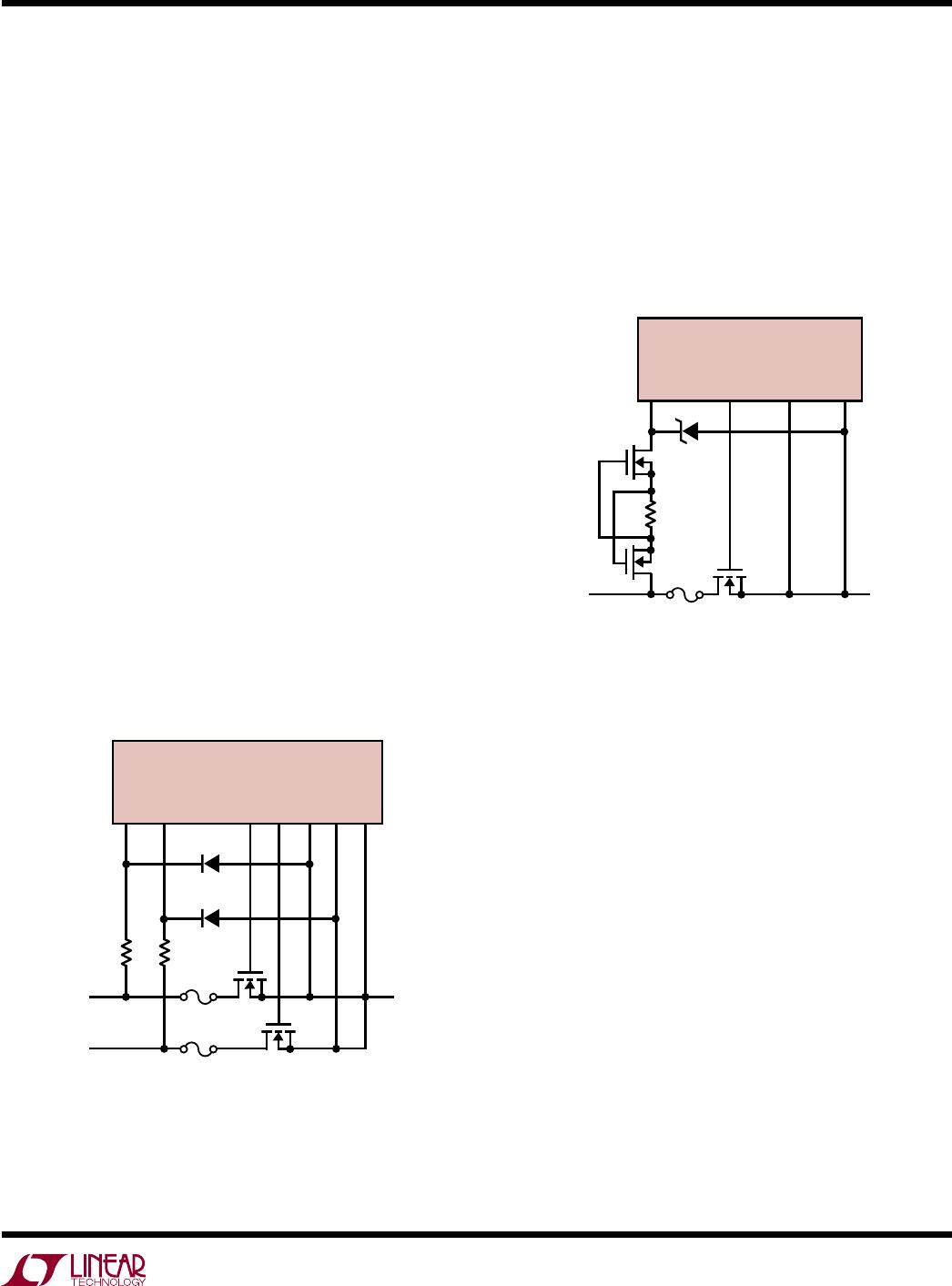

In Figure13, the FAULTB pin is used to shunt current away

from a green LED; the LED indicates (illuminates when) no

fault condition is present. The operating voltage is limited

at the low end by the minimum acceptable LED current,

and at the high end by the FAULTB pin’s 5mA capability.

Figure14 shows a simple implementation driving a red

LED; the LED indicates a fault condition is present. While

this simple configuration works well in –48V applications,

the maximum operating voltage is limited to 100V, the LED

4371 F11

LTC4371

DA DB GA GB SA SB V

SS

R

DA

20k

R

DB

20k

M1

M2

V

A

–36V TO

–72V

V

B

–36V TO

–72V

V

OUT

D1

1N4148W

D2

1N4148W

F1

F2

4371 F12

LTC4371

DA GA SA V

SS

M2*

M3*

M1

V

A

V

OUT

R

DA

20k

82V

*M2, M3: BSP135 (600V) DEPLETION NMOS