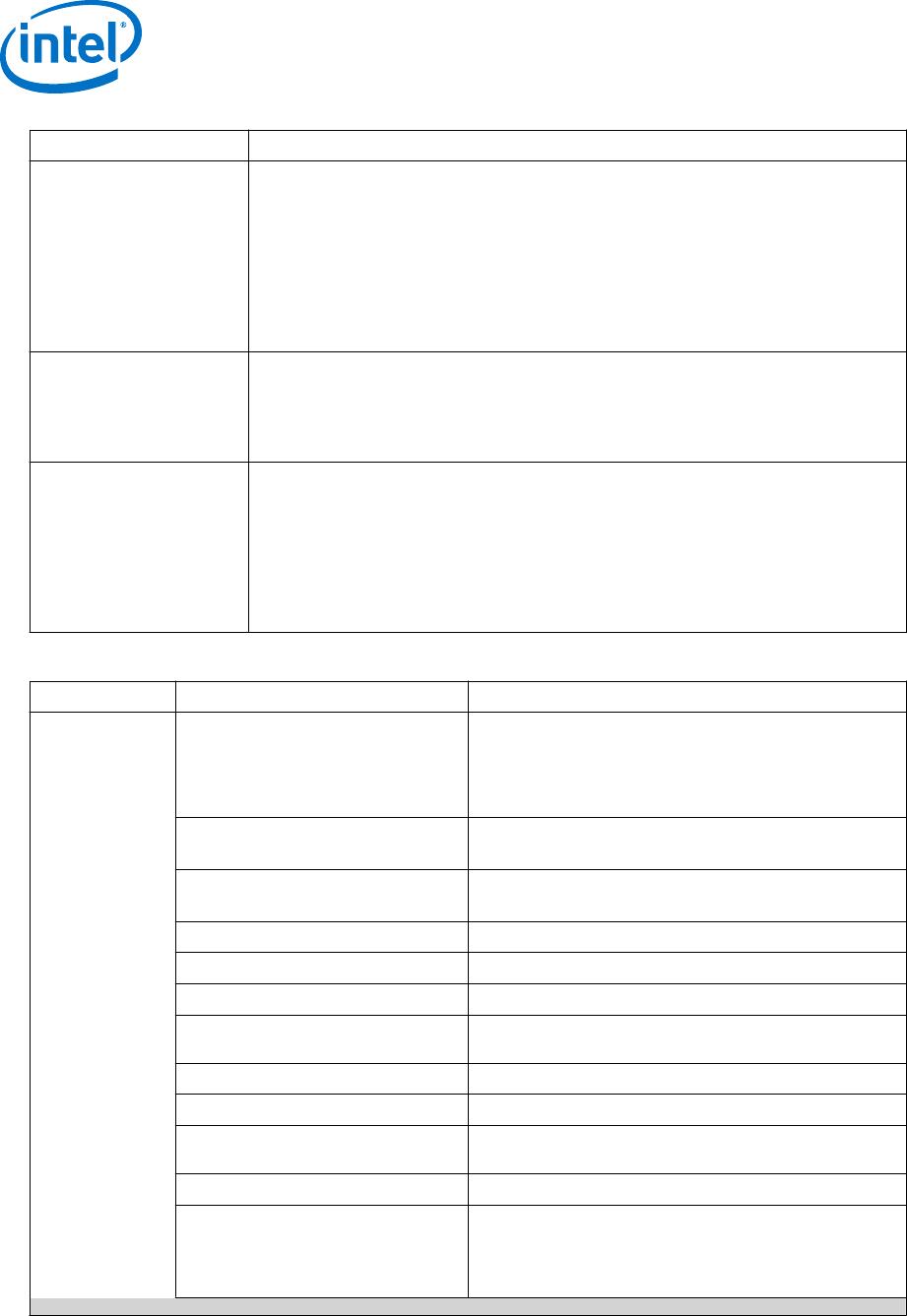

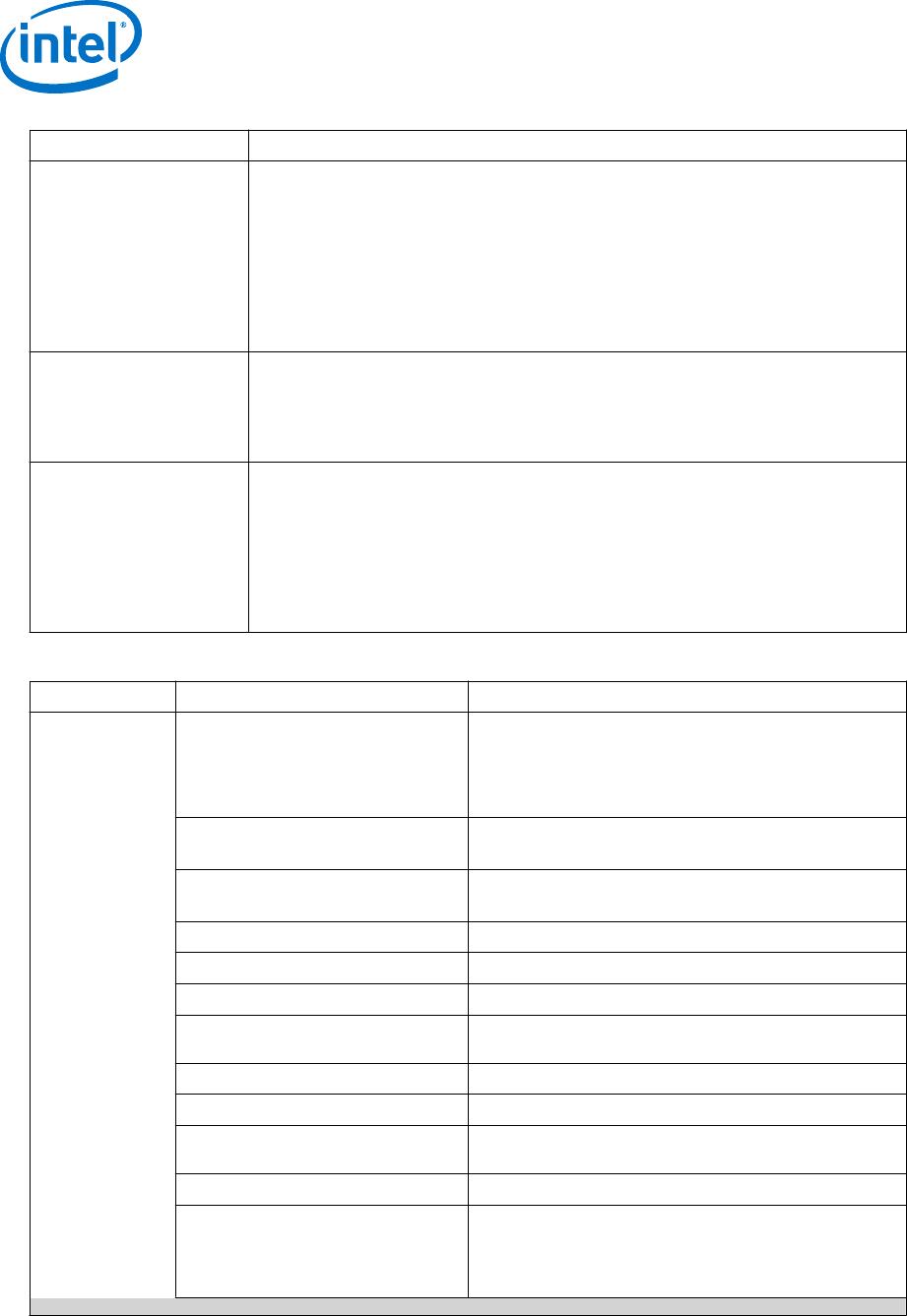

Feature Description

Configuration • Dedicated Secure Device Manager

• Software programmable device configuration

• Serial and parallel flash interface

• Configuration via protocol (CvP) using PCI Express Gen1/Gen2/Gen3

• Fine-grained partial reconfiguration of core fabric

• Dynamic reconfiguration of transceivers and PLLs

• Comprehensive set of security features including AES-256, SHA-256/384, and

ECDSA-256/384 accelerators, and multi-factor authentication

• Physically Unclonable Function (PUF) service

Packaging • Intel Embedded Multi-die Interconnect Bridge (EMIB) packaging technology

• Multiple devices with identical package footprints allows seamless migration across

different device densities

• 1.0 mm ball-pitch FBGA packaging

• Lead and lead-free package options

Software and tools • Intel Quartus Prime Pro Edition design suite with new compiler and Hyper-Aware design

flow

• Fast Forward compiler to allow HyperFlex architecture performance exploration

• Transceiver toolkit

• Platform designer integration tool

• DSP Builder advanced blockset

• OpenCL

™

support

• SoC Embedded Design Suite (EDS)

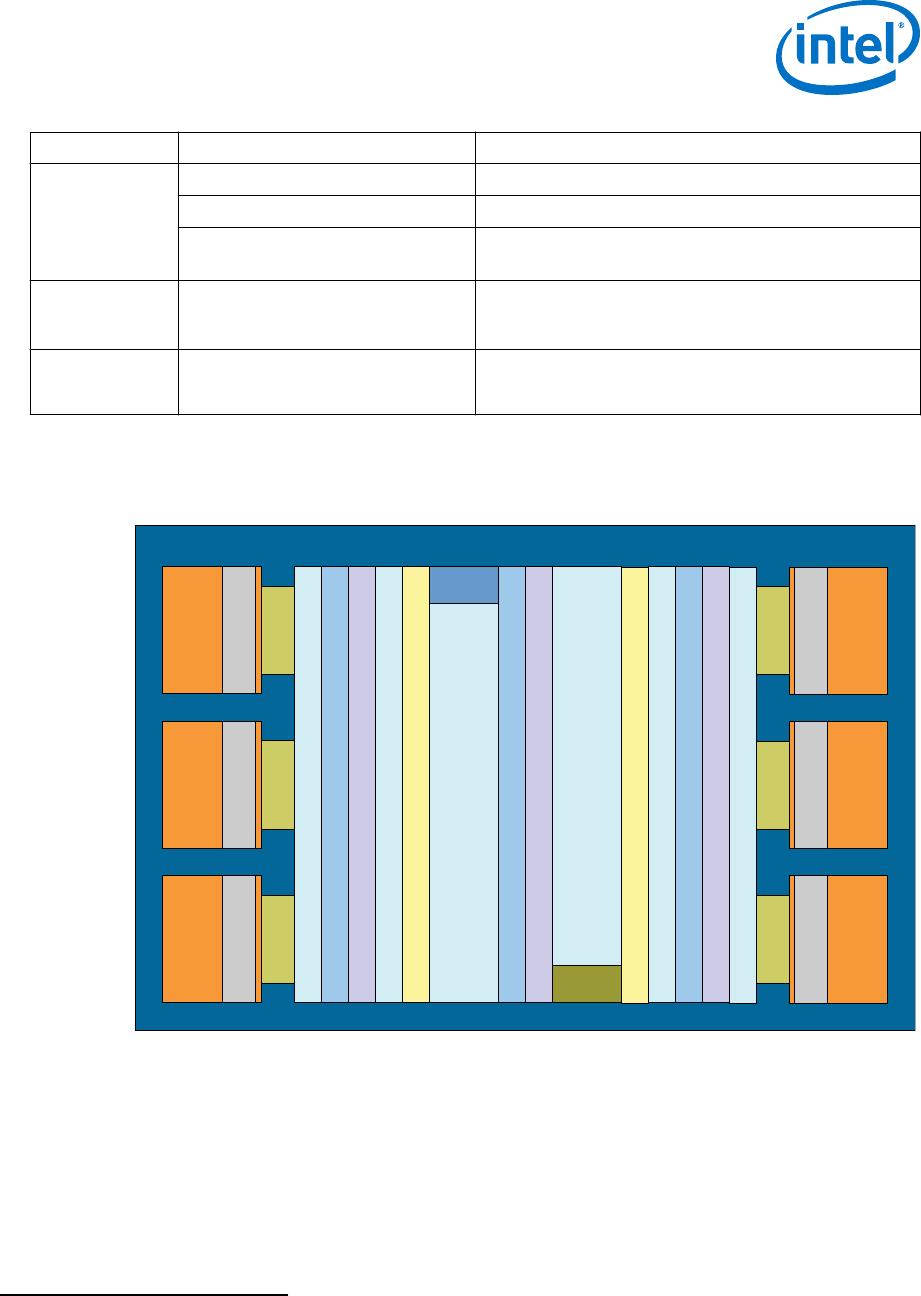

Table 3. Intel Stratix 10 SoC Specific Device Features

SoC Subsystem Feature Description

Hard Processor

System

Multi-processor unit (MPU) core • Quad-core ARM Cortex-A53 MPCore processor with ARM

CoreSight debug and trace technology

• Scalar floating-point unit supporting single and double

precision

• ARM NEON media processing engine for each processor

System Controllers • System Memory Management Unit (SMMU)

• Cache Coherency Unit (CCU)

Layer 1 Cache • 32 KB L1 instruction cache with parity

• 32 KB L1 data cache with ECC

Layer 2 Cache • 1 MB Shared L2 Cache with ECC

On-Chip Memory • 256 KB On-Chip RAM

Direct memory access (DMA) controller • 8-Channel DMA

Ethernet media access controller

(EMAC)

• Three 10/100/1000 EMAC with integrated DMA

USB On-The-Go controller (OTG) • 2 USB OTG with integrated DMA

UART controller • 2 UART 16550 compatible

Serial Peripheral Interface (SPI)

controller

• 4 SPI

I

2

C controller • 5 I

2

C controllers

SD/SDIO/MMC controller • 1 eMMC version 4.5 with DMA and CE-ATA support

• SD, including eSD, version 3.0

• SDIO, including eSDIO, version 3.0

• CE-ATA - version 1.1

continued...

1. Intel

®

Stratix

®

10 GX/SX Device Overview

S10-OVERVIEW | 2018.08.08

Stratix 10 GX/SX Device Overview

10