Each I/O bank contains 48 general purpose I/Os and a high-efficiency hard memory

controller capable of supporting many different memory types, each with different

performance capabilities. The hard memory controller is also capable of being

bypassed and replaced by a soft controller implemented in the user logic. The I/Os

each have a hardened double data rate (DDR) read/write path (PHY) capable of

performing key memory interface functionality such as:

• Read/write leveling

• FIFO buffering to lower latency and improve margin

• Timing calibration

• On-chip termination

The timing calibration is aided by the inclusion of hard microcontrollers based on

Intel’s Nios

®

II technology, specifically tailored to control the calibration of multiple

memory interfaces. This calibration allows the Intel Stratix 10 device to compensate

for any changes in process, voltage, or temperature either within the Intel Stratix 10

device itself, or within the external memory device. The advanced calibration

algorithms ensure maximum bandwidth and robust timing margin across all operating

conditions.

Table 10. External Memory Interface Performance

The listed speeds are for the 1-rank case.

Interface Controller Type Performance

DDR4 Hard 2666 Mbps

DDR3 Hard 2133 Mbps

QDRII+ Soft 1,100 Mtps

QDRII+ Xtreme Soft 1,266 Mtps

QDRIV Soft 2,133 Mtps

RLDRAM III Soft 2400 Mbps

RLDRAM II Soft 533 Mbps

In addition to parallel memory interfaces, Intel Stratix 10 devices support serial

memory technologies such as the Hybrid Memory Cube (HMC). The HMC is supported

by the Intel Stratix 10 high-speed serial transceivers, which connect up to four HMC

links, with each link running at data rates of 15 Gbps (HMC short reach specification).

Intel Stratix 10 devices also feature general purpose I/Os capable of supporting a wide

range of single-ended and differential I/O interfaces. LVDS rates up to 1.6 Gbps are

supported, with each pair of pins having both a differential driver and a differential

input buffer. This enables configurable direction for each LVDS pair.

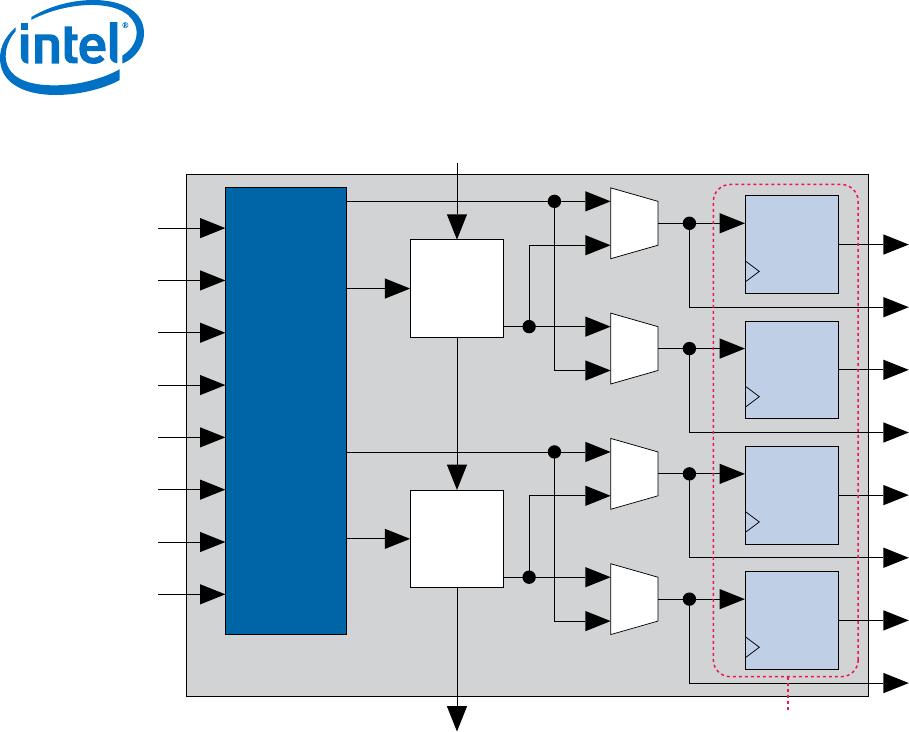

1.13. Adaptive Logic Module (ALM)

Intel Stratix 10 devices use a similar adaptive logic module (ALM) as the previous

generation Arria 10 and Stratix V FPGAs, allowing for efficient implementation of logic

functions and easy conversion of IP between the devices.

The ALM block diagram shown in the following figure has eight inputs with a

fracturable look-up table (LUT), two dedicated embedded adders, and four dedicated

registers.

1. Intel

®

Stratix

®

10 GX/SX Device Overview

S10-OVERVIEW | 2018.08.08

Stratix 10 GX/SX Device Overview

23