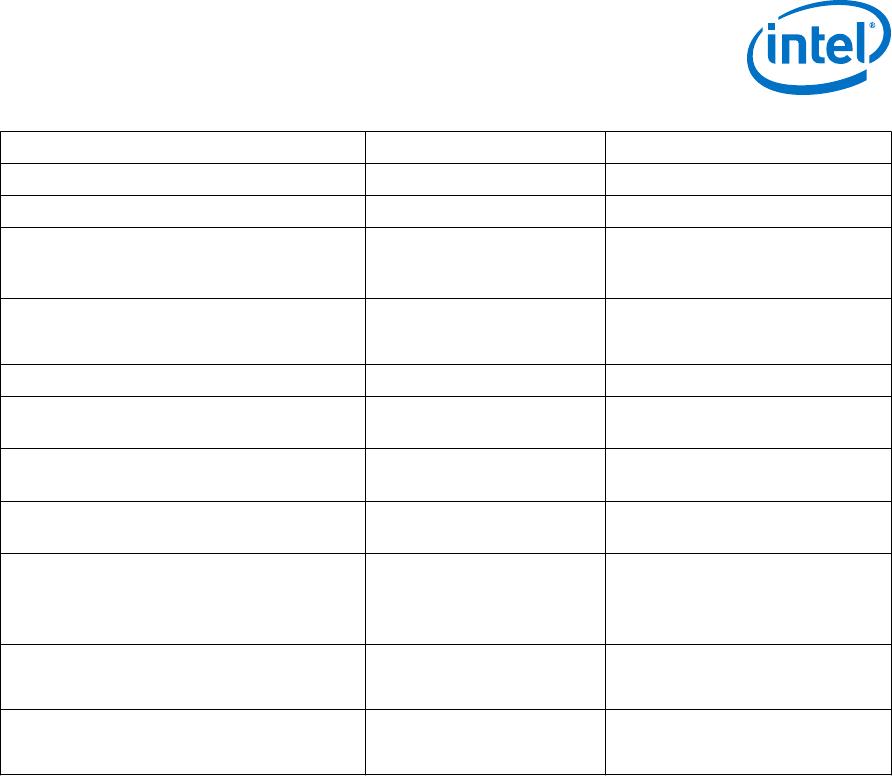

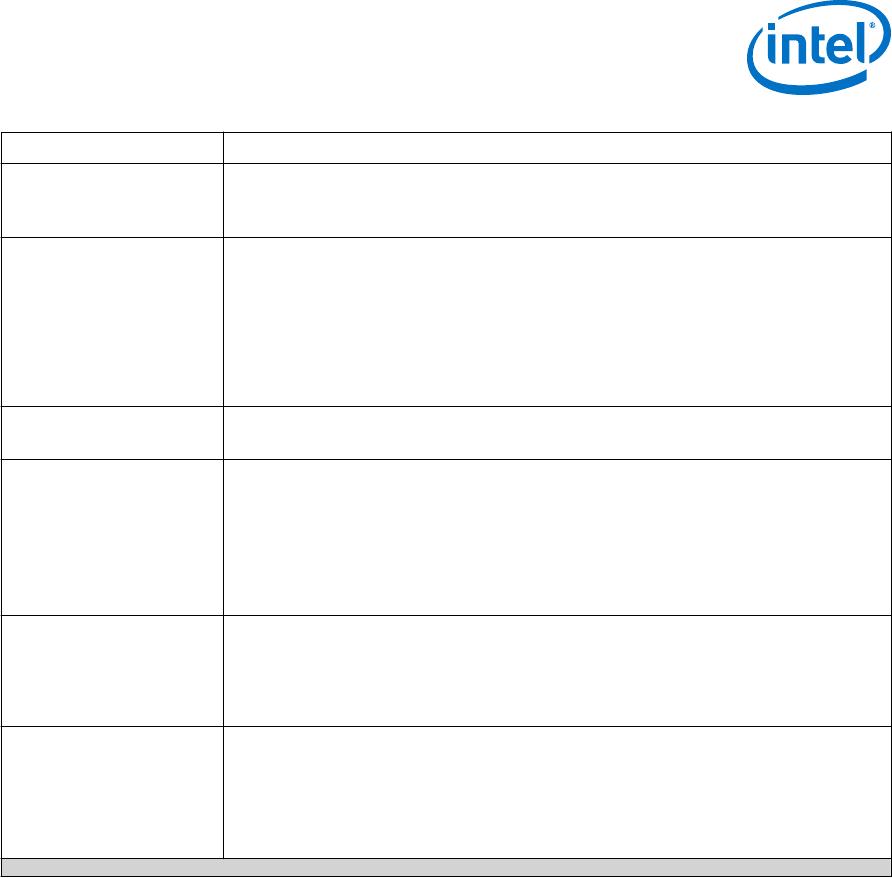

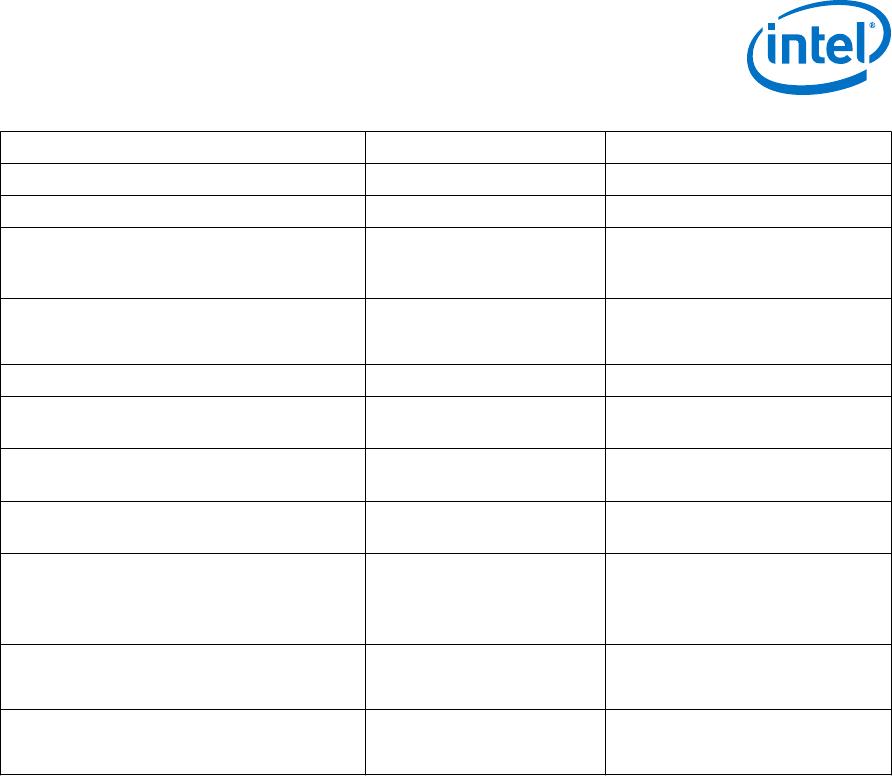

Feature Stratix V FPGAs Intel Stratix 10 FPGAs and SoCs

Logic density 952 KLE (monolithic) 5,500 KLE (monolithic)

Embedded memory (M20K) 52 Mbits 229 Mbits

18x19 multipliers 3,926

Note: Multiplier is 18x18 in

Stratix V devices.

11,520

Note: Multiplier is 18x19 in Intel

Stratix 10 devices.

Floating point DSP capability Up to 1 TFLOP, requires soft

floating point adder and

multiplier

Up to 10 TFLOPS, hard IEEE 754

compliant single precision floating

point adder and multiplier

Maximum transceivers 66 96

Maximum transceiver data rate (chip-to-

chip)

28.05 Gbps 28.3 Gbps L-Tile

28.3 Gbps H-Tile

Maximum transceiver data rate (backplane) 12.5 Gbps 12.5 Gbps L-Tile

28.3 Gbps H-Tile

Hard memory controller None DDR4 @ 1333 MHz/2666 Mbps

DDR3 @ 1067 MHz/2133 Mbps

Hard protocol IP PCIe Gen3 x8 (up to 4

instances)

PCIe Gen3 x16 (up to 4 instances)

SR-IOV (4 physical functions / 2k

virtual functions) on H-Tile devices

10GBASE-KR/40GBASE-KR4 FEC

Core clocking and PLLs Global, quadrant and regional

clocks supported by fractional-

synthesis fPLLs

Programmable clock tree synthesis

supported by fractional synthesis

fPLLs and integer IO PLLs

Register state readback and writeback Not available Non-destructive register state

readback and writeback for ASIC

prototyping and other applications

These innovations result in the following improvements:

• Improved Core Logic Performance: The HyperFlex core architecture combined

with Intel’s 14-nm Tri-Gate technology allows Intel Stratix 10 devices to achieve

2X the core performance compared to the previous generation

• Lower Power: Intel Stratix 10 devices use up to 70% lower power compared to

the previous generation, enabled by 14-nm Intel Tri-Gate technology, the

HyperFlex core architecture, and optional power saving features built into the

architecture

• Higher Density: Intel Stratix 10 devices offer over five times the level of

integration, with up to 5,500K logic elements (LEs) in a monolithic fabric, over 229

Mbits of embedded memory blocks (M20K), and 11,520 18x19 multipliers

• Embedded Processing: Intel Stratix 10 SoCs feature a Quad-Core 64-bit ARM

Cortex-A53 processor optimized for power efficiency and software compatible with

previous generation Arria and Cyclone SoC devices

• Improved Transceiver Performance: With up to 96 transceiver channels

implemented in heterogeneous 3D SiP transceiver tiles, Intel Stratix 10 GX and SX

devices support data rates up to 28.3 Gbps chip-to-chip and 28.3 Gbps across the

backplane with signal conditioning circuits capable of equalizing over 30 dB of

system loss

• Improved DSP Performance: The variable precision DSP block in Intel Stratix

10 devices features hard fixed and floating point capability, with up to 10

TeraFLOPS IEEE754 single-precision floating point performance

1. Intel

®

Stratix

®

10 GX/SX Device Overview

S10-OVERVIEW | 2018.08.08

Stratix 10 GX/SX Device Overview

7