AMIS−30660

http://onsemi.com

4

FUNCTIONAL DESCRIPTION

Operating Modes

The behavior of AMIS−30660 under various conditions is

illustrated in Table 5 below. In case the device is powered,

one of two operating modes can be selected through Pin S.

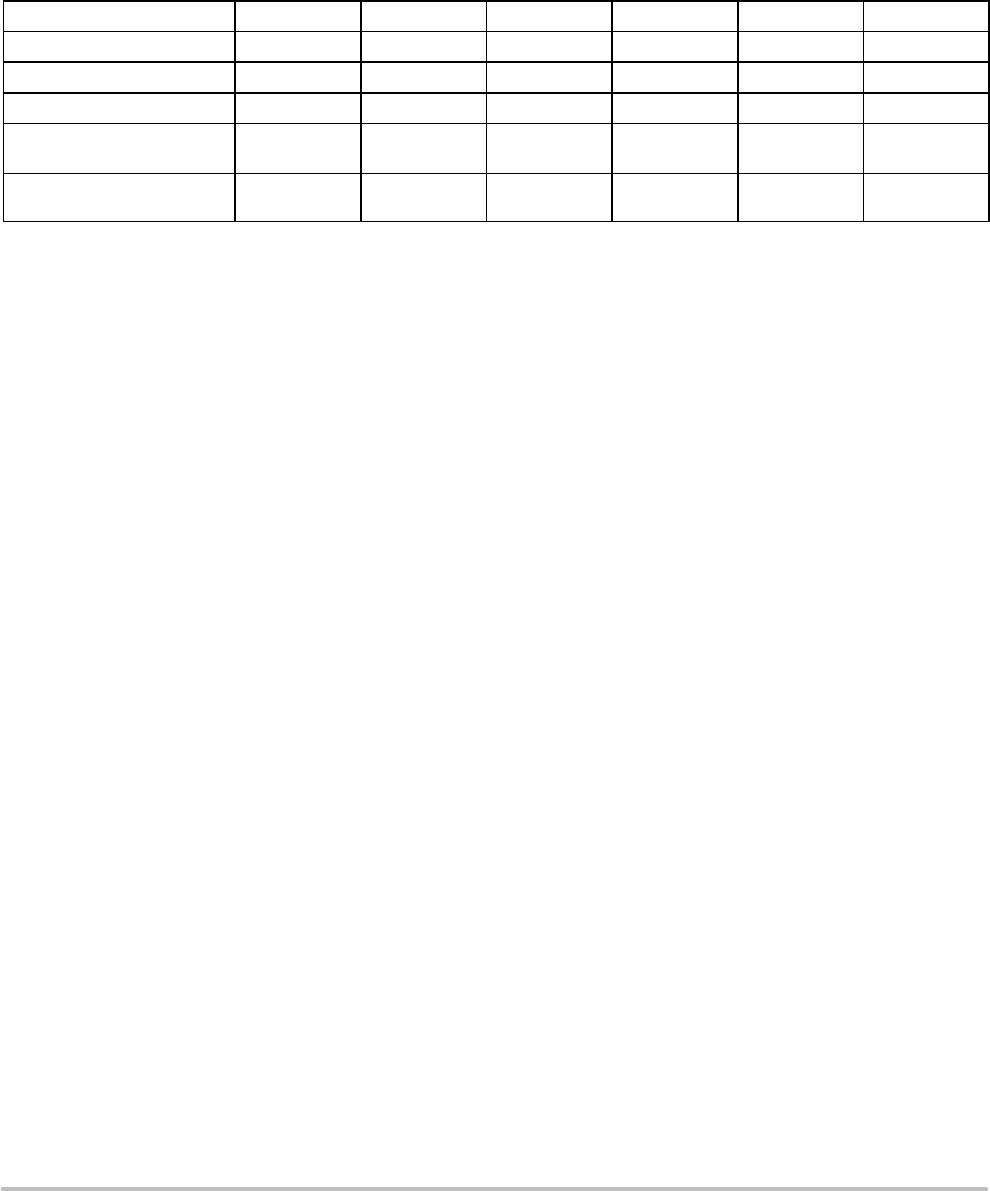

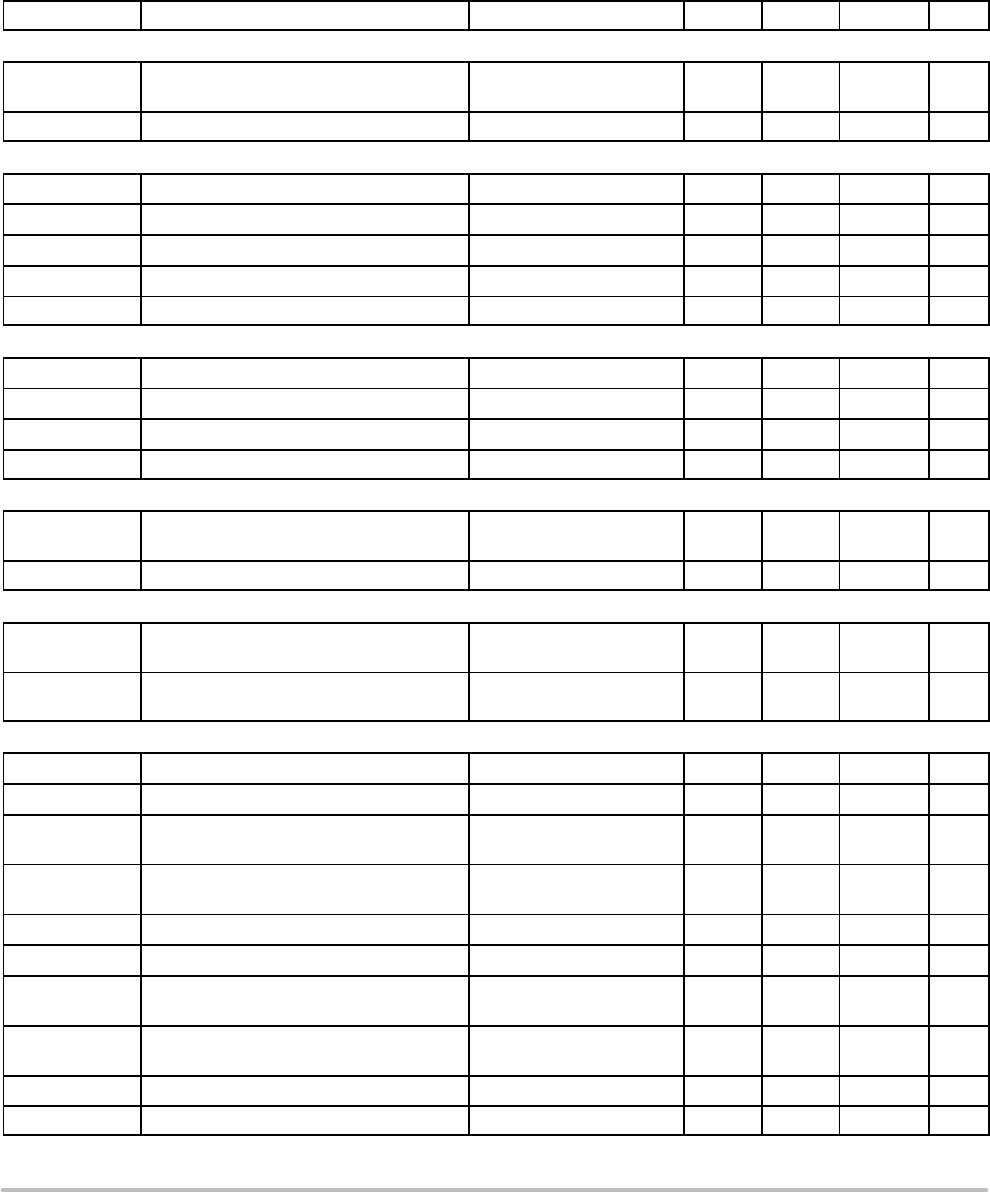

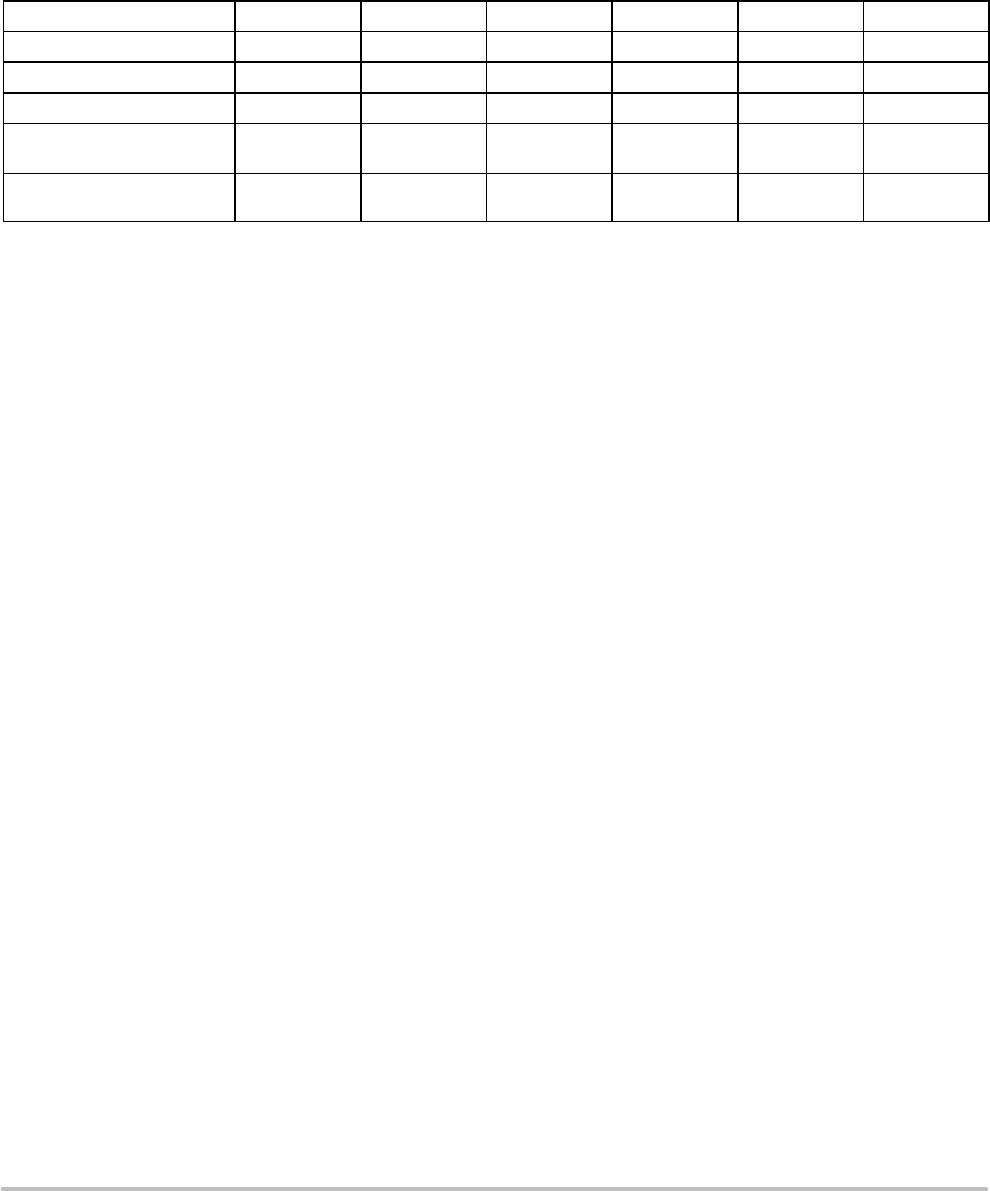

Table 5. FUNCTIONAL TABLE OF AMIS−30660 (X = DON’T CARE)

VCC Pin TxD Pin S Pin CANH Pin CANL Bus State Pin RxD

4.75 V to 5.25 V 0 0 (or Floating) High Low Dominant 0

4.75 V to 5.25 V X 1 V

CC

/ 2 V

CC

/ 2 Recessive 1

4.75 V to 5.25 V 1 (or Floating) X V

CC

/ 2 V

CC

/ 2 Recessive 1

V

CC

< PORL (Unpowered) X X 0 V < CANH

< V

CC

0 V < CANL <

V

CC

Recessive 1

PORL < V

CC

< 4.75 V > 2 V X 0 V < CANH

< V

CC

0 V < CANL <

V

CC

Recessive 1

High−Speed Mode

If Pin S is pulled low (or left floating), the transceiver is

in its high−speed mode and is able to communicate via the

bus lines. The signals are transmitted and received to the

CAN controller via the Pins TxD and RxD. The slopes on the

bus line outputs are optimized to give extremely low

electromagnetic emissions.

Silent Mode

In silent mode, the transmitter is disabled. All other IC

functions continue to operate. The silent mode is selected by

connecting Pin S to V

CC

and can be used to prevent network

communication from being blocked, due to a CAN

controller which is out of control.

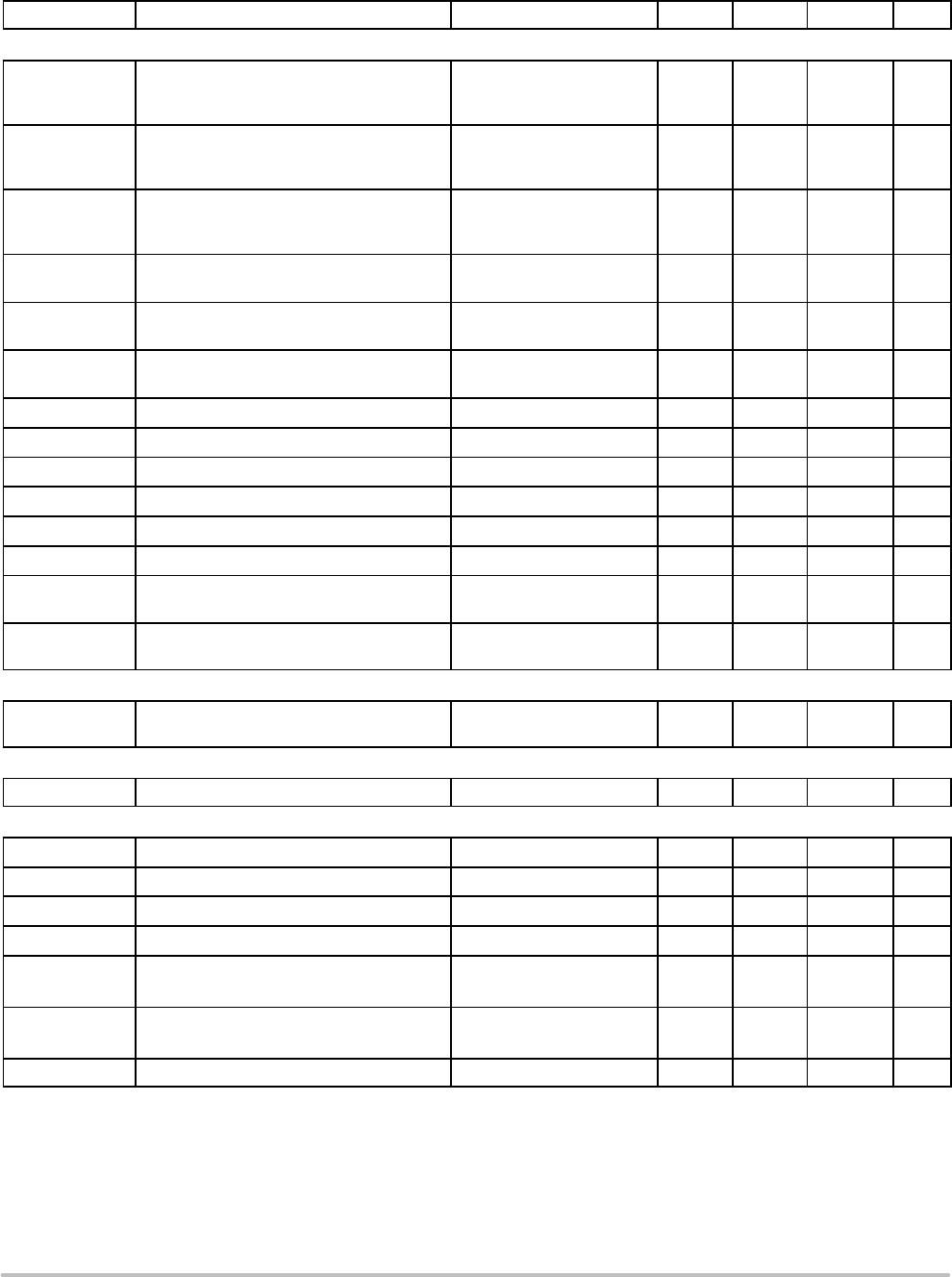

Overtemperature Detection

A thermal protection circuit protects the IC from damage

by switching off the transmitter if the junction temperature

exceeds a value of approximately 160°C. Because the

transmitter dissipates most of the power, the power

dissipation and temperature of the IC is reduced. All other

IC functions continue to operate. The transmitter off−state

resets when Pin TxD goes high. The thermal protection

circuit is particularly necessary when a bus line

short−circuits.

TxD Dominant Time−out Function

A TxD dominant time−out timer circuit prevents the bus

lines from being driven to a permanent dominant state

(blocking all network communication) if Pin TxD is forced

permanently low by a hardware and/or software application

failure. The timer is triggered by a negative edge on pin TxD.

If the duration of the low−level on Pin TxD exceeds the

internal timer value t

dom

, the transmitter is disabled, driving

the bus into a recessive state. The timer is reset by a positive

edge on Pin TxD.

Fail−Safe Features

A current−limiting circuit protects the transmitter output

stage from damage caused by an accidental short−circuit to

either positive or negative supply voltage, although power

dissipation increases during this fault condition.

The Pins CANH and CANL are protected from

automotive electrical transients (according to “ISO 7637”;

see Figure 3). Pin TxD is pulled high internally should the

input become disconnected.