1

Power Factor Correction Controllers

ISL6730A, ISL6730B, ISL6730C, ISL6730D

The ISL6730A, ISL6730B, ISL6730C, ISL6730D are active

Power Factor Correction (PFC) controller ICs that use a boost

topology. The controllers are suitable for AC/DC power

systems, up to 2kW and over the universal line input.

The ISL6730A, ISL6730B, ISL6730C, ISL6730D operate in

Continuous Conduction Mode (CCM). Accurate input current

shaping is achieved with a current error amplifier. A patent

pending breakthrough negative capacitance technology

minimizes zero crossing distortion and reduces the magnetic

components size. The small external components result in a

low cost design without sacrificing performance.

The internally clamped 12.5V gate driver delivers 1.5A peak

current to the external power MOSFET. The ISL6730A,

ISL6730B, ISL6730C, ISL6730D provide a highly reliable

system that is fully protected. Protection features include

cycle-by-cycle overcurrent, over power limit, over-temperature,

input brownout, output overvoltage and undervoltage

protection.

The ISL6730A, ISL6730B provide excellent power efficiency

and transitions into a power saving skip mode during light load

conditions, thus improving efficiency automatically. The

ISL6730A, ISL6730B, ISL6730C, ISL6730D can be shut down

by pulling the FB pin below 0.5V or grounding the BO pin. The

ISL6730C, ISL6730D have no skip mode.

Two switching frequency options are provided. The ISL6730B,

ISL6730D switch at 62kHz, and the ISL6730A, ISL6730C

switch at 124kHz.

Features

• Reduce component size requirements

- Enables smaller, thinner AC/DC adapters

- Choke and cap size can be reduced

- Lower cost of materials

• Excellent power factor over line and load regulation

- Internal current compensation

- CCM Mode with Patent pending IP for smaller EMI filter

•Better light load efficiency

- Automatic pulse skipping

- Programmable or automatic shutdown

• High reliable design

- Cycle-by-cycle current limit

- Input average power limit

- OVP and OTP protection

- Input brownout protection

• Small 10 Ld MSOP package

Applications

• Desktop computer AC/DC adaptor

• Laptop computer AC/DC adaptor

•TV AC/DC power supply

•AC/DC brick converters

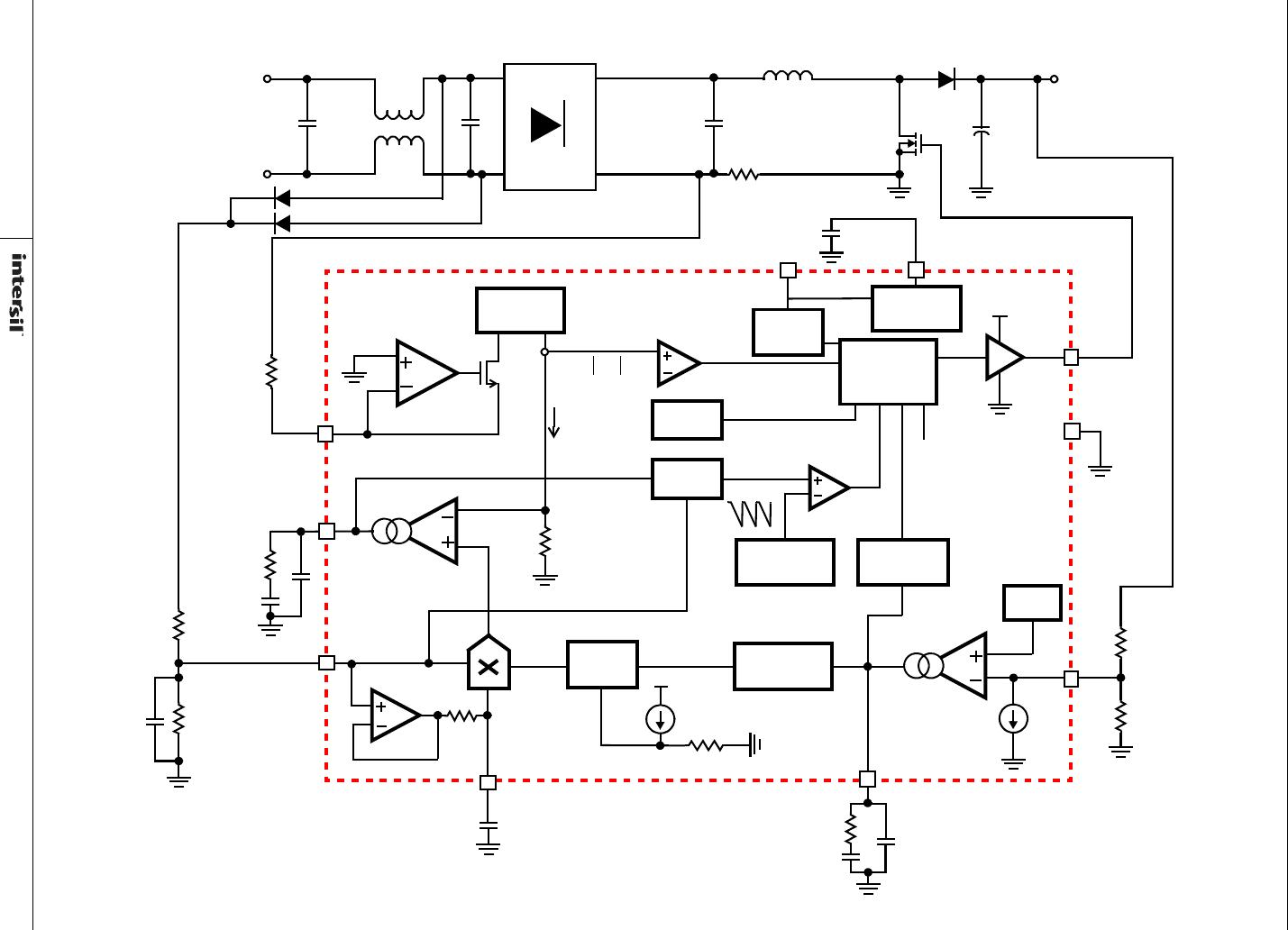

FIGURE 1. TYPICAL APPLICATION FIGURE 2. PFC EFFICIENCY

+

ISL6730

VCC

ISEN

ICOMP

VIN

GATE

GND

FB

BO VREG

COMP

V

LINE

V

OUT

V

I

OUTPUT POWER (W)

EFFICIENCY (%)

ISL6730C

ISL6730A, SKIP

100

95

60

65

70

90

85

80

75

0 20 40 60 80 100

TABLE 1. KEY DIFFERENCES IN FAMILY OF ISL6730

VERSION ISL6730A ISL6730B ISL6730C ISL6730D

Switching Frequency 124kHz 62kHz 124kHz 62kHz

Skip Mode Yes-Fixed Yes-Fixed No No

August 8, 2013

FN8258.1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774

| Copyright Intersil Americas LLC 2013. All Rights Reserved

Intersil (and design) is a trademark owned by Intersil Corporation or one of its subsidiaries.

All other trademarks mentioned are the property of their respective owners.