ISL6730A, ISL6730B, ISL6730C, ISL6730D

12

FN8258.1

August 8, 2013

harmonic distortion minimum, it is desirable to set the control

bandwidth much lower than twice of the line frequency. The

recommended voltage loop bandwidth is 10Hz.

During start-up, the compensation capacitors and the charging

current from the error amplifier sets the input power increase

rate. Thus, soft-start is achieved.

The COMP is discharged during shutdown and fault conditions.

Light Load Efficiency Enhancement

For PC, adaptor and TV applications, it is desirable to achieve

high efficiency at light load conditions and low standby current.

The ISL6730A, ISL6730B can enter light load efficiency mode

automatically.

The voltage error amplifier output, COMP, is an indicator of the

average input power level. The controller compares the V(COMP)

and V(SKIP). If V(COMP)-1V is less than V(SKIP)*0.25, the PFC

controller stops gate switching and the COMP pin voltage is

clamped to V(SKIP)+0.6V. ISL6730A/B use a fixed V(SKIP), which

is 1.4V; for ISL6730C/D, the SKIP function are disabled.

The controller exits skip mode when V

FB

drops to 88% (typical) of

the reference voltage or when the sensed returned current

exceeds 29µA.

Protection Circuits

Input Brownout, BO Protection

Brownout occurs when there is a drop in the line voltage. The BO

pin is a dual function pin. The BO pin detects the brownout

condition and shuts down the gate driver and controller. During

normal operation, the BO pin is used to compensate the effect of

the input line voltage change on the voltage loop. To keep the

harmonic distortion low, the corner frequency formed by the R

BO

and C

BO

should be lower than 6Hz.

The BO pin is the output of the average voltage of the rectified

voltage. The PFC controller is turned off when the BO pin drops

below 0.4V. This protects the PFC power stage to enable

operation at or below brownout condition for long periods of

time. The controller resumes operation when the BO pin returns

to 0.5V.

The BO pin is usually connected to GND through a capacitor, C

BO

.

To avoid distortion on the VIN pin, select C

BO

so that:

Overcurrent Protection

The peak current limiting function prevents the inductor from

saturation. The gate driver turns off when the current goes above

the current limit.

Overpower Protection

The overpower protection is implemented by limiting the COMP

pin voltage higher than 3.85V (typical).

Overvoltage Protection

If the voltage on the FB pin exceeds the reference voltage by about

4%, the gate driver is turned off. The controller resumes normal

operation after the FB pin drops below reference voltage.

Over-Temperature Protection

The ISL6730A, ISL6730B, ISL6730C, ISL6730D is protected

against over-temperature conditions. When the junction

temperature exceeds +160°C, the PWM shuts down. Normal

operation is resumed when the junction temperature decreases

below +135°C.

Application Guidelines

Layout Considerations

As in any high frequency switching converter, layout is very

important. Switching current from one power device to another

can generate voltage transients across the impedances of the

interconnecting bond wires and circuit traces. These

interconnecting impedances should be minimized by using wide,

short printed circuit traces. The critical components should be

located as close together as possible using ground plane

construction or single point grounding.

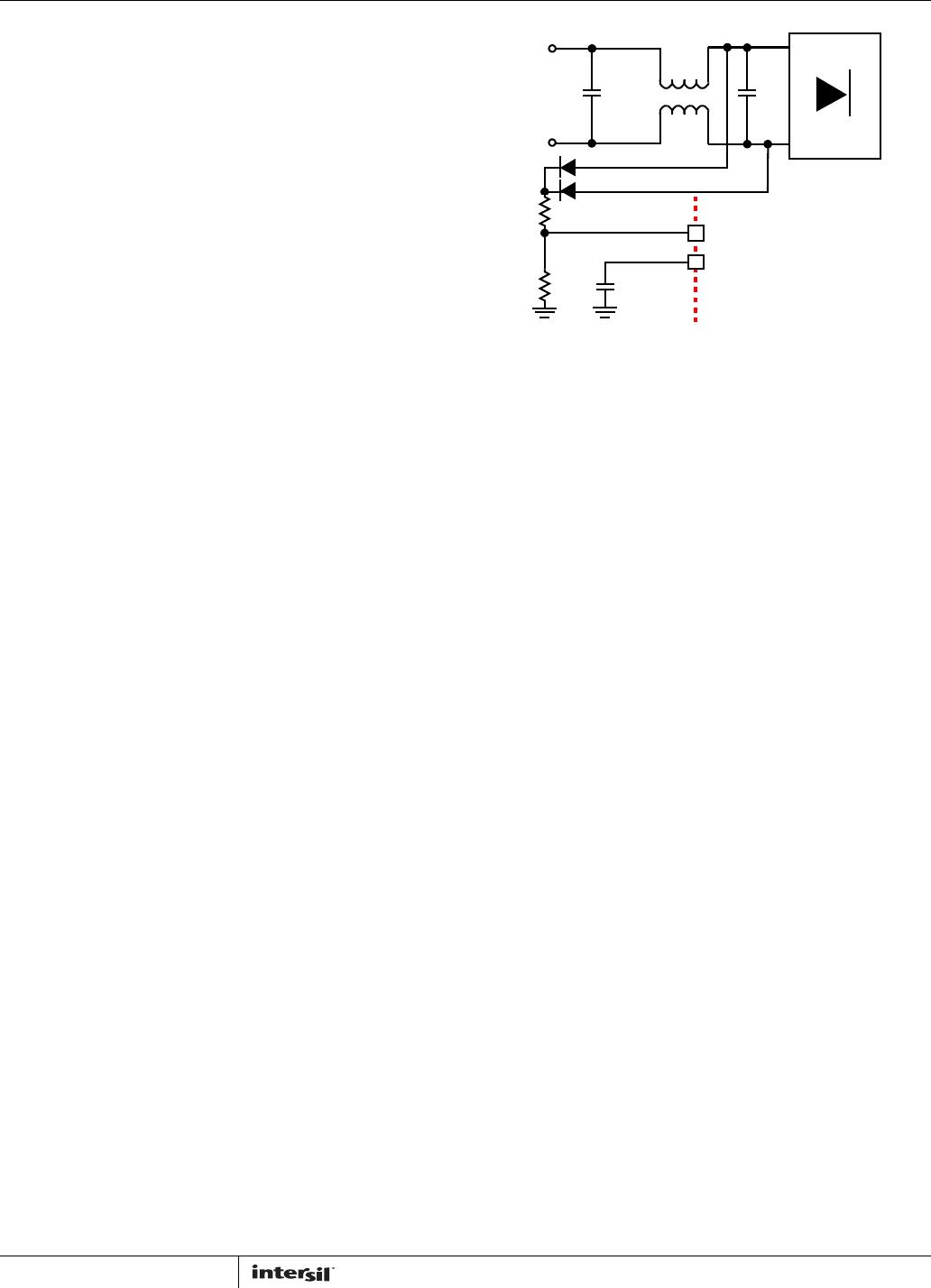

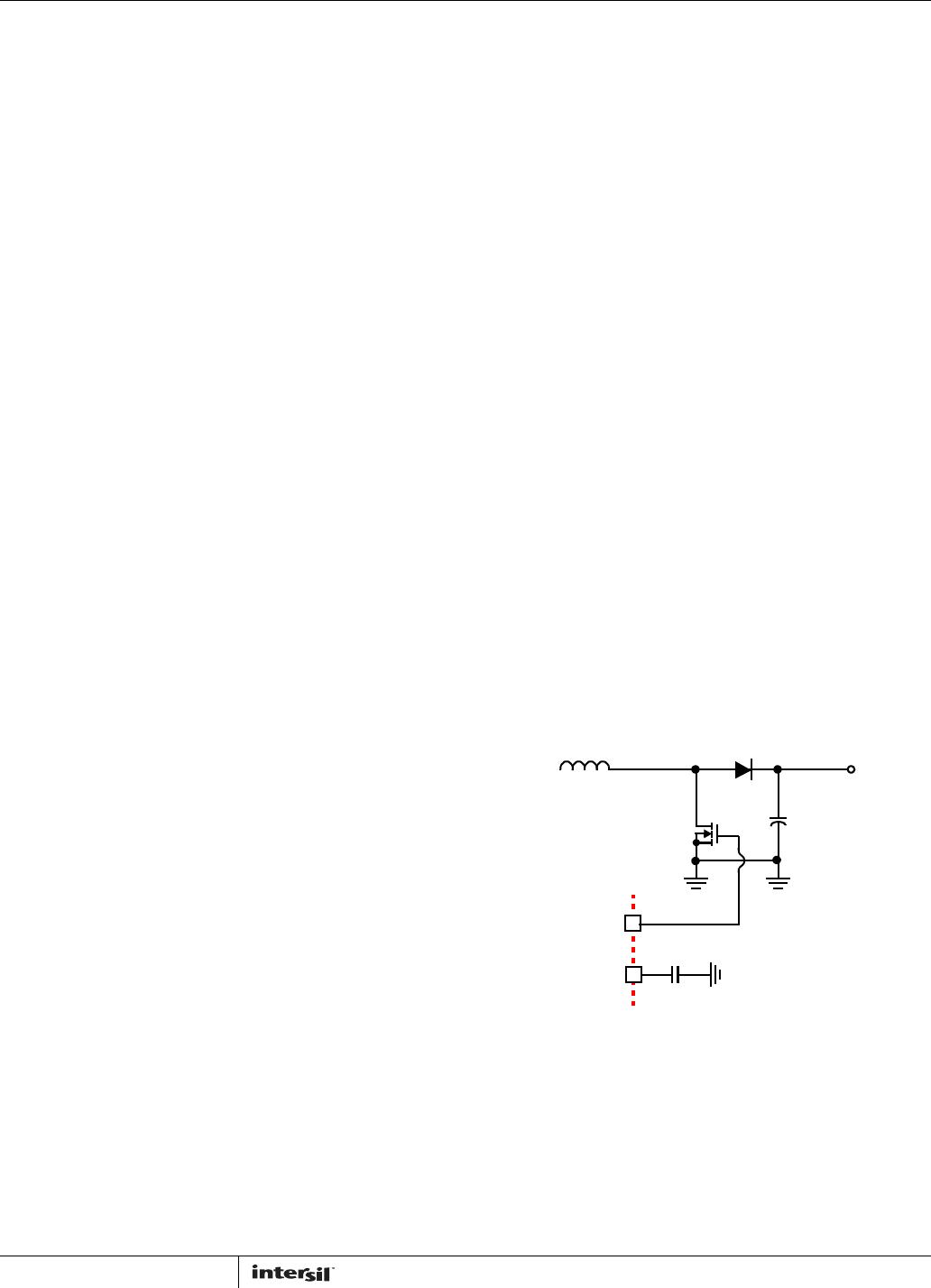

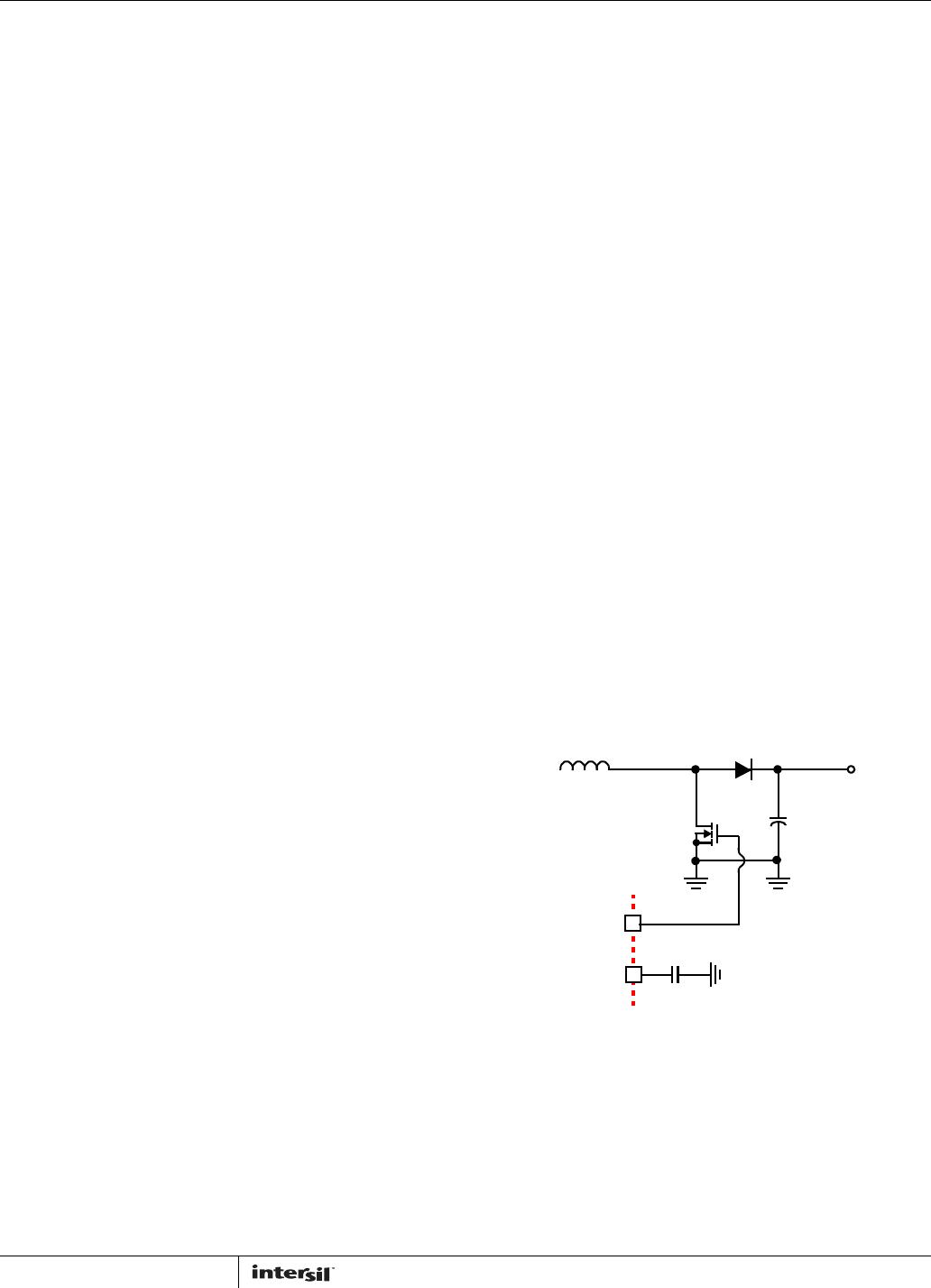

Figure 14 shows the critical power components; Q

1

, D and C

OUT

.

To minimize the voltage overshoot, the interconnecting wires

indicated by heavy lines should be part of the ground or the

power plane in a printed circuit board. The components shown in

Figure 14 should be located as close together as possible. Please

note that the capacitors C

VCC

and C

O

each represent numerous

physical capacitors. Locate the ISL6730A, ISL6730B, ISL6730C,

ISL6730D within 2 inches of the MOSFET, Q

1

. The circuit traces

for the MOSFETs’ gate and source connections from the

ISL6730A, ISL6730B, ISL6730C, ISL6730D must be sized to

handle up to 1.5A peak current.

Component Selection Guidelines

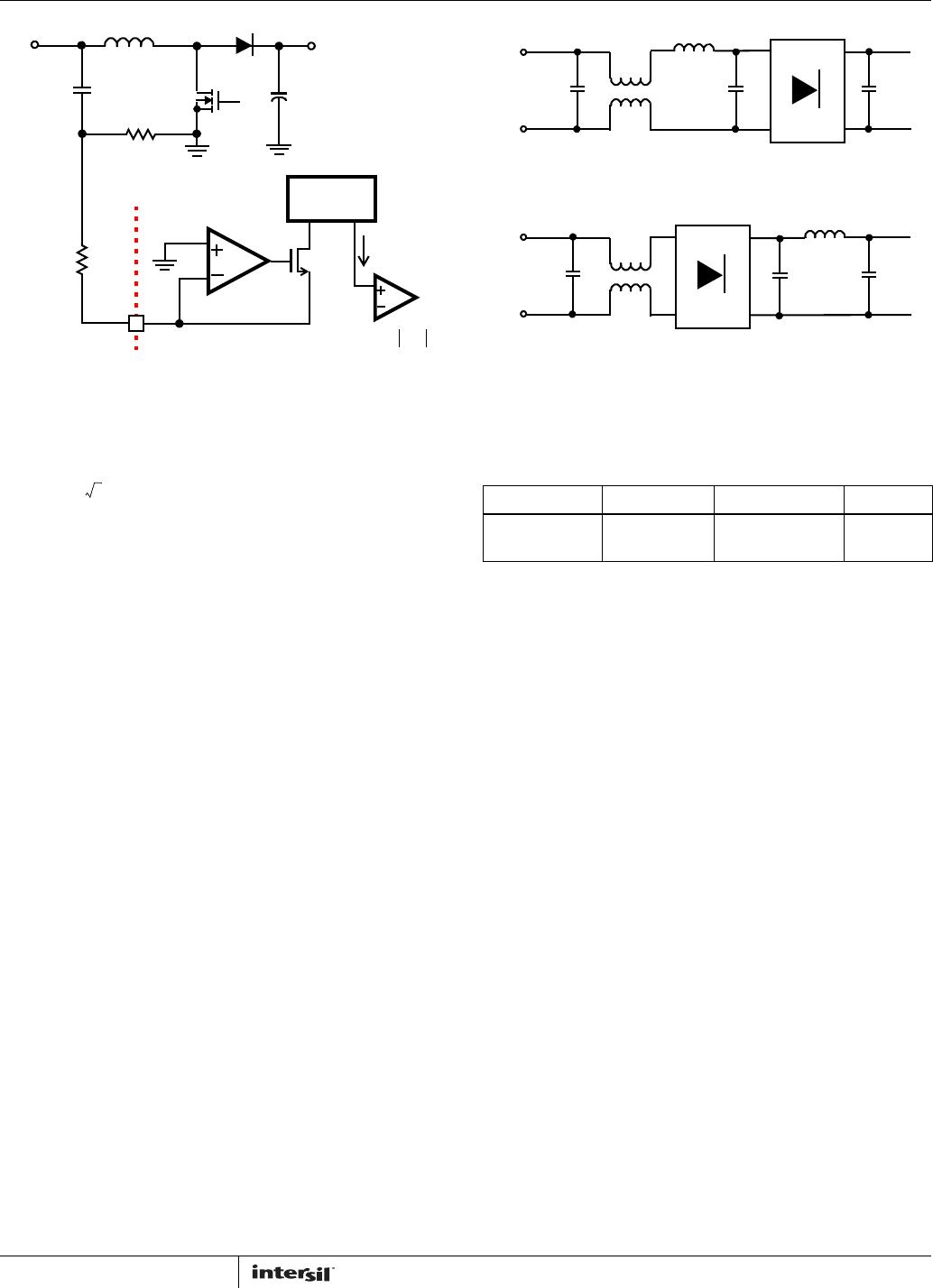

A 300W, universal input, PFC converter design is provided for

demonstration. The design method is for a continuous current

mode power factor correction boost converter with the

ISL6730B/D. The switching frequency is 62kHz.

FIGURE 14. CRITICAL CURRENT POWER COMPONENTS

Q

1

C

OUT

L

D

GATE

VCC

C

VCC