PCS Features

The Cyclone V core logic connects to the PCS through an 8, 10, 16, 20, 32, or 40 bit

interface, depending on the transceiver data rate and protocol. Cyclone V devices

contain PCS hard IP to support PCIe Gen1 and Gen2, Gbps Ethernet (GbE), Serial

RapidIO

®

(SRIO), and Common Public Radio Interface (CPRI).

Most of the standard and proprietary protocols from 614 Mbps to 6.144 Gbps are

supported.

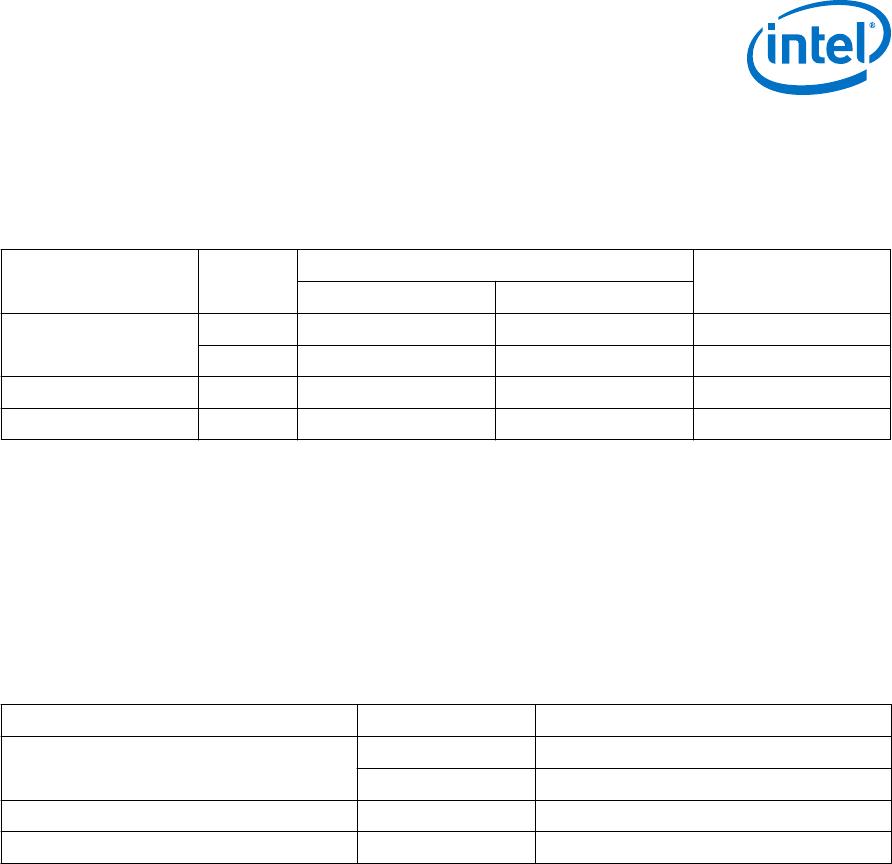

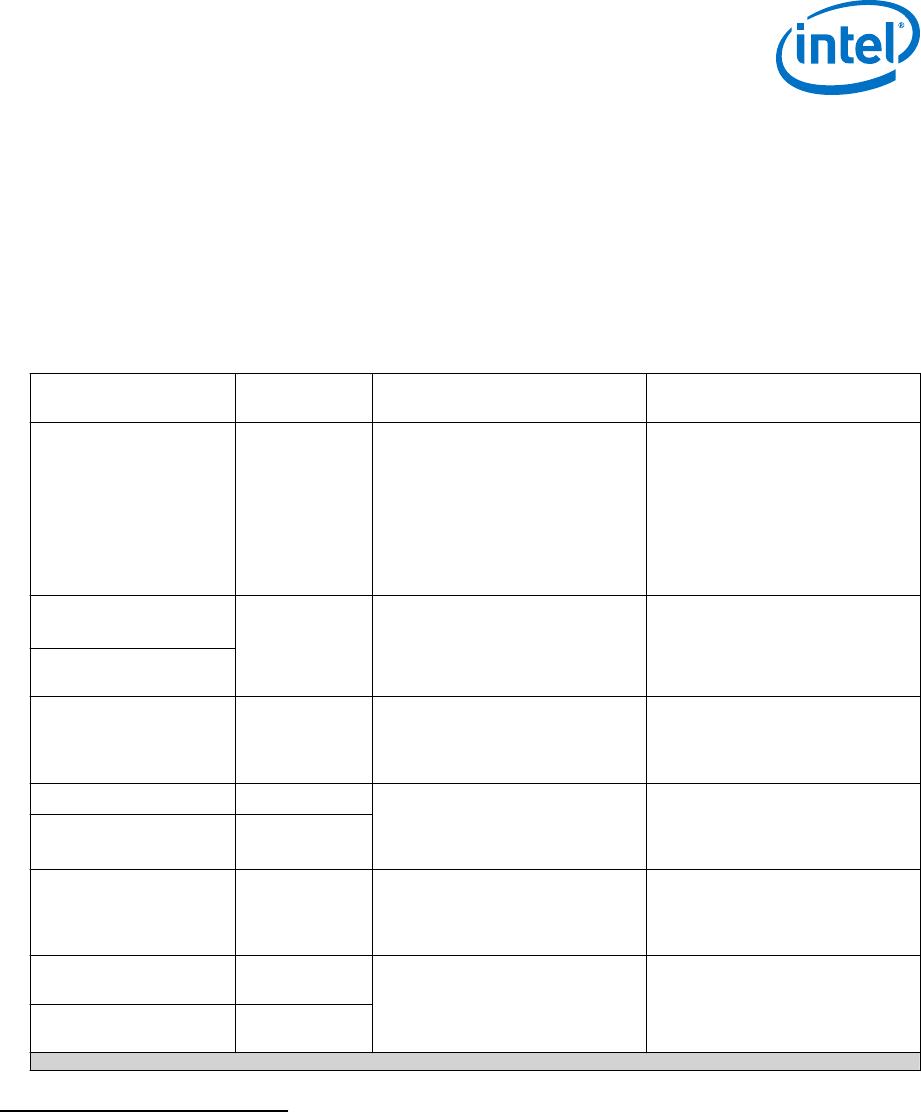

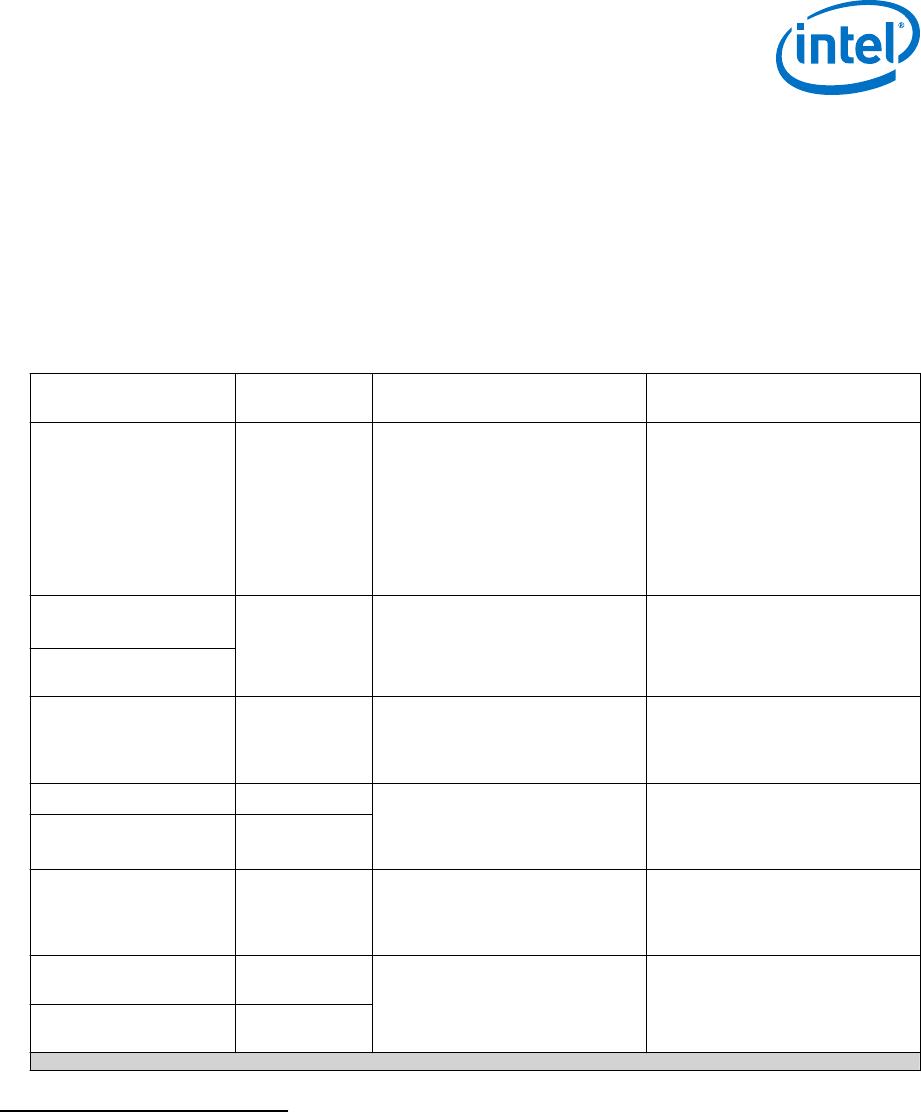

Table 23. Transceiver PCS Features for Cyclone V Devices

PCS Support Data Rates

(Gbps)

Transmitter Data Path Feature Receiver Data Path Feature

3-Gbps and 6-Gbps Basic 0.614 to 6.144 • Phase compensation FIFO

• Byte serializer

• 8B/10B encoder

• Transmitter bit-slip

• Word aligner

• Deskew FIFO

• Rate-match FIFO

• 8B/10B decoder

• Byte deserializer

• Byte ordering

• Receiver phase compensation

FIFO

PCIe Gen1

(x1, x2, x4)

2.5 and 5.0 • Dedicated PCIe PHY IP core

• PIPE 2.0 interface to the core

logic

• Dedicated PCIe PHY IP core

• PIPE 2.0 interface to the core

logic

PCIe Gen2

( x1, x2, x4)

(12)

GbE 1.25 • Custom PHY IP core with preset

feature

• GbE transmitter synchronization

state machine

• Custom PHY IP core with preset

feature

• GbE receiver synchronization

state machine

XAUI

(13)

3.125 • Dedicated XAUI PHY IP core

• XAUI synchronization state

machine for bonding four

channels

• Dedicated XAUI PHY IP core

• XAUI synchronization state

machine for realigning four

channels

HiGig 3.75

SRIO 1.3 and 2.1 1.25 to 3.125 • Custom PHY IP core with preset

feature

• SRIO version 2.1-compliant x2

and x4 channel bonding

• Custom PHY IP core with preset

feature

• SRIO version 2.1-compliant x2

and x4 deskew state machine

SDI, SD/HD, and 3G-SDI 0.27

(14)

, 1.485,

and 2.97

Custom PHY IP core with preset

feature

Custom PHY IP core with preset

feature

JESD204A 0.3125

(15)

to

3.125

continued...

(12)

PCIe Gen2 is supported for Cyclone V GT and ST devices. The PCIe Gen2 x4 support is

PCIe-compatible.

(13)

XAUI is supported through the soft PCS.

(14)

The 0.27-Gbps data rate is supported using oversampling user logic that you must implement

in the FPGA fabric.

(15)

The 0.3125-Gbps data rate is supported using oversampling user logic that you must

implement in the FPGA fabric.

Cyclone V Device Overview

CV-51001 | 2018.05.07

Cyclone V Device Overview

27