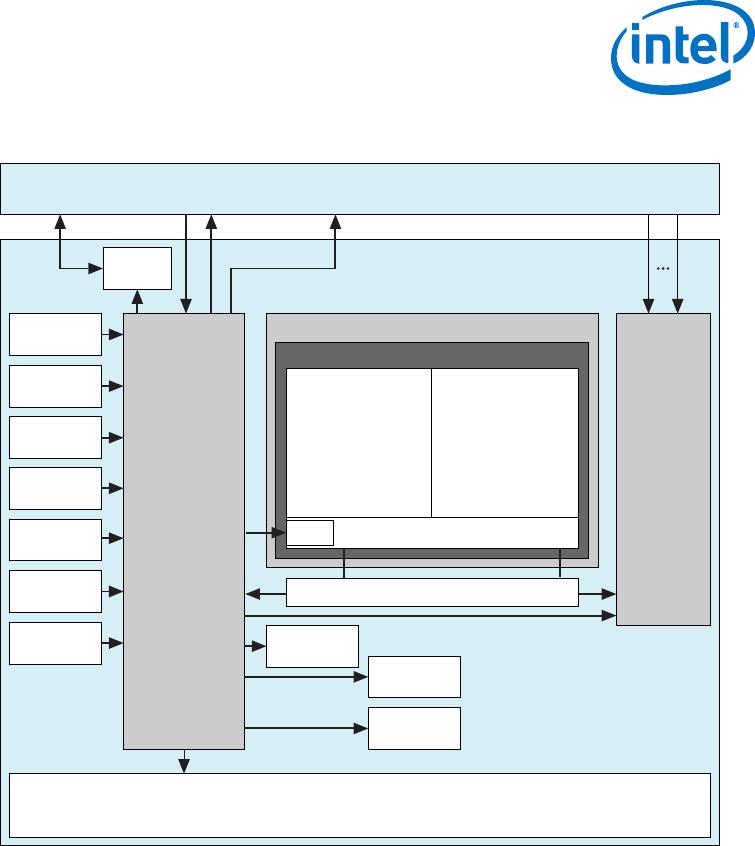

HPS–FPGA AXI Bridges

The HPS–FPGA bridges, which support the Advanced Microcontroller Bus Architecture

(AMBA

®

) Advanced eXtensible Interface (AXI

™

) specifications, consist of the following

bridges:

• FPGA-to-HPS AXI bridge—a high-performance bus supporting 32, 64, and 128 bit

data widths that allows the FPGA fabric to issue transactions to slaves in the HPS.

• HPS-to-FPGA AXI bridge—a high-performance bus supporting 32, 64, and 128 bit

data widths that allows the HPS to issue transactions to slaves in the FPGA fabric.

• Lightweight HPS-to-FPGA AXI bridge—a lower latency 32 bit width bus that allows

the HPS to issue transactions to slaves in the FPGA fabric. This bridge is primarily

used for control and status register (CSR) accesses to peripherals in the FPGA

fabric.

The HPS–FPGA AXI bridges allow masters in the FPGA fabric to communicate with

slaves in the HPS logic, and vice versa. For example, the HPS-to-FPGA AXI bridge

allows you to share memories instantiated in the FPGA fabric with one or both

microprocessors in the HPS, while the FPGA-to-HPS AXI bridge allows logic in the

FPGA fabric to access the memory and peripherals in the HPS.

Each HPS–FPGA bridge also provides asynchronous clock crossing for data transferred

between the FPGA fabric and the HPS.

HPS SDRAM Controller Subsystem

The HPS SDRAM controller subsystem contains a multiport SDRAM controller and DDR

PHY that are shared between the FPGA fabric (through the FPGA-to-HPS SDRAM

interface), the level 2 (L2) cache, and the level 3 (L3) system interconnect. The

FPGA-to-HPS SDRAM interface supports AMBA AXI and Avalon

®

Memory-Mapped

(Avalon-MM) interface standards, and provides up to six individual ports for access by

masters implemented in the FPGA fabric.

To maximize memory performance, the SDRAM controller subsystem supports

command and data reordering, deficit round-robin arbitration with aging, and

high-priority bypass features. The SDRAM controller subsystem supports DDR2, DDR3,

or LPDDR2 devices up to 4 Gb in density operating at up to 400 MHz (800 Mbps data

rate).

FPGA Configuration and Processor Booting

The FPGA fabric and HPS in the SoC are powered independently. You can reduce the

clock frequencies or gate the clocks to reduce dynamic power, or shut down the entire

FPGA fabric to reduce total system power.

You can configure the FPGA fabric and boot the HPS independently, in any order,

providing you with more design flexibility:

• You can boot the HPS independently. After the HPS is running, the HPS can fully or

partially reconfigure the FPGA fabric at any time under software control. The HPS

can also configure other FPGAs on the board through the FPGA configuration

controller.

• You can power up both the HPS and the FPGA fabric together, configure the FPGA

fabric first, and then boot the HPS from memory accessible to the FPGA fabric.

Cyclone V Device Overview

CV-51001 | 2018.05.07

Cyclone V Device Overview

30