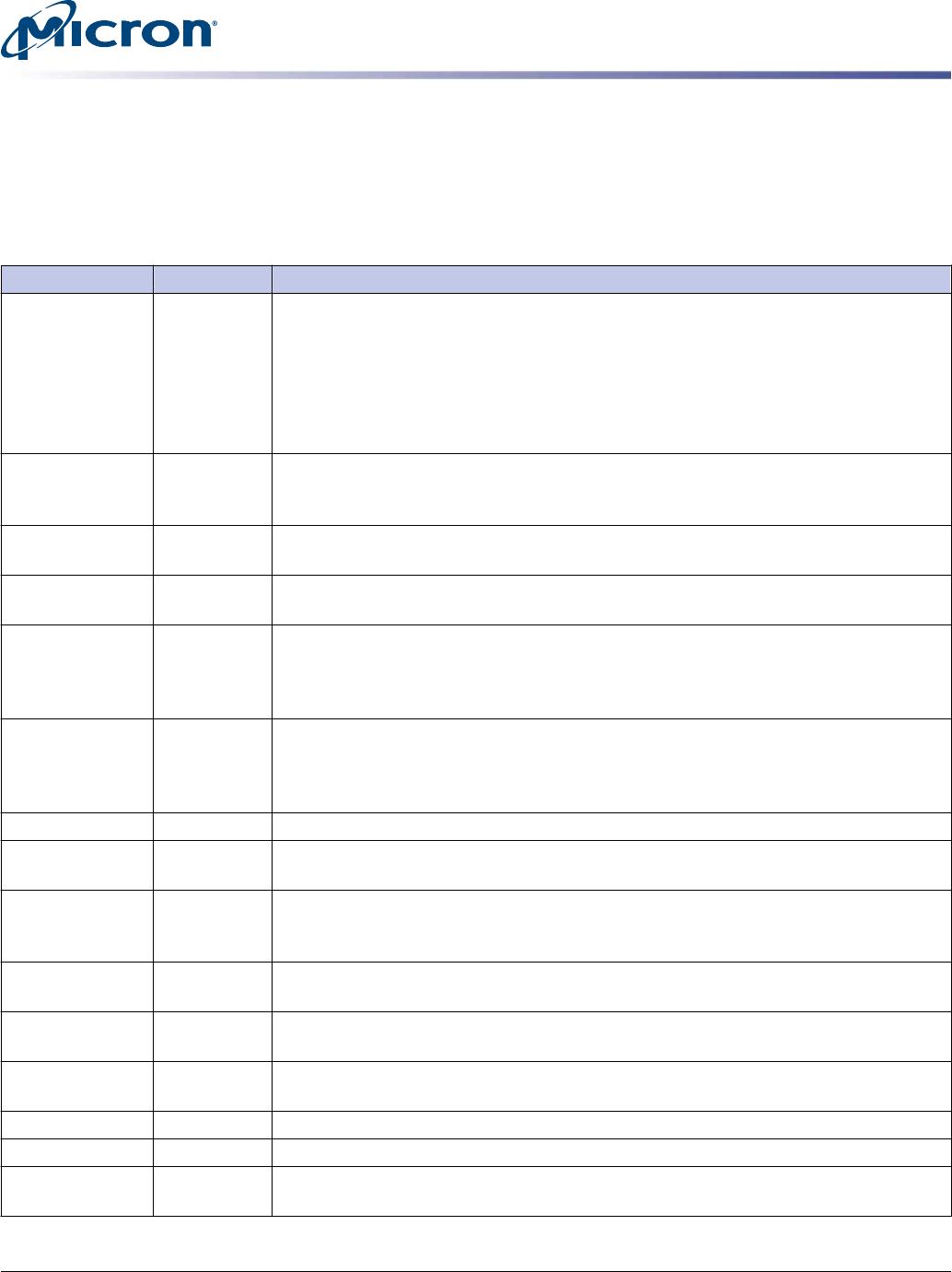

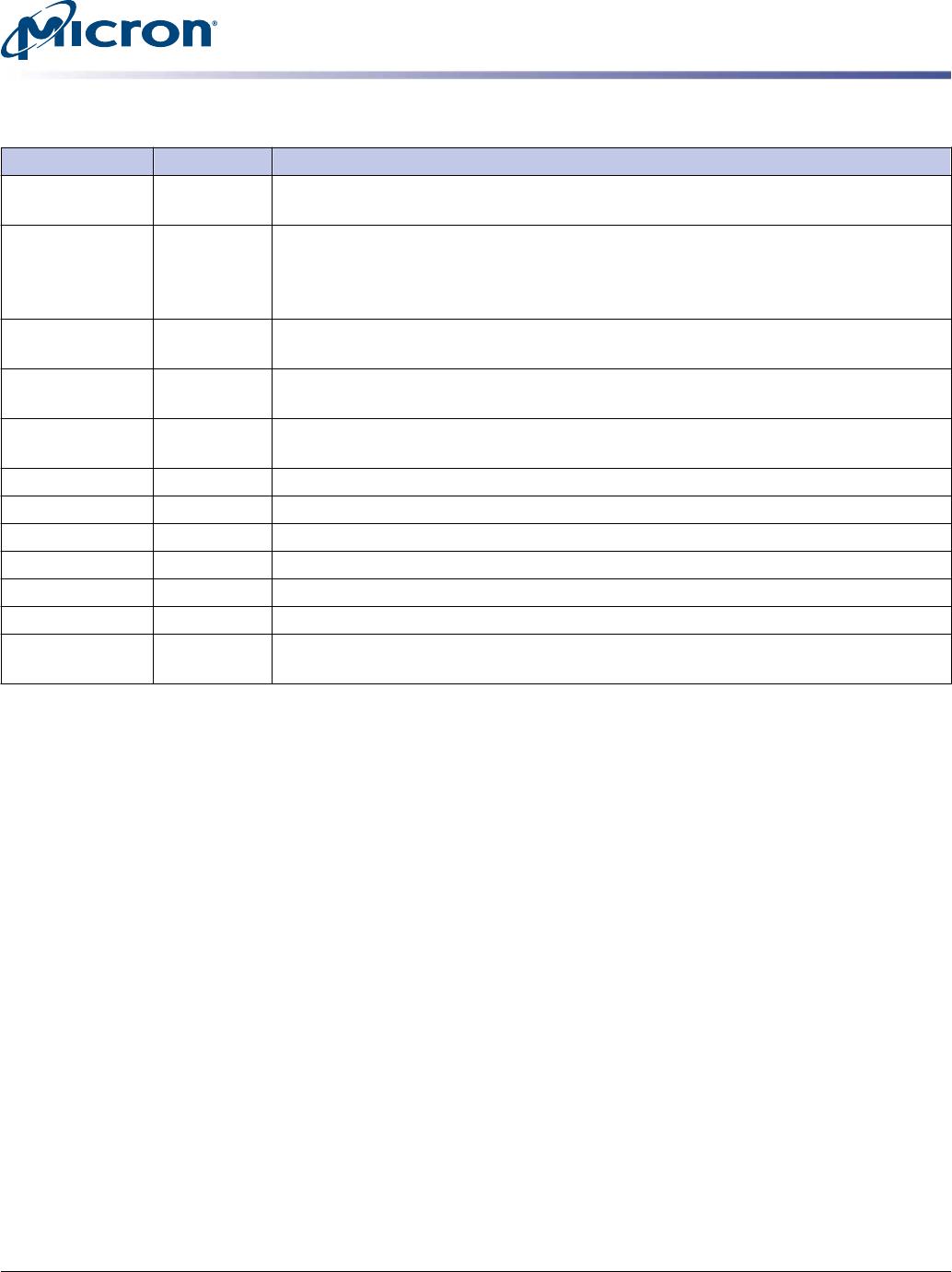

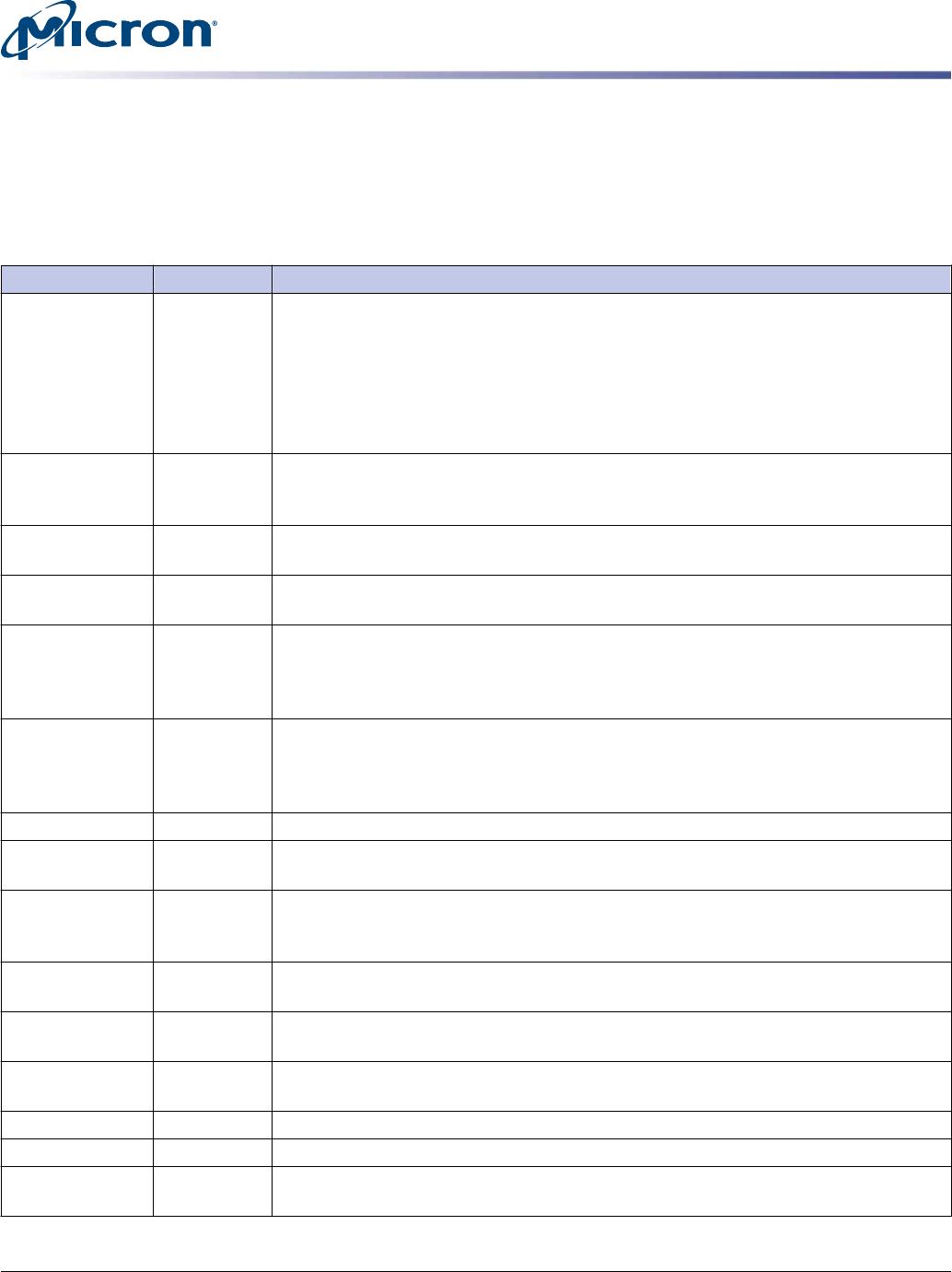

Pin Descriptions

The pin description table below is a comprehensive list of all possible pins for all DDR3

modules. All pins listed may not be supported on this module. See Pin Assignments for

information specific to this module.

Table 7: Pin Descriptions

Symbol Type Description

Ax Input Address inputs: Provide the row address for ACTIVE commands, and the column ad-

dress and auto precharge bit (A10) for READ/WRITE commands, to select one location

out of the memory array in the respective bank. A10 sampled during a PRECHARGE

command determines whether the PRECHARGE applies to one bank (A10 LOW, bank

selected by BAx) or all banks (A10 HIGH). The address inputs also provide the op-code

during a LOAD MODE command. See the Pin Assignments Table for density-specific

addressing information.

BAx Input Bank address inputs: Define the device bank to which an ACTIVE, READ, WRITE, or

PRECHARGE command is being applied. BA define which mode register (MR0, MR1,

MR2, or MR3) is loaded during the LOAD MODE command.

CKx,

CKx#

Input Clock: Differential clock inputs. All control, command, and address input signals are

sampled on the crossing of the positive edge of CK and the negative edge of CK#.

CKEx Input Clock enable: Enables (registered HIGH) and disables (registered LOW) internal circui-

try and clocks on the DRAM.

DMx Input Data mask (x8 devices only): DM is an input mask signal for write data. Input data

is masked when DM is sampled HIGH, along with that input data, during a write ac-

cess. Although DM pins are input-only, DM loading is designed to match that of the

DQ and DQS pins.

ODTx Input On-die termination: Enables (registered HIGH) and disables (registered LOW) termi-

nation resistance internal to the DDR3 SDRAM. When enabled in normal operation,

ODT is only applied to the following pins: DQ, DQS, DQS#, DM, and CB. The ODT input

will be ignored if disabled via the LOAD MODE command.

Par_In Input Parity input: Parity bit for Ax, RAS#, CAS#, and WE#.

RAS#, CAS#, WE# Input Command inputs: RAS#, CAS#, and WE# (along with S#) define the command being

entered.

RESET# Input

(LVCMOS)

Reset: RESET# is an active LOW asychronous input that is connected to each DRAM

and the registering clock driver. After RESET# goes HIGH, the DRAM must be reinitial-

ized as though a normal power-up was executed.

Sx# Input Chip select: Enables (registered LOW) and disables (registered HIGH) the command

decoder.

SAx Input Serial address inputs: Used to configure the temperature sensor/SPD EEPROM ad-

dress range on the I

2

C bus.

SCL Input Serial clock for temperature sensor/SPD EEPROM: Used to synchronize communi-

cation to and from the temperature sensor/SPD EEPROM on the I

2

C bus.

CBx I/O Check bits: Used for system error detection and correction.

DQx I/O Data input/output: Bidirectional data bus.

DQSx,

DQSx#

I/O Data strobe: Differential data strobes. Output with read data; edge-aligned with

read data; input with write data; center-aligned with write data.

2GB, 4GB, 8GB (x64, DR) 240-Pin DDR3 UDIMM

Pin Descriptions

PDF: 09005aef837cdd2d

jtf16c256_512_1gx64az.pdf - Rev. I 04/13 EN

4

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2008 Micron Technology, Inc. All rights reserved.