Si824x

22 Preliminary Rev. 0.3

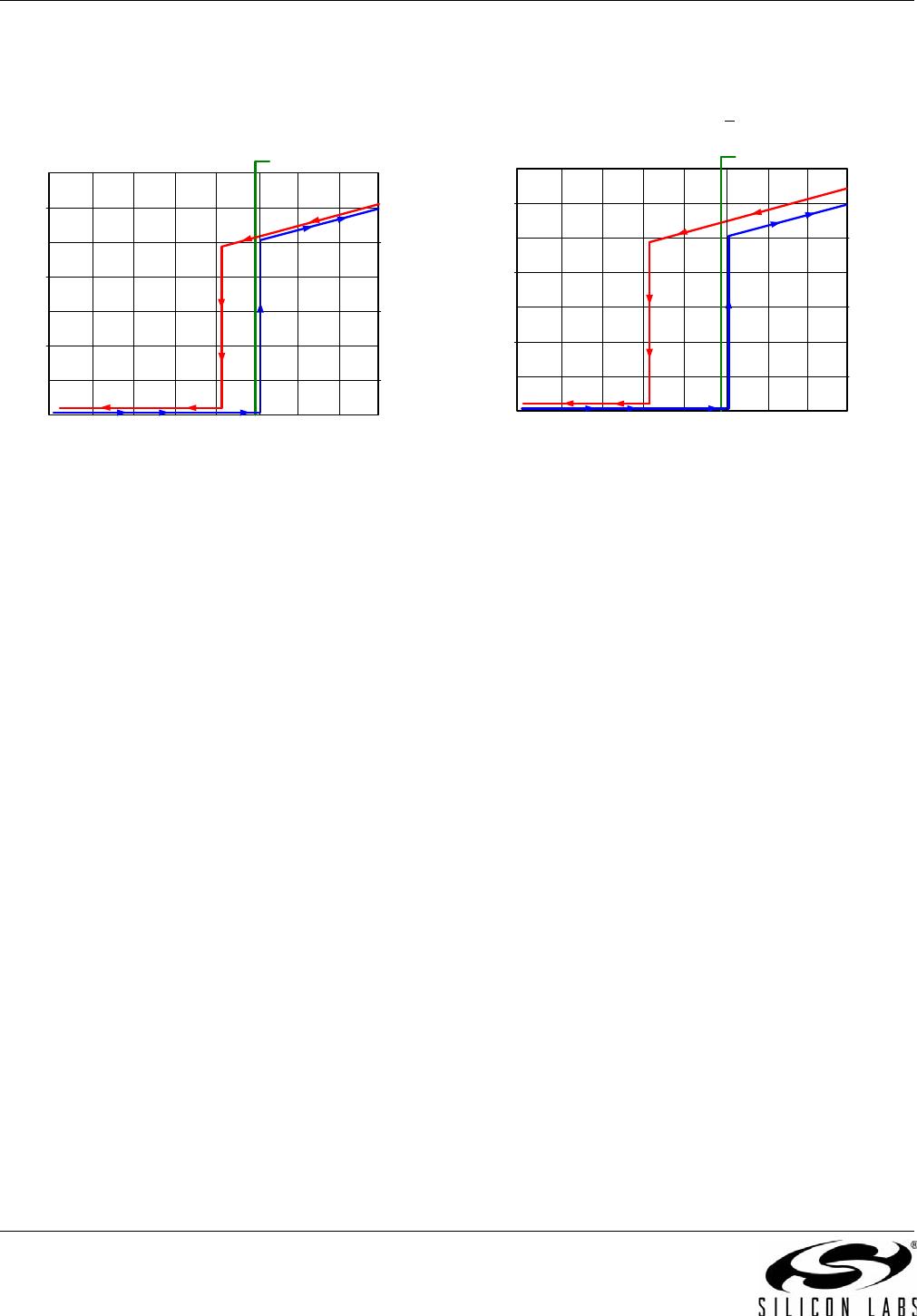

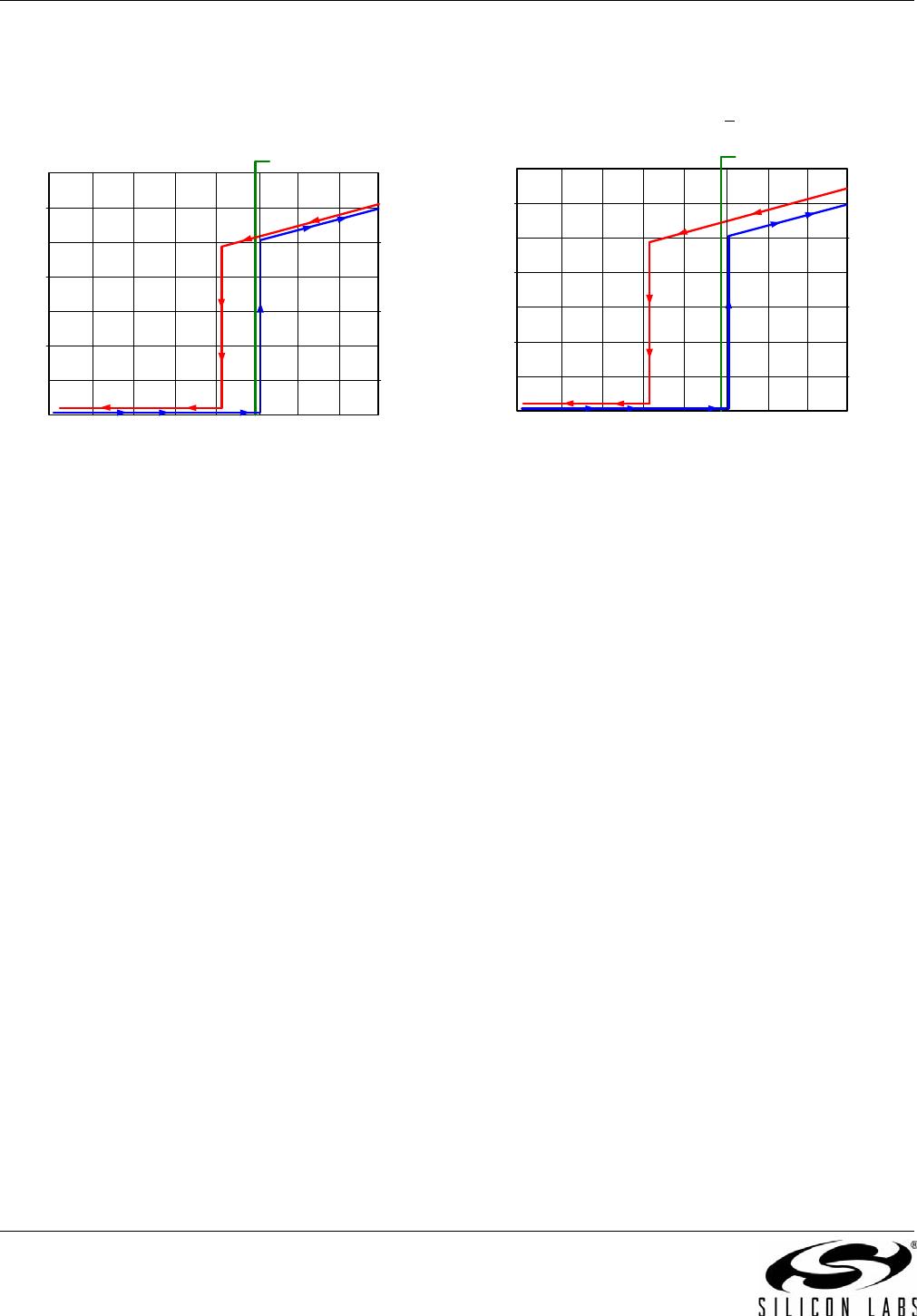

3.7.3. Undervoltage Lockout (UVLO)

The UVLO circuit unconditionally drives VO low when VDD is below the lockout threshold. Referring to Figures 35

and 36, upon power up, the Si824x is maintained in UVLO until VDD rises above VDD

UV+

. During power down, the

Si824x enters UVLO when VDD falls below the UVLO threshold plus hysteresis (i.e., VDD <

VDD

UV+

– VDD

HYS

).

Figure 35. Si824x UVLO Response (8 V)

Figure 36. Si824x UVLO Response (10 V)

3.7.4. Control Inputs

PWM inputs are high-true, TTL level-compatible logic inputs. VOA is high and VOB is low when the PWM input is

high, and VOA is low and VOB is high when the PWM input is low.

3.7.5. Disable Input

When brought high, the DISABLE input unconditionally drives VOA and VOB low regardless of the states of input.

Device operation terminates within tSD after DISABLE = V

IH

and resumes within tRESTART after DISABLE = V

IL

.

The DISABLE input has no effect if VDDI is below its UVLO level (i.e. VOA, VOB remain low). The DISABLE input

is typically connected to external protection circuitry to unconditionally halt driver operation in the event of a fault.

6.0

10.5

V

DDUV+

(Typ)

Output Voltage (V

O

)

6.5 7.0 7.5 8.0 8.5 9.0 9.5 10.0

Supply Voltage (V

DD

- V

SS

) (V)

8.5

10.5

V

DDUV+

(Typ)

Output Voltage (V

O

)

9.0 9.5 10.0 10.5 11.0 11.5 12.0 12.5

Supply Voltage (V

DD

- V

SS

) (V)