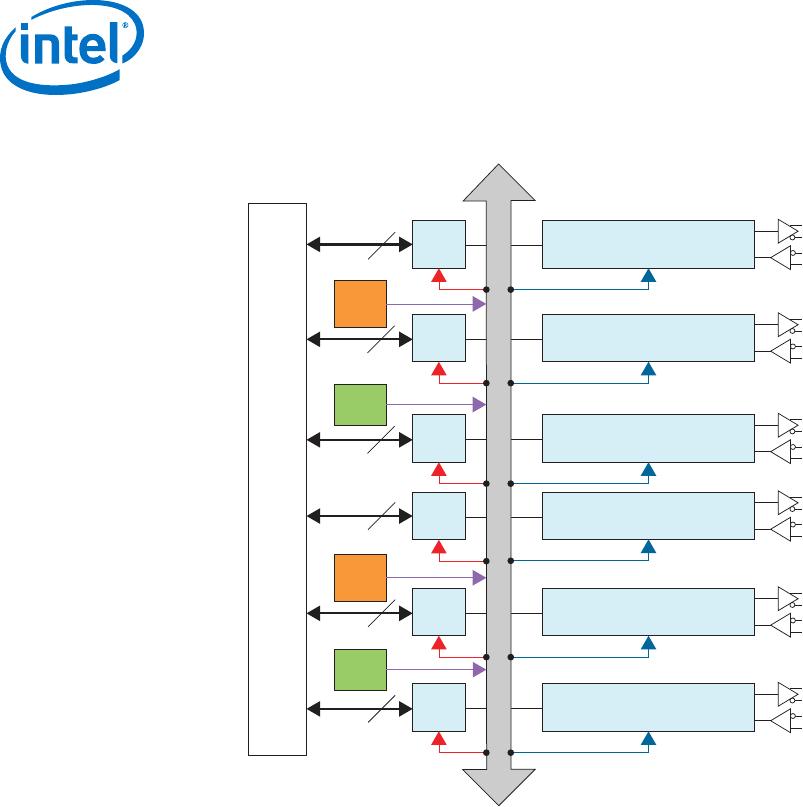

Each transceiver channel contains a channel PLL that can be used as the CMU PLL or

clock data recovery (CDR) PLL. In CDR mode, the channel PLL recovers the receiver

clock and data in the transceiver channel. Up to 80 independent data rates can be

configured on a single Intel Arria 10 device.

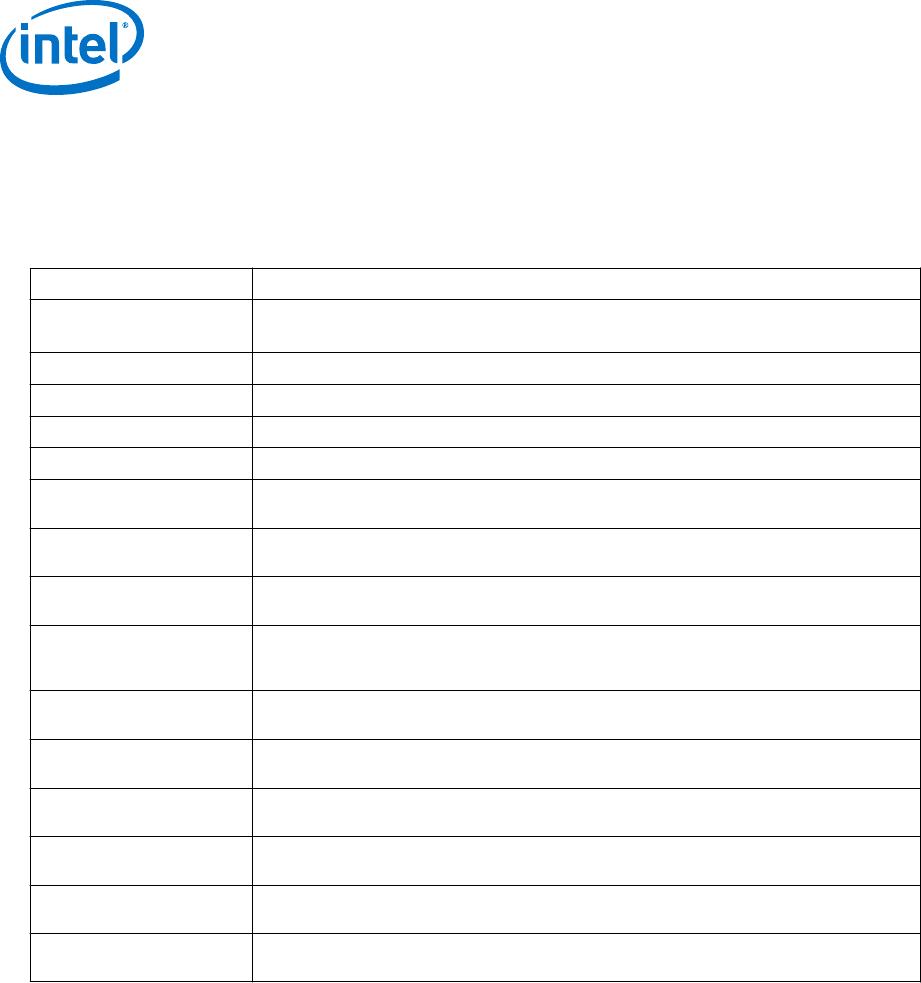

Table 23. PMA Features of the Transceivers in Intel Arria 10 Devices

Feature Capability

Chip-to-Chip Data Rates 1 Gbps to 17.4 Gbps (Intel Arria 10 GX devices)

1 Gbps to 25.8 Gbps (Intel Arria 10 GT devices)

Backplane Support Drive backplanes at data rates up to 12.5 Gbps

Optical Module Support SFP+/SFP, XFP, CXP, QSFP/QSFP28, CFP/CFP2/CFP4

Cable Driving Support SFP+ Direct Attach, PCI Express over cable, eSATA

Transmit Pre-Emphasis 4-tap transmit pre-emphasis and de-emphasis to compensate for system channel loss

Continuous Time Linear

Equalizer (CTLE)

Dual mode, high-gain, and high-data rate, linear receive equalization to compensate for

system channel loss

Decision Feedback Equalizer

(DFE)

7-fixed and 4-floating tap DFE to equalize backplane channel loss in the presence of

crosstalk and noisy environments

Variable Gain Amplifier Optimizes the signal amplitude prior to the CDR sampling and operates in fixed and

adaptive modes

Altera Digital Adaptive

Parametric Tuning (ADAPT)

Fully digital adaptation engine to automatically adjust all link equalization parameters—

including CTLE, DFE, and variable gain amplifier blocks—that provide optimal link margin

without intervention from user logic

Precision Signal Integrity

Calibration Engine (PreSICE)

Hardened calibration controller to quickly calibrate all transceiver control parameters on

power-up, which provides the optimal signal integrity and jitter performance

Advanced Transmit (ATX)

PLL

Low jitter ATX (LC tank based) PLLs with continuous tuning range to cover a wide range of

standard and proprietary protocols

Fractional PLLs On-chip fractional frequency synthesizers to replace on-board crystal oscillators and reduce

system cost

Digitally Assisted Analog

CDR

Superior jitter tolerance with fast lock time

Dynamic Partial

Reconfiguration

Allows independent control of the Avalon memory-mapped interface of each transceiver

channel for the highest transceiver flexibility

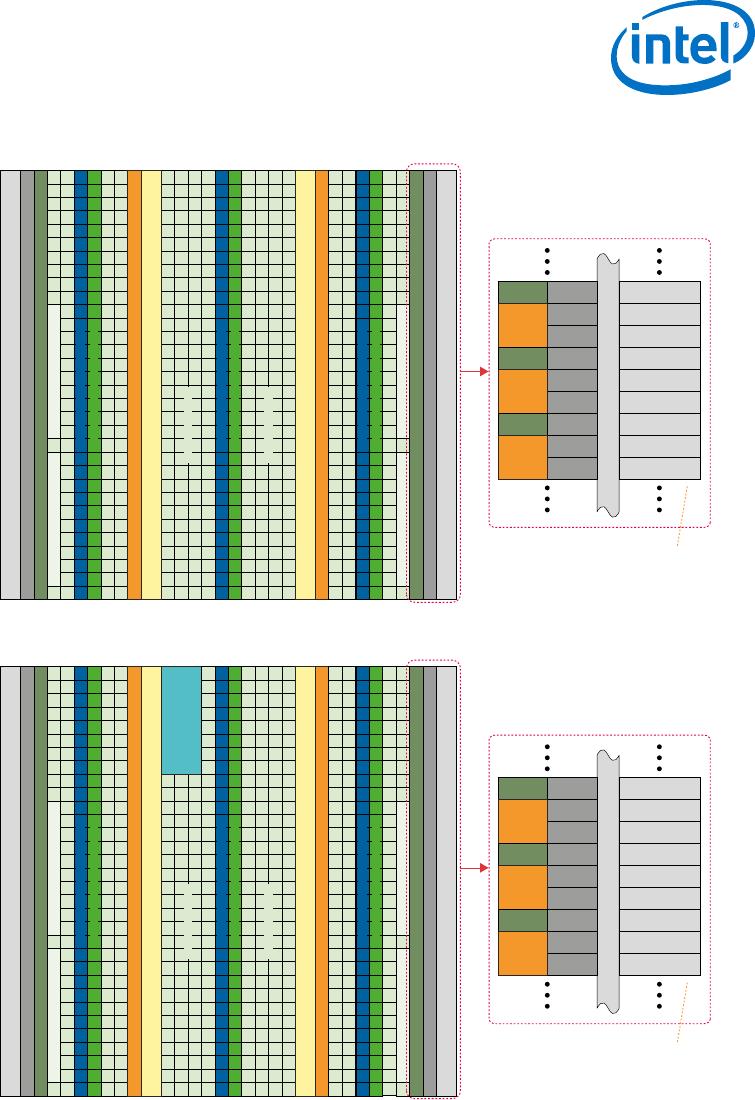

Multiple PCS-PMA and PCS-

PLD interface widths

8-, 10-, 16-, 20-, 32-, 40-, or 64-bit interface widths for flexibility of deserialization width,

encoding, and reduced latency

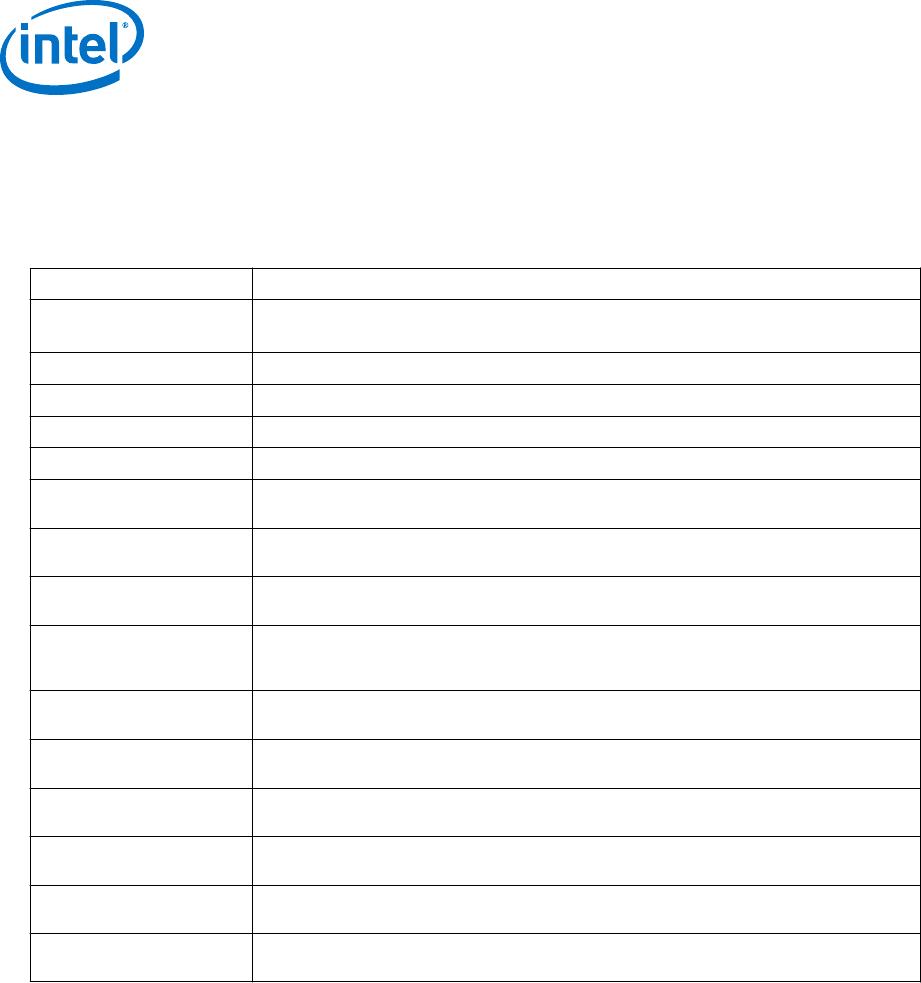

PCS Features

This table summarizes the Intel Arria 10 transceiver PCS features. You can use the

transceiver PCS to support a wide range of protocols ranging from 1 Gbps to

25.8 Gbps.

Intel

®

Arria

®

10 Device Overview

A10-OVERVIEW | 2018.04.09

Intel

®

Arria

®

10 Device Overview

30