Related Information

Intel Arria 10 Device Datasheet

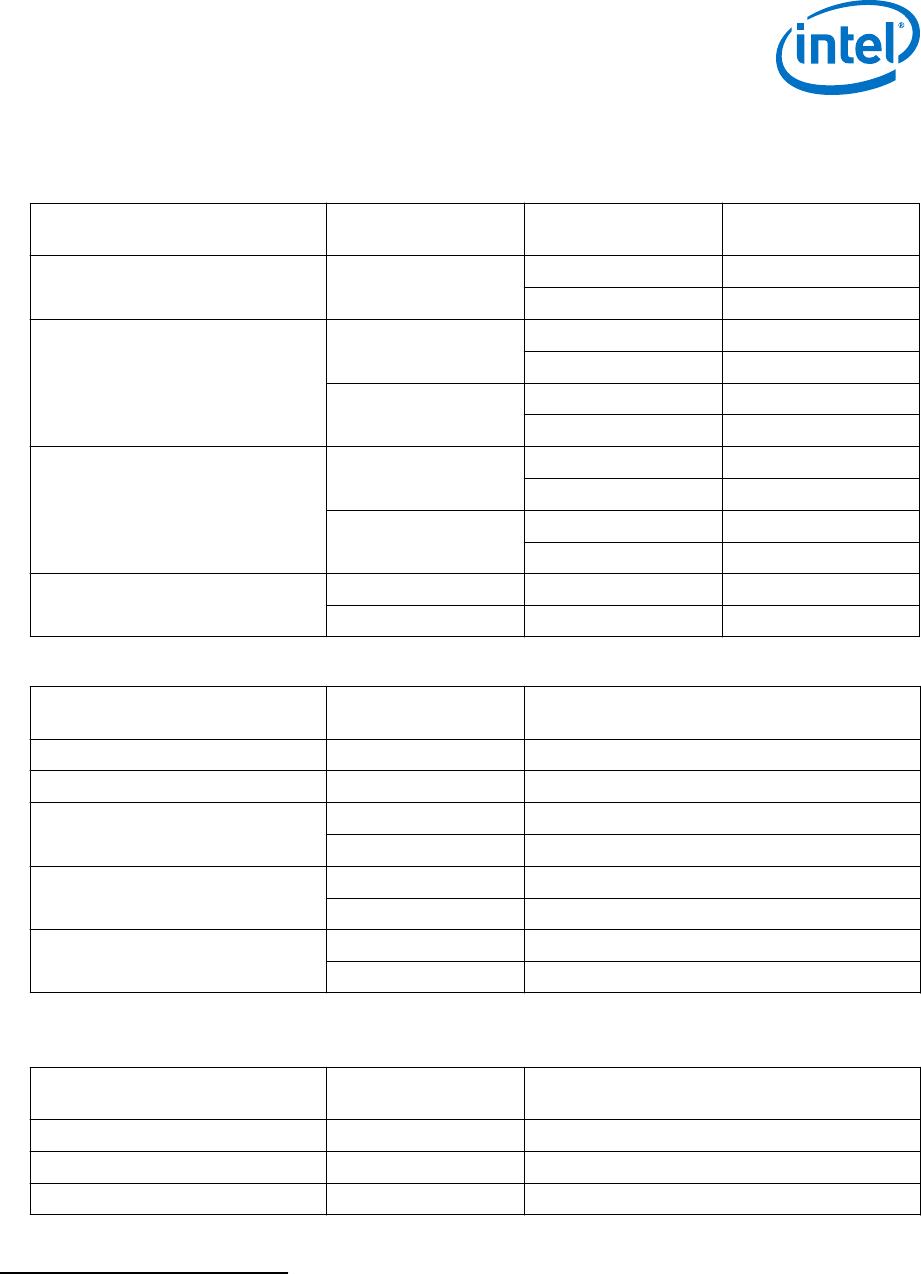

Lists the memory interface performance according to memory interface standards,

rank or chip select configurations, and Intel Arria 10 device speed grades.

PCIe Gen1, Gen2, and Gen3 Hard IP

Intel Arria 10 devices contain PCIe hard IP that is designed for performance and

ease-of-use:

• Includes all layers of the PCIe stack—transaction, data link and physical layers.

• Supports PCIe Gen3, Gen2, and Gen1 Endpoint and Root Port in x1, x2, x4, or x8

lane configuration.

• Operates independently from the core logic—optional configuration via protocol

(CvP) allows the PCIe link to power up and complete link training in less than

100 ms while the Intel Arria 10 device completes loading the programming file for

the rest of the FPGA.

• Provides added functionality that makes it easier to support emerging features

such as Single Root I/O Virtualization (SR-IOV) and optional protocol extensions.

• Provides improved end-to-end datapath protection using ECC.

• Supports FPGA configuration via protocol (CvP) using PCIe at Gen3, Gen2, or

Gen1 speed.

Related Information

PCS Features on page 30

Enhanced PCS Hard IP for Interlaken and 10 Gbps Ethernet

Interlaken Support

The Intel Arria 10 enhanced PCS hard IP provides integrated Interlaken PCS

supporting rates up to 25.8 Gbps per lane.

The Interlaken PCS is based on the proven functionality of the PCS developed for

Intel’s previous generation FPGAs, which demonstrated interoperability with Interlaken

ASSP vendors and third-party IP suppliers. The Interlaken PCS is present in every

transceiver channel in Intel Arria 10 devices.

Related Information

PCS Features on page 30

10 Gbps Ethernet Support

The Intel Arria 10 enhanced PCS hard IP supports 10GBASE-R PCS compliant with

IEEE 802.3 10 Gbps Ethernet (10GbE). The integrated hard IP support for 10GbE and

the 10 Gbps transceivers save external PHY cost, board space, and system power.

Intel

®

Arria

®

10 Device Overview

A10-OVERVIEW | 2018.04.09

Intel

®

Arria

®

10 Device Overview

26