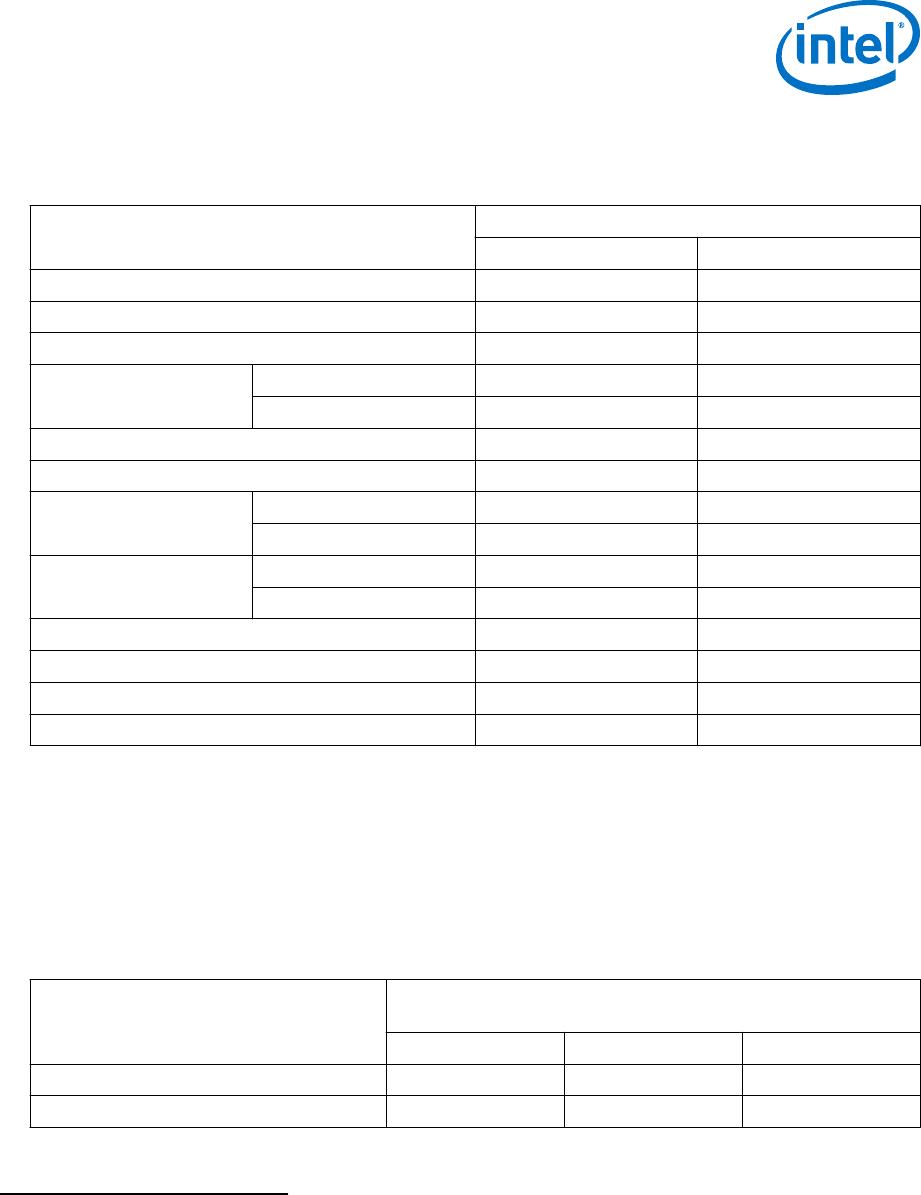

Maximum Resources

Table 12. Maximum Resource Counts for Intel Arria 10 SX Devices

Resource Product Line

SX 160 SX 220 SX 270 SX 320 SX 480 SX 570 SX 660

Logic Elements (LE) (K) 160 220 270 320 480 570 660

ALM 61,510 80,330 101,620 119,900 183,590 217,080 251,680

Register 246,040 321,320 406,480 479,600 734,360 868,320 1,006,720

Memory (Kb) M20K 8,800 11,740 15,000 17,820 28,620 36,000 42,620

MLAB 1,050 1,690 2,452 2,727 4,164 5,096 5,788

Variable-precision DSP Block 156 192 830 985 1,368 1,523 1,687

18 x 19 Multiplier 312 384 1,660 1,970 2,736 3,046 3,374

PLL Fractional

Synthesis

6 6 8 8 12 16 16

I/O 6 6 8 8 12 16 16

17.4 Gbps Transceiver 12 12 24 24 36 48 48

GPIO

(8)

288 288 384 384 492 696 696

LVDS Pair

(9)

120 120 168 168 174 324 324

PCIe Hard IP Block 1 1 2 2 2 2 2

Hard Memory Controller 6 6 8 8 12 16 16

ARM Cortex-A9 MPCore

Processor

Yes Yes Yes Yes Yes Yes Yes

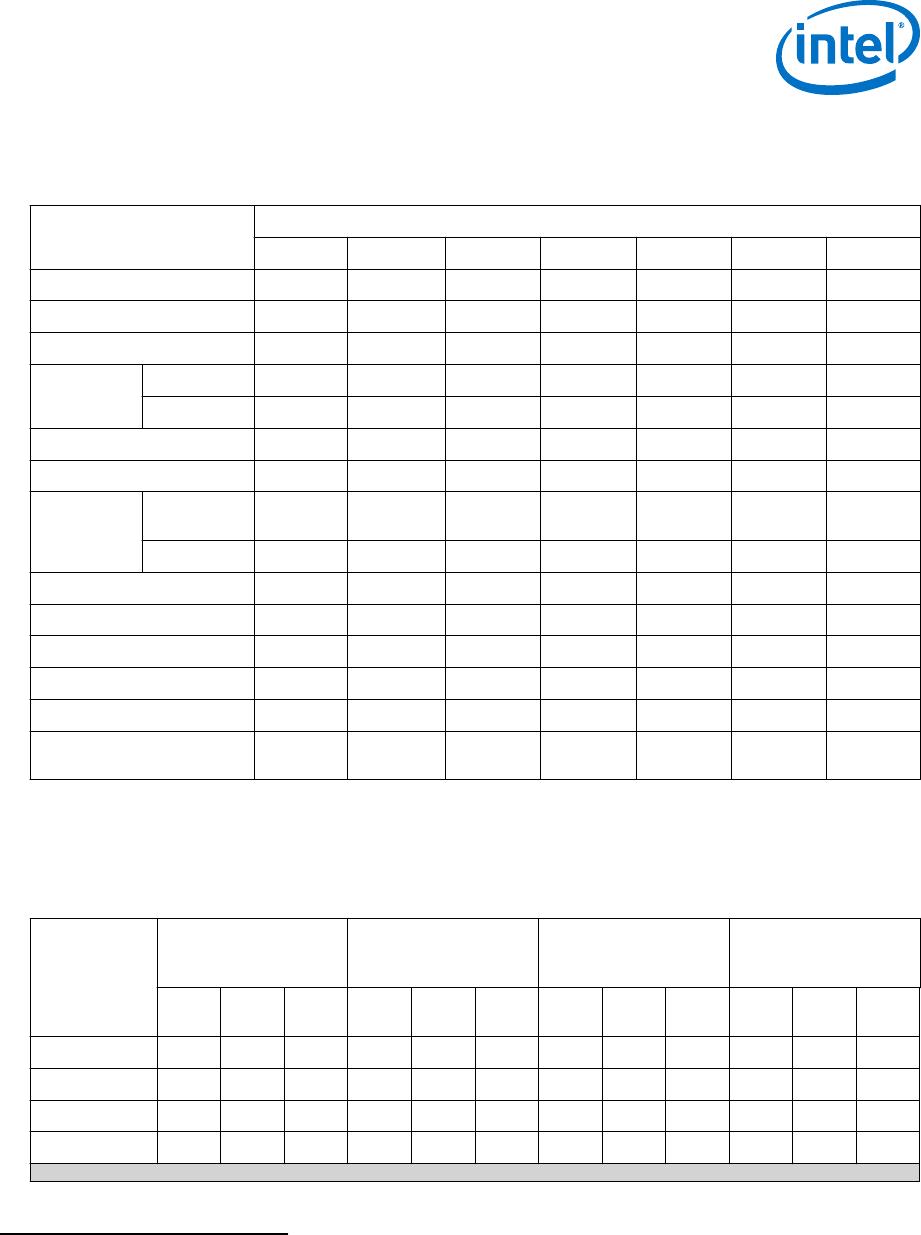

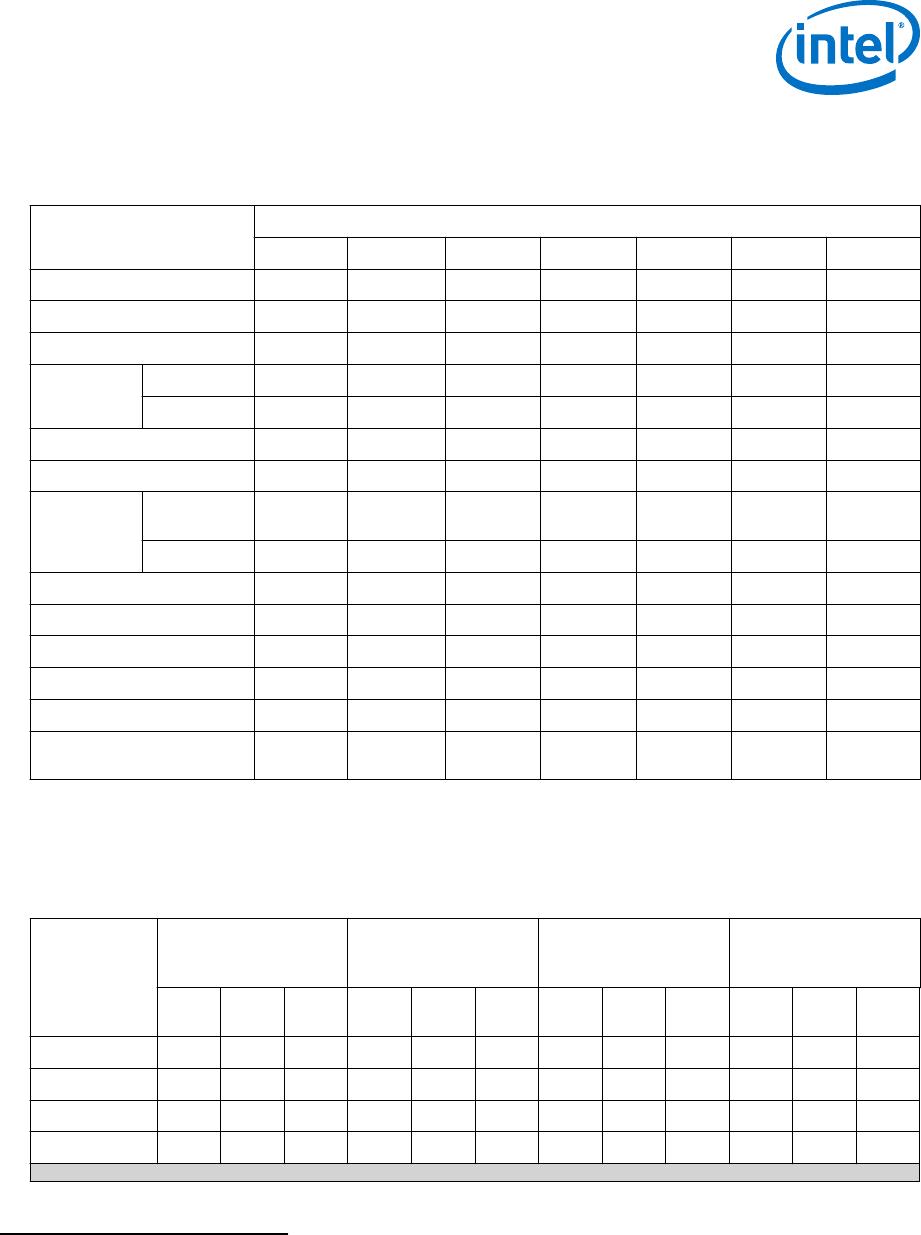

Package Plan

Table 13. Package Plan for Intel Arria 10 SX Devices (U19, F27, F29, and F34)

Refer to I/O and High Speed I/O in Intel Arria 10 Devices chapter for the number of 3 V I/O, LVDS I/O, and

LVDS channels in each device package.

Product Line

U19

(19 mm × 19 mm,

484-pin UBGA)

F27

(27 mm × 27 mm,

672-pin FBGA)

F29

(29 mm × 29 mm,

780-pin FBGA)

F34

(35 mm × 35 mm,

1152-pin FBGA)

3 V

I/O

LVDS

I/O

XCVR 3 V

I/O

LVDS

I/O

XCVR 3 V

I/O

LVDS

I/O

XCVR 3 V

I/O

LVDS

I/O

XCVR

SX 160 48 144 6 48 192 12 48 240 12 — — —

SX 220 48 144 6 48 192 12 48 240 12 — — —

SX 270 — — — 48 192 12 48 312 12 48 336 24

SX 320 — — — 48 192 12 48 312 12 48 336 24

continued...

(8)

The number of GPIOs does not include transceiver I/Os. In the Intel Quartus Prime software,

the number of user I/Os includes transceiver I/Os.

(9)

Each LVDS I/O pair can be used as differential input or output.

Intel

®

Arria

®

10 Device Overview

A10-OVERVIEW | 2018.04.09

Intel

®

Arria

®

10 Device Overview

15