© Semiconductor Components Industries, LLC, 2016

August, 2016 − Rev. 12

1 Publication Order Number:

MC10LVEP16/D

MC10LVEP16, MC100LVEP16

2.5V / 3.3V ECL

Differential Receiver/Driver

Description

The MC10/100LVEP16 is a world class differential receiver/driver.

The device is functionally equivalent to the EL16, EP16 and LVEL16

devices. With output transition times significantly faster than the EL16

and LVEL16, the LVEP16 is ideally suited for interfacing with high

frequency and low voltage (2.5 V) sources. Single-Ended CLK input

operation is limited to a V

CC

≥ 3.0 V in PECL mode, or V

EE

≤ −3.0 V in

NECL mode.

The V

BB

pin, an internally generated Voltage supply, is available to

this device only. For Single-Ended input conditions, the unused

differential input is connected to V

BB

as a switching reference voltage.

V

BB

may also rebias AC coupled inputs. When used, decouple V

BB

and V

CC

via a 0.01 mF capacitor and limit current sourcing or sinking

to 0.5 mA. When not used, V

BB

should be left open.

The 100 Series contains temperature compensation.

Features

• 240 ps Propagation Delay

• Maximum Frequency = > 4 GHz Typical

• PECL Mode Operating Range:

V

CC

= 2.375 V to 3.8 V with V

EE

= 0 V

• NECL Mode Operating Range:

V

CC

= 0 V with V

EE

= −2.375 V to −3.8 V

• V

BB

Output

• Open Input Default State

• LVDS Input Compatible

• These Devices are Pb-Free, Halogen Free and are RoHS Compliant

*For additional marking information, refer to

Application Note AND8002/D

.

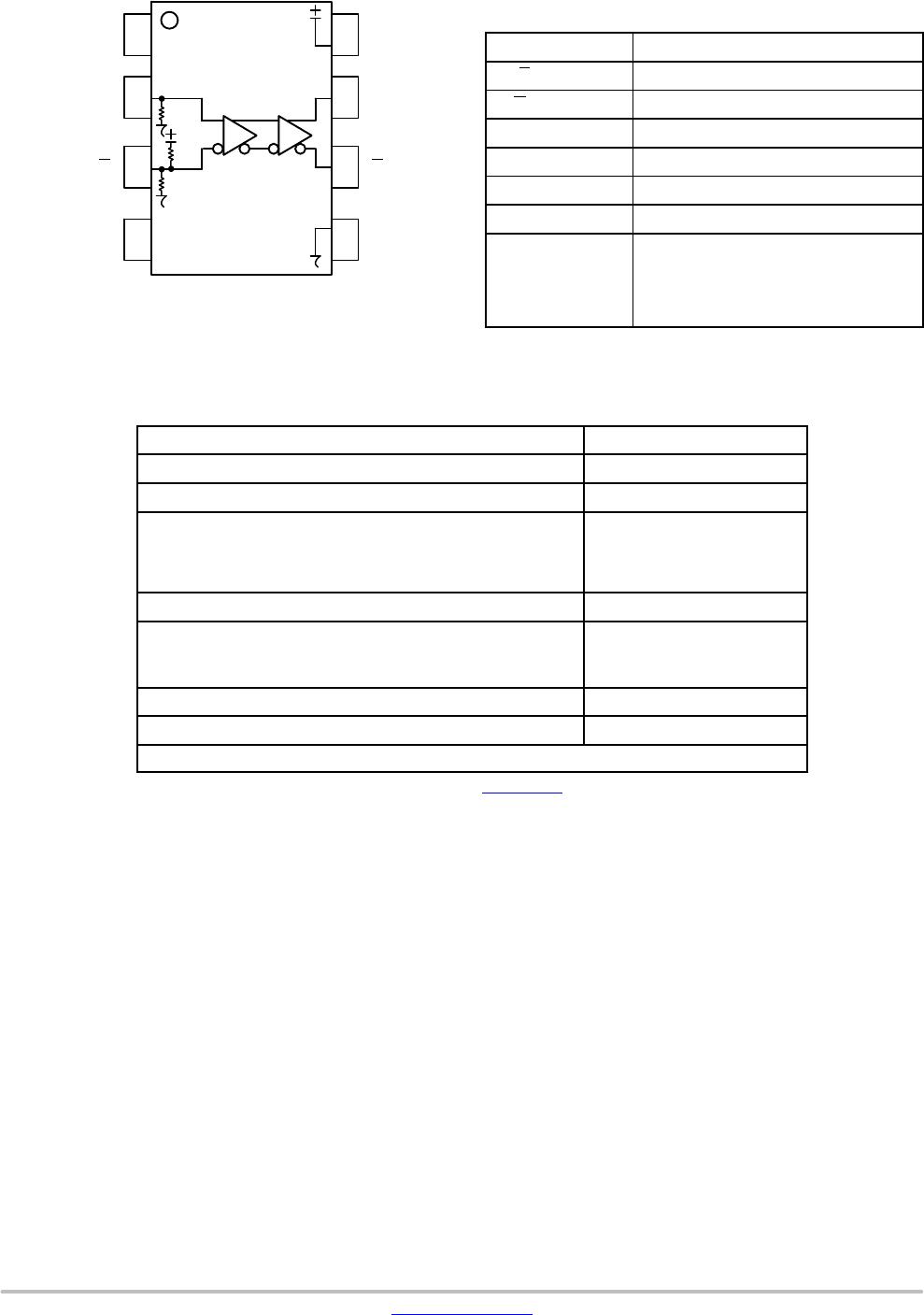

H = MC10 A = Assembly Location

K = MC100 L = Wafer Lot

5Y = MC10 Y = Year

4L = MC100 W = Work Week

M = Date Code G = Pb-Free Package

(Note: Microdot may be in either location)

MARKING DIAGRAMS*

HU16

ALYWG

G

KU16

ALYWG

G

SOIC−8 NB

D SUFFIX

CASE 751−07

TSSOP−8

DT SUFFIX

CASE 948R−02

1

8

1

8

1

8

www.onsemi.com

See detailed ordering and shipping information in the package

dimensions section on page 9 of this data sheet.

ORDERING INFORMATION

1

8

HVP16

ALYW

G

1

8

KVP16

ALYW

G

1

8

DFN8

MN SUFFIX

CASE 506AA

5Y MG

G

14

4L MG

G

14

SOIC−8 NB TSSOP−8 DFN8