24

Integrated Silicon Solution, Inc. — www.issi.com

Rev. F

03/03/09

IS42S32400D

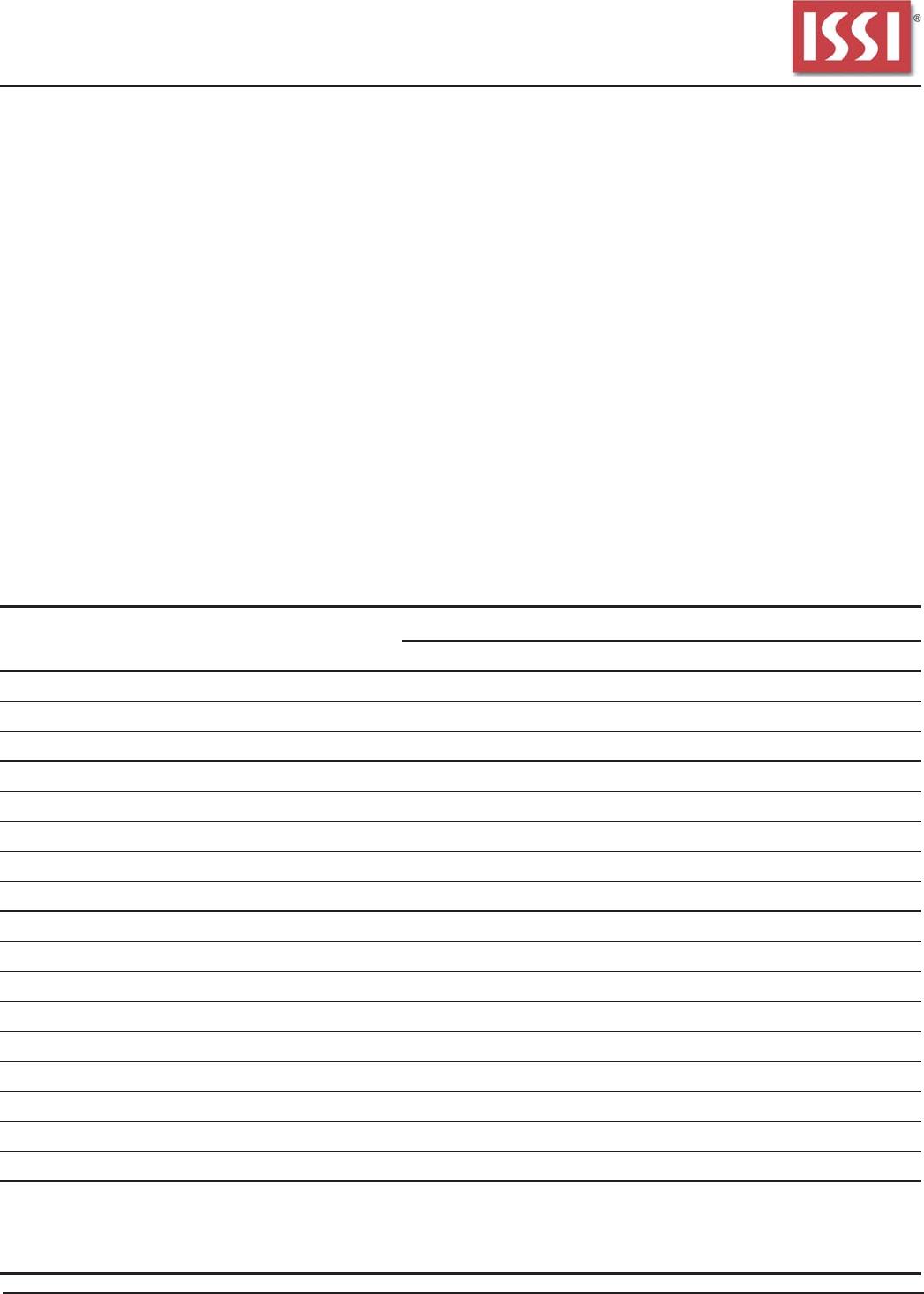

BURST DEFINITION

Burst Starting Column Order of Accesses Within a Burst

Length Address Type = Sequential Type = Interleaved

A0

2 0 0-1 0-1

1 1-0 1-0

A1 A0

0 0 0-1-2-3 0-1-2-3

4 0 1 1-2-3-0 1-0-3-2

1 0 2-3-0-1 2-3-0-1

1 1 3-0-1-2 3-2-1-0

A2 A1 A0

0 0 0 0-1-2-3-4-5-6-7 0-1-2-3-4-5-6-7

0 0 1 1-2-3-4-5-6-7-0 1-0-3-2-5-4-7-6

0 1 0 2-3-4-5-6-7-0-1 2-3-0-1-6-7-4-5

8 0 1 1 3-4-5-6-7-0-1-2 3-2-1-0-7-6-5-4

1 0 0 4-5-6-7-0-1-2-3 4-5-6-7-0-1-2-3

1 0 1 5-6-7-0-1-2-3-4 5-4-7-6-1-0-3-2

1 1 0 6-7-0-1-2-3-4-5 6-7-4-5-2-3-0-1

1 1 1 7-0-1-2-3-4-5-6 7-6-5-4-3-2-1-0

Full n = A0-A7 Cn, Cn + 1, Cn + 2 Not Supported

Page Cn + 3, Cn + 4...

(y) (location 0-y) …Cn - 1,

Cn…

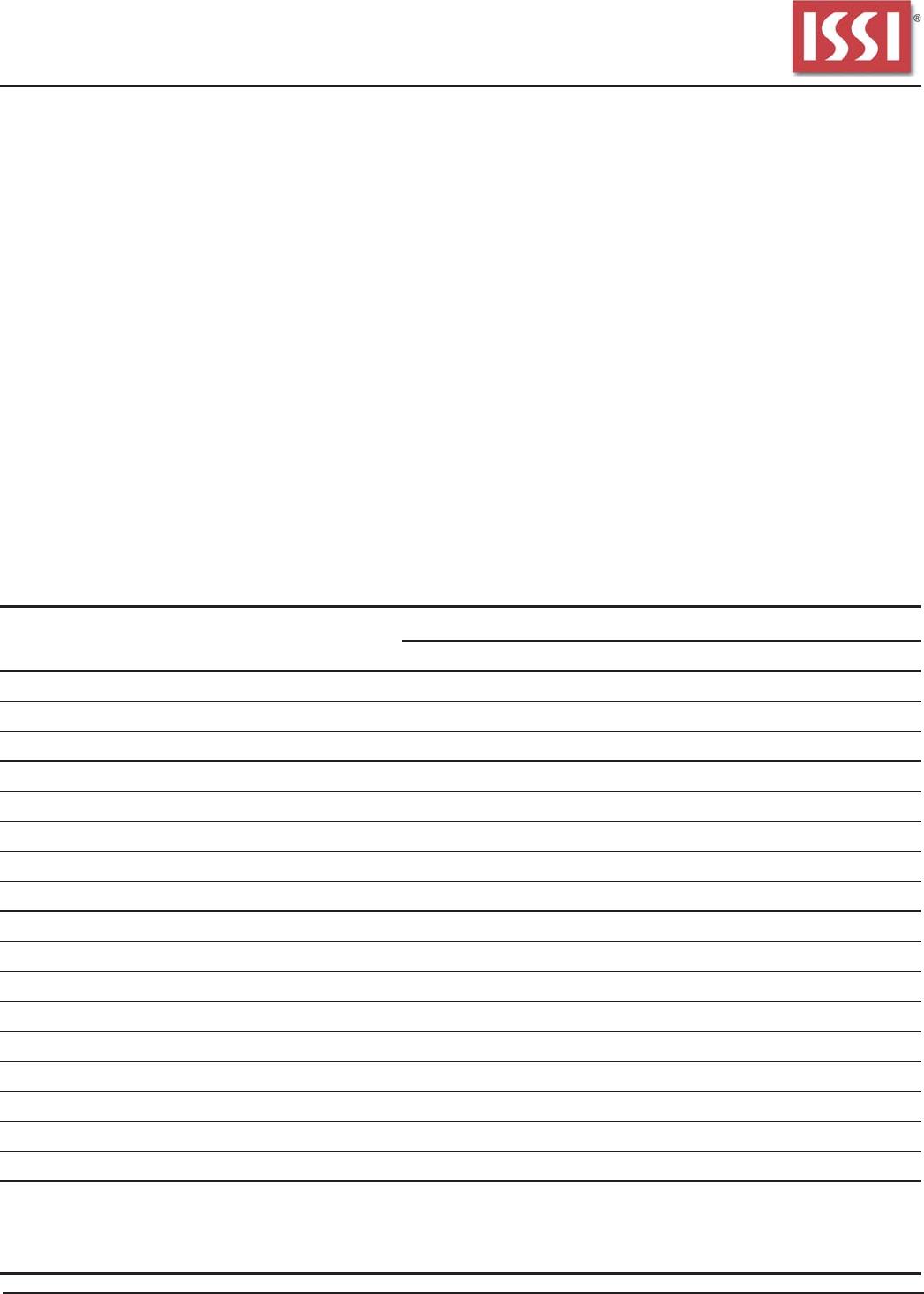

BURST LENGTH

Read and write accesses to the SDRAM are burst oriented,

with the burst length being programmable, as shown in

MODE REGISTER DEFINITION. The burst length deter-

mines the maximum number of column locations that can

be accessed for a given READ or WRITE command. Burst

lengths of 1, 2, 4 or 8 locations are available for both the

sequential and the interleaved burst types, and a full-page

burst is available for the sequential type. The full-page burst

is used in conjunction with the BURST TERMINATE com-

mand to generate arbitrary burst lengths.

Reserved states should not be used, as unknown operation

or incompatibility with future versions may result.

When a READ or WRITE command is issued, a block of

columns equal to the burst length is effectively selected. All

accesses for that burst take place within this block, mean-

ing that the burst will wrap within the block if a boundary is

reached. The block is uniquely selected by A1-A7 (x32)

when the burst length is set to two; by A2-A7 (x32) when the

burst length is set to four; and by A3-A7 (x32) when the burst

length is set to eight. The remaining (least significant)

address bit(s) is (are) used to select the starting location

within the block. Full-page bursts wrap within the page if the

boundary is reached.

Burst Type

Accesses within a given burst may be programmed to be

either sequential or interleaved; this is referred to as the

burst type and is selected via bit M3.

The ordering of accesses within a burst is determined by the

burst length, the burst type and the starting column address,

as shown in BURST DEFINITION table.