Data Sheet ADuM3223/ADuM4223

Rev. I | Page 17 of 20

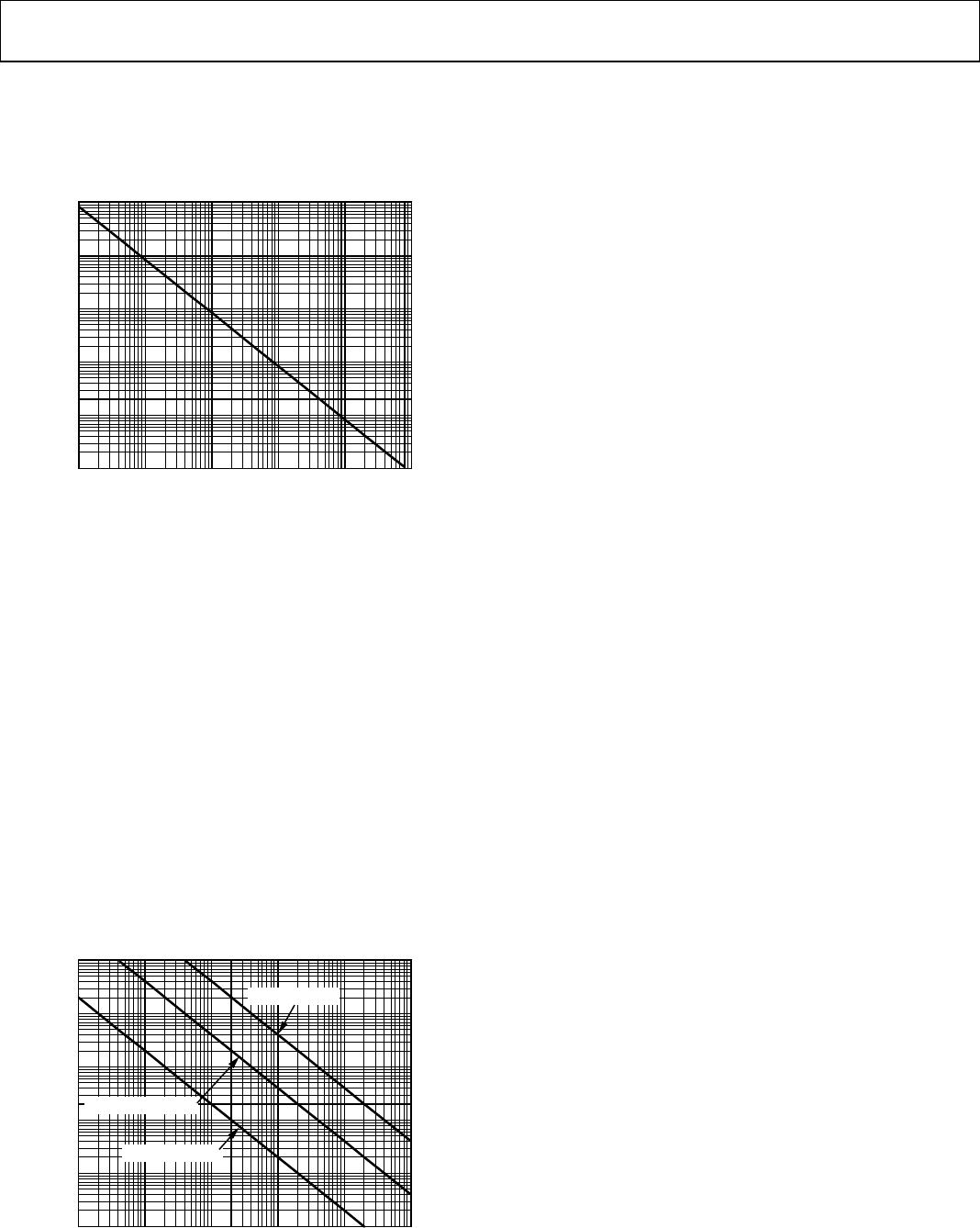

Given the geometry of the receiving coil in the ADuM3223/

ADuM4223 and an imposed requirement that the induced

voltage is, at most, 50% of the 0.5 V margin at the decoder, a

maximum allowable magnetic field is calculated, as shown in

Figure 23.

Figure 23. Maximum Allowable External Magnetic Flux Density

For example, at a magnetic field frequency of 1 MHz, the

maximum allowable magnetic field of 0.08 kgauss induces a

voltage of 0.25 V at the receiving coil. This is about 50% of the

sensing threshold and does not cause a faulty output transition.

Similarly, if such an event were to occur during a transmitted

pulse (and had the worst-case polarity), the received pulse is

reduced from >1.0 V to 0.75 V, still well above the 0.5 V sensing

threshold of the decoder.

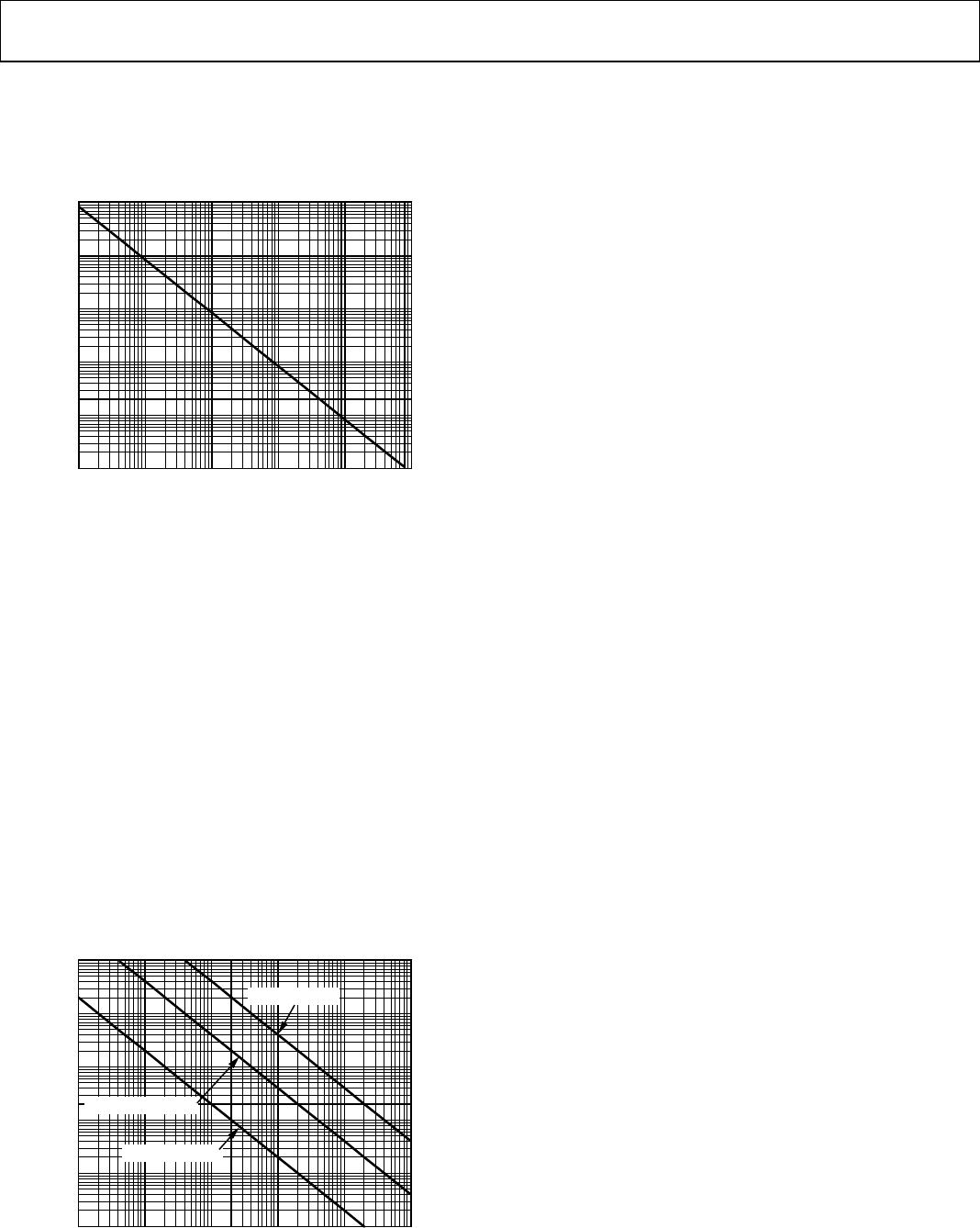

The preceding magnetic flux density values correspond to

specific current magnitudes at given distances away from the

ADuM3223/ADuM4223 transformers. Figure 24 expresses

these allowable current magnitudes as a function of frequency

for selected distances. As shown, the ADuM3223/ADuM4223

are immune and only can be affected by extremely large currents

operated at a high frequency and very close to the component.

For the 1 MHz example, a 0.2 kA current must be placed 5 mm

away from the ADuM3223/ADuM4223 to affect the

component’s operation.

Figure 24. Maximum Allowable Current for Various

Current-to-ADuM3223/ADuM4223 Spacings

POWER CONSUMPTION

The supply current at a given channel of the ADuM3223/

ADuM4223 isolator is a function of the supply voltage,

channel data rate, and channel output load.

During the driving of a MOSFET gate, the driver must dissipate

power. This power is not insignificant and can lead to thermal

shutdown (TSD) if considerations are not made. The gate of a

MOSFET can be simulated approximately as a capacitive load.

Due to Miller capacitance and other nonlinearities, it is common

practice to take the stated input capacitance, C

ISS

, of a given

MOSFET and multiply it by a factor of 5 to arrive at a conservative

estimate to approximate the load being driven. With this value,

the estimated total power dissipation per channel due to

switching action is given by

P

DISS

= C

EST

× (V

DDx

)

2

× f

S

where:

C

EST

= C

ISS

× 5.

f

S

is the switching frequency.

Alternately, use the gate charge to obtain a more precise value

for P

DISS

.

P

DISS

= Q

GATE

× V

DDx

× f

S

where:

Q

GATE

is the gate charge for the MOSFET.

f

S

is the switching frequency.

This power dissipation is shared between the internal on

resistances of the internal gate driver switches and the external

gate resistances, R

GON

and R

GOFF

. The ratio of the internal gate

resistances to the total series resistance allows the calculation of

losses seen within the ADuM3223/ADuM4223 chips per

channel.

P

DISS_IC

= P

DISS

× ½ × (R

DSON_P

/(R

EXT_X

+ R

DSON_P

) +

R

DSON_N

/(R

EXT_X

+ R

DSON_N

))

Taking the power dissipation found inside the chip and

multiplying it by θ

JA

gives the rise above ambient temperature

that the ADuM3223/ADuM4223 experiences, multiplied by two

to reflect that there are two channels.

T

J

= θ

JA

× 2 × P

DISS_IC

+ T

AMB

For the device to remain within specification, T

J

must not

exceed 125°C. If T

J

exceeds 150°C (typical), the device enters TSD.

Quiescent power dissipation may also be added to give a more

accurate number for temperature rise, but the switching power

losses are often the largest source of power dissipation, and

quiescent losses can often be ignored. To calculate the total

supply current, the quiescent supply currents for each input and

output channel corresponding to I

DD1(Q)

, I

DDA(Q)

, and I

DDB(Q)

are

added. The full equation for the T

J

becomes

T

J

= θ

JA

× (2 × P

DISS_IC

+ V

DD1

× I

DD1(Q)

+ V

DDA

× I

DDA(Q)

+

V

DDB

× I

DDB(Q)

) + T

AMB

100

10

1

0.1

0.01

0.001

1k 10k 100k 1M 10M 100M

MAXIMUM ALLOWABLE MAGNETIC FLUX

DENSITY (kgauss)

MAGNETIC FIELD FREQUENCY (Hz)

10450-122

1k

100

10

1

0.1

0.01

1k 10k 100k 1M 10M 100M

MAXIMUM ALLOWABLE CURRENT (kA)

MAGNETIC FIELD FREQUENCY (Hz)

10450-123

DISTANCE = 1m

DISTANCE = 100mm

DISTANCE = 5mm