AT88SC0104C [SUMMARY DATASHEET]

Atmel-2021MS-CryptoMem-AT88SC0104C-Datasheet-Summary_122013

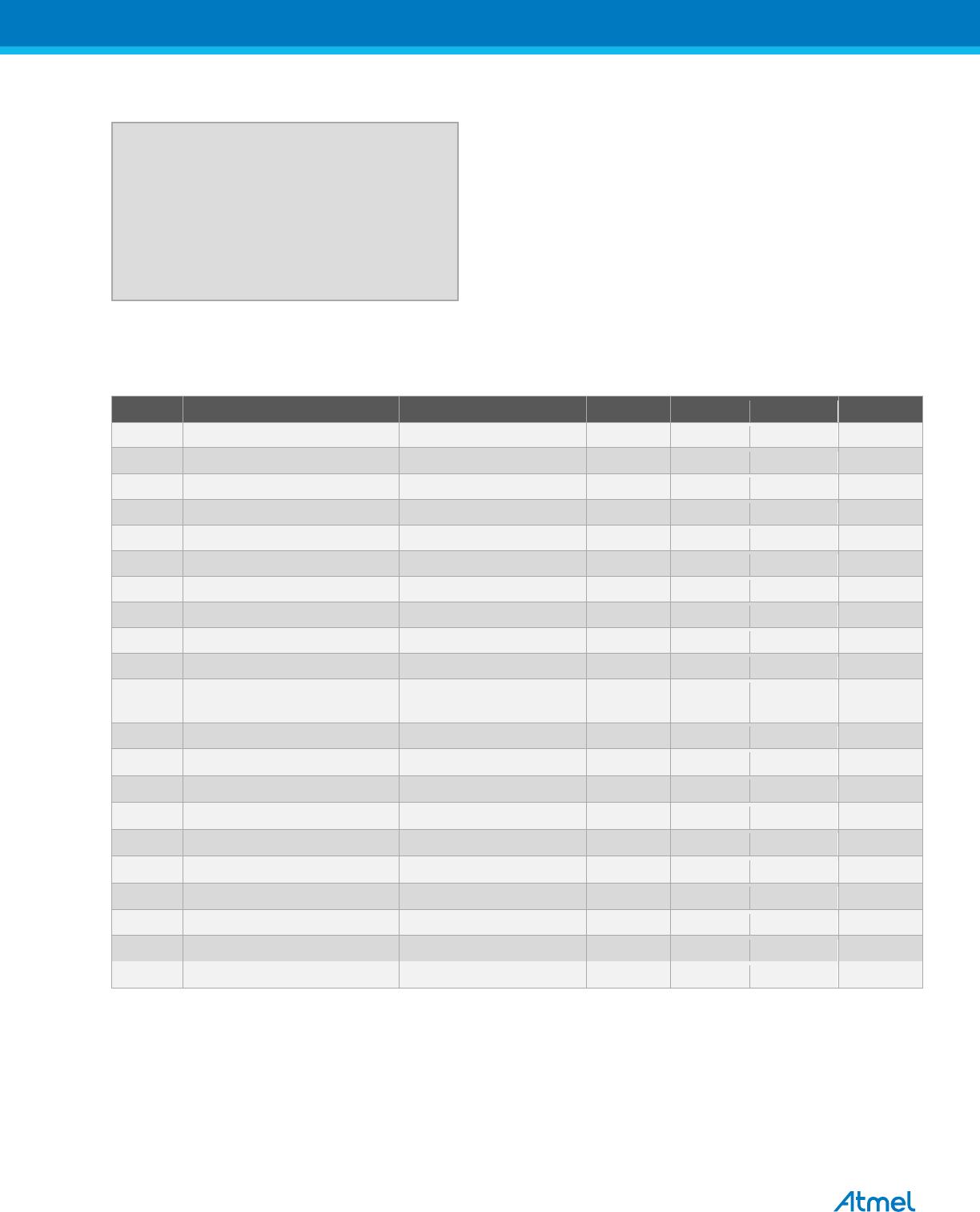

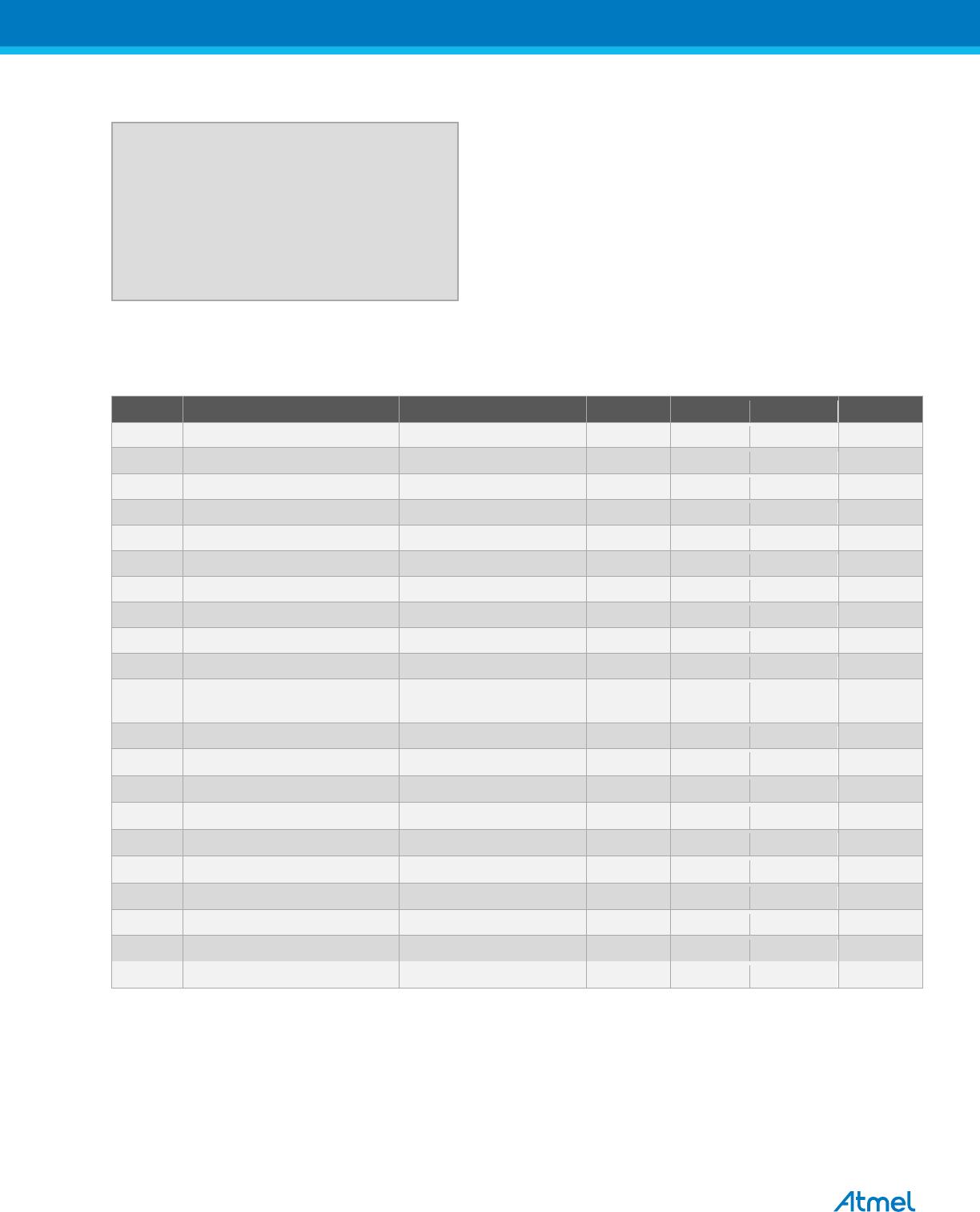

3. Absolute Maximum Ratings*

Operating Temperature .................. −40°C to +85°C

Storage Temperature .................. −65°C to + 150°C

Voltage on Any Pin

with Respect to Ground ............. − 0.7 to V

CC

+0.7V

Maximum Operating Voltage ........................... 6.0V

DC Output Current ........................................ 5.0mA

*NOTICE: Stresses beyond those listed under “Absolute

Maximum Ratings” may cause permanent damage to

the device. This is a stress rating only and functional

operation of the device at these or any other condition

beyond those indicated in the operational sections of

this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods of

time may affect device reliability.

Table 3-1. DC Characteristics

Applicable over recommended operating range from V

CC

= +2.7 to 5.5V, T

AC

= -40°C to +85°C (unless otherwise noted)

Symbol Parameter Test Condition Min Typ Max Units

V

CC

(2)

Supply Voltage 2.7 5.5 V

I

CC

Supply Current (V

CC

= 5.5V) Async Read at 3.57MHz 5 mA

I

CC

Supply Current (V

CC

= 5.5V) Async Write at 3.57MHz 5 mA

I

CC

Supply Current (V

CC

= 5.5V) Synch Read at 1MHz 5 mA

I

CC

Supply Current (V

CC

= 5.5V) Synch Write at 1MHz 5 mA

I

SB

Standby Current (V

CC

= 5.5V) V

IN

= V

CC

or GND 100 mA

V

IL

SDA/IO Input Low Threshold 0 V

CC

x 0.2 V

V

IL

SCL/CLK Input Low Threshold 0 V

CC

x 0.2 V

V

IL

RST Input Low Threshold 0 V

CC

x 0.2 V

V

IH

SDA/IO Input High Threshold V

CC

x 0.7 V

CC

V

V

IH

SCL/CLK Input High

Threshold

V

CC

x 0.7 V

CC

V

V

IH

(1)(2)

RST Input High Threshold V

CC

x 0.7 V

CC

V

I

IL

SDA/IO Input Low Current 0 < V

IL

< V

CC

x 0.15 15

µA

I

IL

SCL/CLK Input Low Current 0 < V

IL

< V

CC

x 0.15 15

µA

I

IL

RST Input Low Current 0 < V

IL

< V

CC

x 0.15 50

µA

I

IH

SDA/IO Input High Current V

CC

x 0.7 < V

IH

< V

CC

20

µA

I

IH

SCL/CLK Input High Current V

CC

x 0.7 < V

IH

< V

CC

100

µA

I

IH

RST Input High Current V

CC

x 0.7 < V

IH

< V

CC

150

µA

V

OH

SDA/IO Output High Voltage 20K ohm external pull-up V

CC

x 0.7 V

CC

V

V

OL

SDA/IO Output Low Voltage I

OL

= 1mA 0 V

CC

x 0.15 V

I

OH

SDA/IO Output High Current V

OH

20

µA

Notes: 1. V

IL

min and V

IH

max are reference only and are not tested

2. To prevent latch up conditions from occurring during power up of the AT88SCxxxxC, V

CC

must be turned on

before applying V

IH

. For powering down, V

IH

must be removed before turning V

CC

off