LTC1096/LTC1096L

LTC1098/LTC1098L

16

10968fc

The wake-up time is inherently provided for the LTC1098(L)

with setup time = 1μs (see Figure 2).

Data Transfer

The CLK synchronizes the data transfer with each bit being

transmitted on the falling CLK edge and captured on the

rising CLK edge in both transmitting and receiving sys-

tems. The LTC1098(L) fi rst receives input data and then

transmits back the A/D conversion result (half duplex).

Because of the half duplex operation, D

IN

and D

OUT

may

be tied together allowing transmission over just three

wires: CS, CLK and DATA (D

IN

/D

OUT

).

Data transfer is initiated by a falling chip select (CS) signal.

After CS falls the LTC1098(L) looks for a start bit. After the

start bit is received, the 3-bit input word is shifted into the

D

IN

input which confi gures the LTC1098(L) and starts the

conversion. After one null bit, the result of the conversion

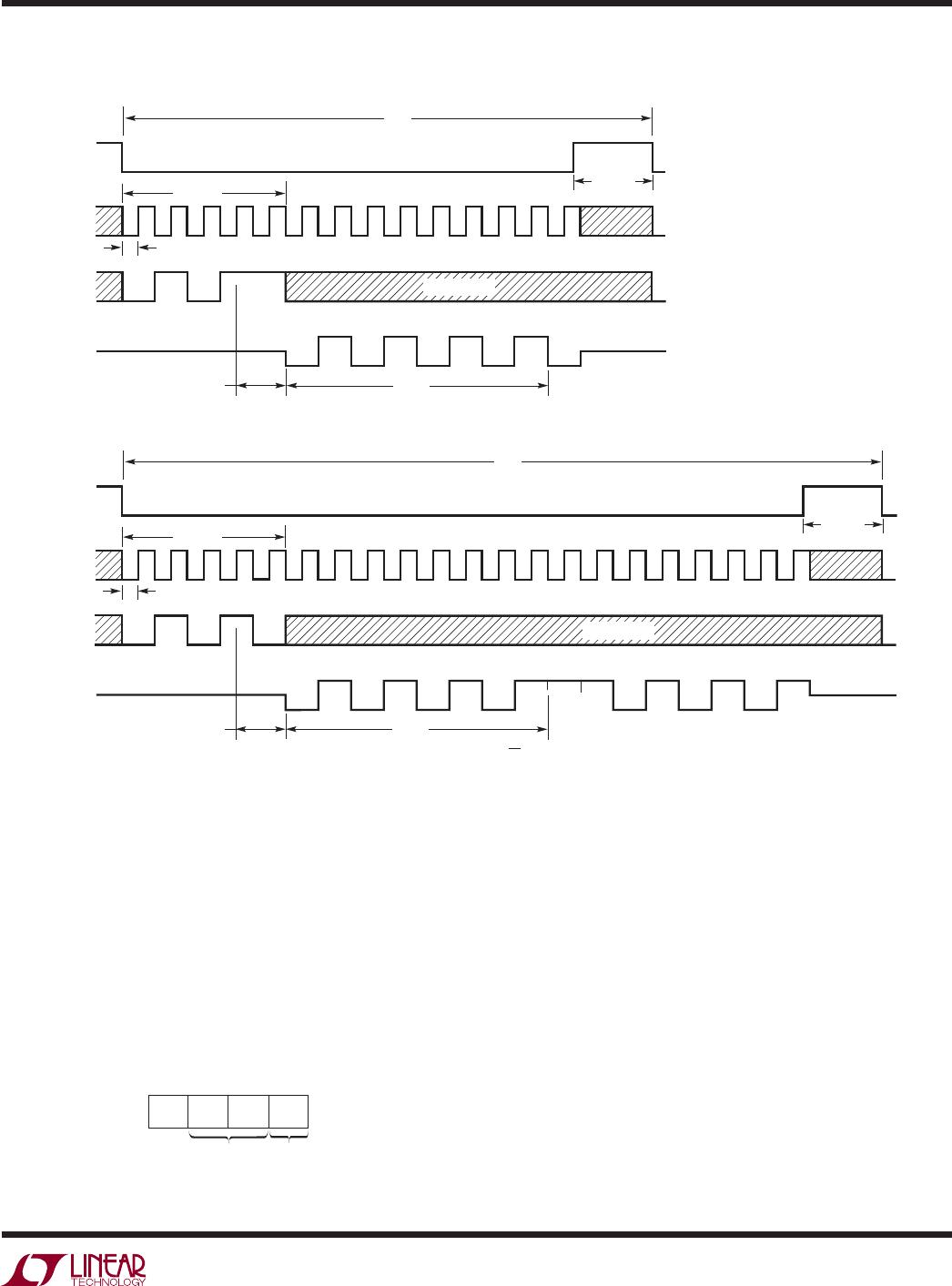

Figure 1. LTC1096(L) Operating Sequence

is output on the D

OUT

line. At the end of the data exchange

CS should be brought high. This resets the LTC1098(L) in

preparation for the next data exchange.

The LTC1096(L) does not require a confi guration input

word and has no D

IN

pin. A falling CS initiates data trans-

feras shown in the LTC1096(L) operating sequence. After

CS falls, the fi rst CLK pulse enables D

OUT

. After one null

bit, the A/D conversion result is output on the D

OUT

line.

Bringing CS high resets the LTC1096(L) for the next data

exchange.

CLK

t

CYC

CS

B7*B6B5

B4

B3

B2B1

B0

B1

B2

B3B4B5

B6

B7

NULL

BIT

Hi-Z

D

OUT

10968 F01

POWER

DOWN

Hi-Z

t

suCS

t

WAKEUP

t

CONV

CLK

CS

t

CYC

POWER

DOWN

t

WAKEUP

B0

B1

B2

B3

B4B5

B6B7

Hi-Z

D

OUT

t

CONV

HI-Z

t

suCS

NULL

BIT

*AFTER COMPLETING THE DATA TRANSFER, IF FURTHER CLOCKS ARE APPLIED WITH CS LOW, THE ADC WILL OUTPUT ZEROS INDEFINITELY.

(MSB)

(MSB)

APPLICATIONS INFORMATION

D

IN

1 D

IN

2

D

OUT

1 D

OUT

2

CS

SHIFT MUX

ADDRESS IN

1 NULL BIT

SHIFT A/D CONVERSION

RESULT OUT

10968 AI01