XCR3256XL 256 Macrocell CPLD

4 www.xilinx.com DS013 (v2.7) March 31, 2006

Product Specification

R

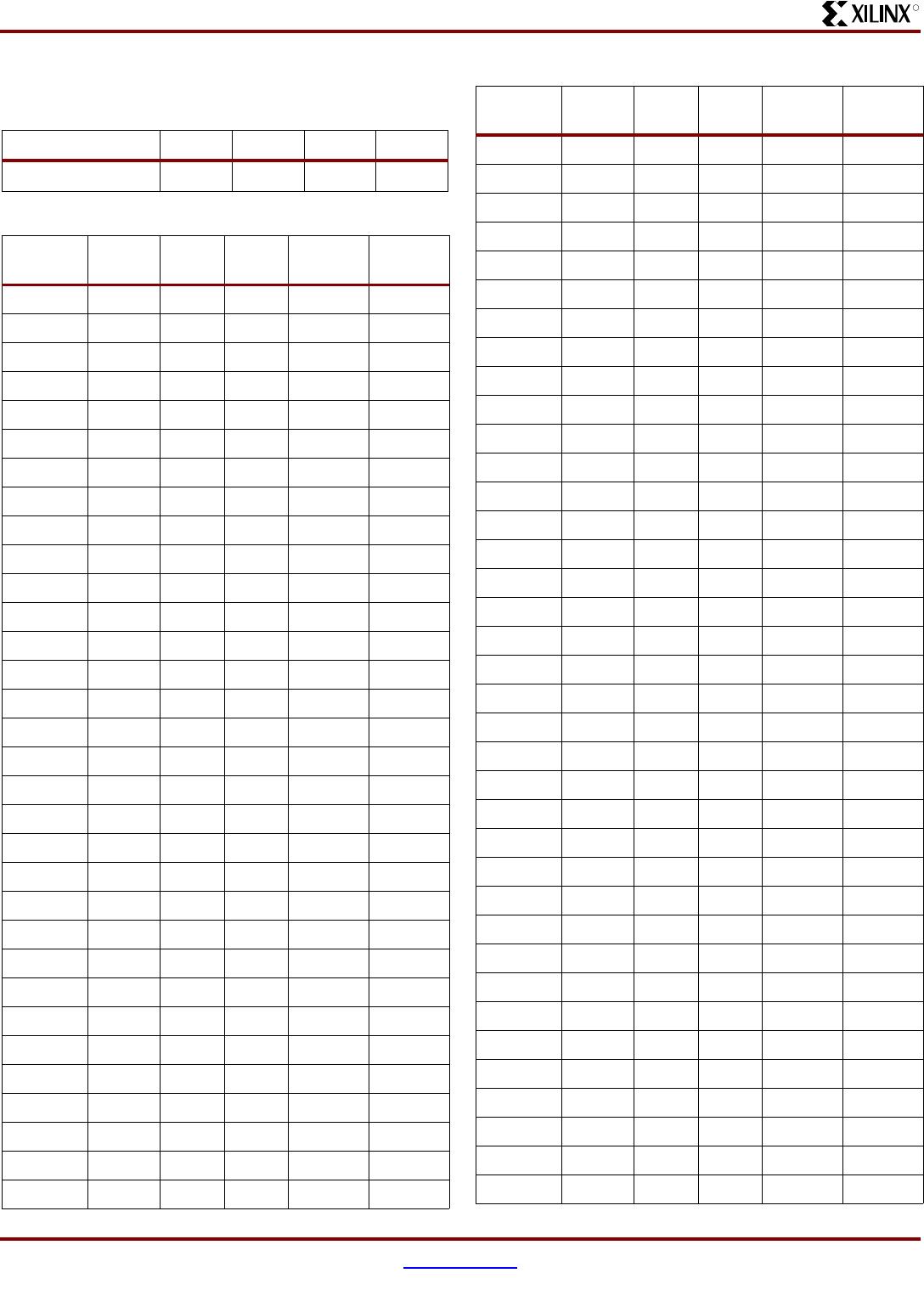

Internal Timing Parameters

(1,2)

Symbol Parameter

-7 -10 -12

UnitMin. Max. Min. Max. Min. Max.

Buffer Delays

T

IN

Input buffer delay - 2.5 - 3.3 - 4.0 ns

T

FIN

Fast input buffer delay - 2.7 - 3.3 - 3.3 ns

T

GCK

Global clock buffer delay - 1.0 - 1.3 - 1.5 ns

T

OUT

Output buffer delay - 2.5 - 3.2 - 3.8 ns

T

EN

Output buffer enable/disable delay - 4.5 - 5.2 - 6.0 ns

Internal Register and Combinatorial Delays

T

LDI

Latch transparent delay - 1.3 - 1.6 - 2.0 ns

T

SUI

Register setup time 0.8 - 1.0 - 1.2 - ns

T

HI

Register hold time 0.3 - 0.5 - 0.7 - ns

T

ECSU

Register clock enable setup time 2.0 - 2.5 - 3.0 - ns

T

ECHO

Register clock enable hold time 3.0 - 4.5 - 5.5 - ns

T

COI

Register clock to output delay - 1.0 - 1.3 - 1.6 ns

T

AOI

Register async. S/R to output delay - 2.0 - 2.0 - 2.2 ns

T

RAI

Register async. recovery - 5.0 - 7.0 - 8.0 ns

T

PTCK

Product term clock delay - 2.0 - 2.5 - 3.0 ns

T

LOGI1

Internal logic delay (single p-term) - 2.0 - 2.5 - 3.0 ns

T

LOGI2

Internal logic delay (PLA OR term) - 2.5 - 3.5 - 4.2 ns

Feedback Delays

T

F

ZIA delay - 2.2 - 3.7 - 4.4 ns

Time Adders

T

LOGI3

Fold-back NAND delay - 2.0 - 2.5 - 3.0 ns

T

UDA

Universal delay - 2.0 - 2.5 - 3.0 ns

T

SLEW

Slew rate limited delay - 4.0 - 5.0 - 6.0 ns

Notes:

1. These parameters guaranteed by design and/or characterization, not testing.

2. See the CoolRunner XPLA3 family data sheet (

DS012) for the timing model.