1

Zarlink Semiconductor Inc.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2007, Zarlink Semiconductor Inc. All Rights Reserved.

A full Data Sheet is available to qualified customers. To

register, please send an email to

TimingandSync@zarlink.com.

Features

• Single chip low cost solution for synchronizing an

Ethernet PHY to a standard telecom clock

• Generates an IEEE 802.3 jitter compliant 25 MHz

Gigabit Ethernet output clock

• Supports three modes of operation:

Asynchronous Freerun, Synchronous, and

Asynchronous Holdover

• Defaults in Asynchronous Freerun mode

• In Asynchronous Freerun mode, the DPLL

generates an output clock with a frequency

accuracy equal to frequency accuracy of the

external crystal oscillator (XO) or a low cost

crystal (XTAL)

• In Synchronous mode, the DPLL automatically

synchronizes to one of a pre-defined set of

frequencies including 2 kHz, 8 kHz, 64 kHz,

1.544 MHz, 2.048 MHz, 6.48 MHz, 8.192 MHz,

16.384 MHz, 19.44 MHz, 38.88 MHz, 77.76 MHz.

• Configurable to accept a 25 MHz input reference

• Automatic entry into Asynchronous Holdover

mode when all input references fail

• Input reference is manually selectable through the

serial (SPI) interface

• Hitless input reference switching

• Lock indicator pin

• Input reference status monitors

• Programmable loop bandwidth of 14 Hz, 28 Hz, or

890 Hz

Applications

• Ethernet Line Cards Supporting Synchronous

Transmission

March 2007

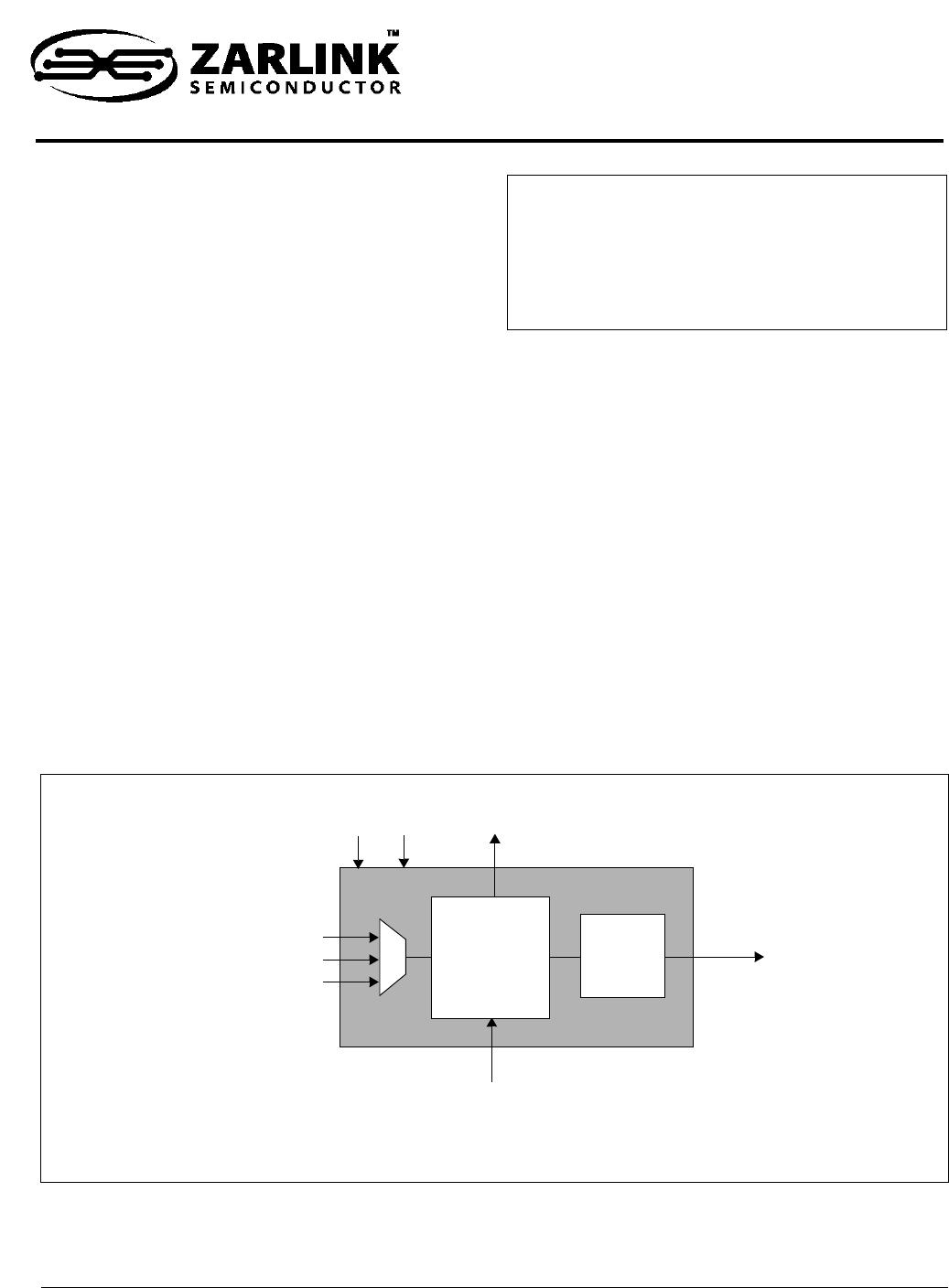

Figure 1 - Block Diagram

LOCK

CLK

X1/CLK

X2

uP I/F

DPLL

APLL

REF0

REF1

REF2

ZL30107

GbE Line Card Synchronizer

Shortform Data Sheet

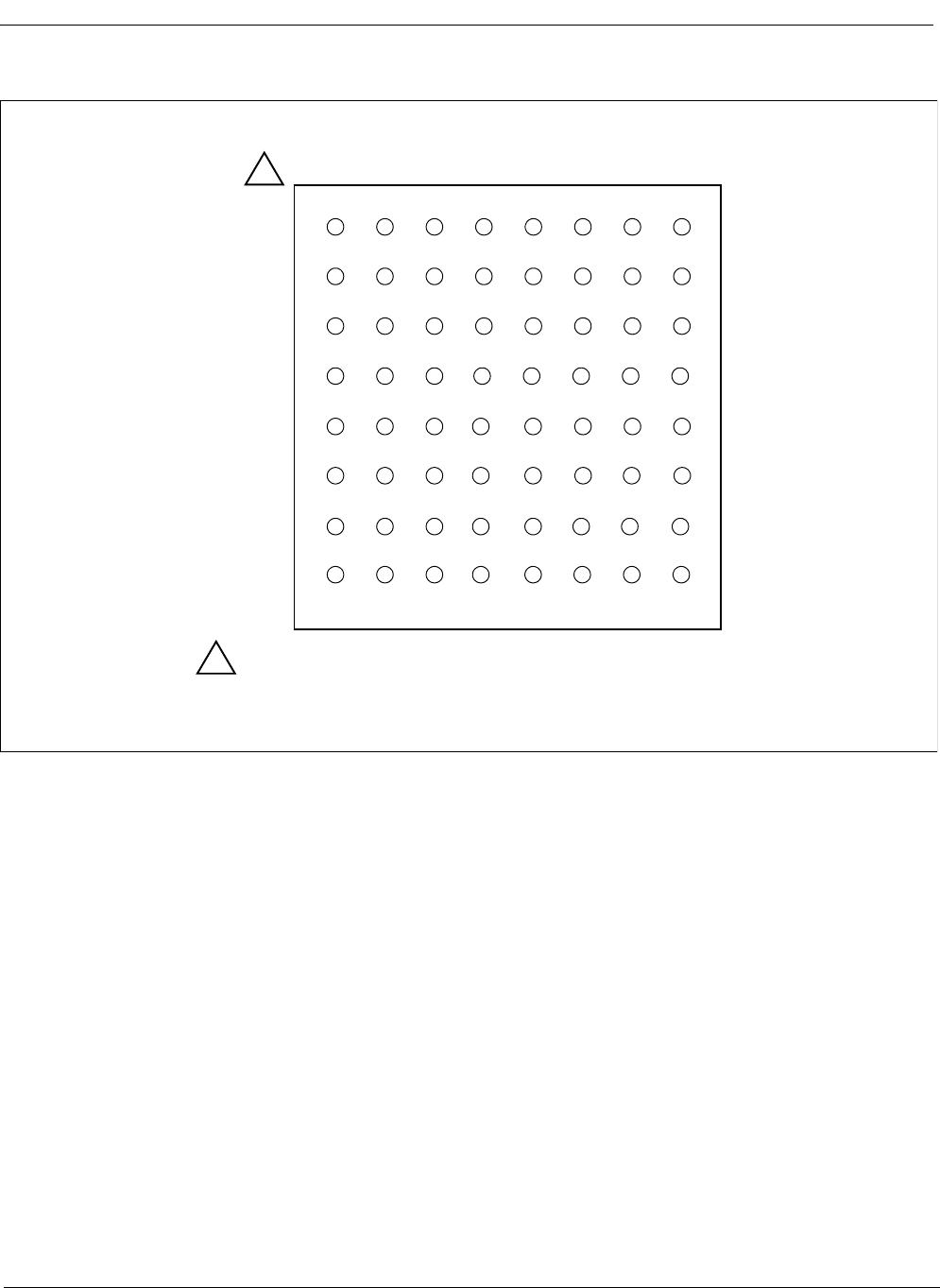

Ordering Information

ZL30107GGG 64 Pin CABGA Trays

ZL30107GGG2 64 Pin CABGA* Trays

*Pb Free Tin/Silver/Copper

-40

o

C to +85

o

C