33

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72V36100/72V36110 3.3V HIGH DENSITY SUPERSYNC II

TM

36-BIT FIFO

65,536 x 36 and 131,072 x 36

NOTES:

1. If the part is empty at the point of Retransmit, the empty flag (EF) will be updated based on RCLK (Retransmit clock cycle), valid data will also appear on the output.

2. OE = LOW.

3. W1 = first word written to the FIFO after Master Reset, W2 = second word written to the FIFO after Master Reset.

4. No more than D - 2 may be written to the FIFO between Reset (Master or Partial) and Retransmit setup. Therefore, FF will be HIGH throughout the Retransmit setup procedure.

D = 65,536 for the IDT72V36100 and 131,072 for the IDT72V36110.

5. There must be at least two words written to the FIFO before a Retransmit operation can be invoked.

6. RM is set LOW during MRS.

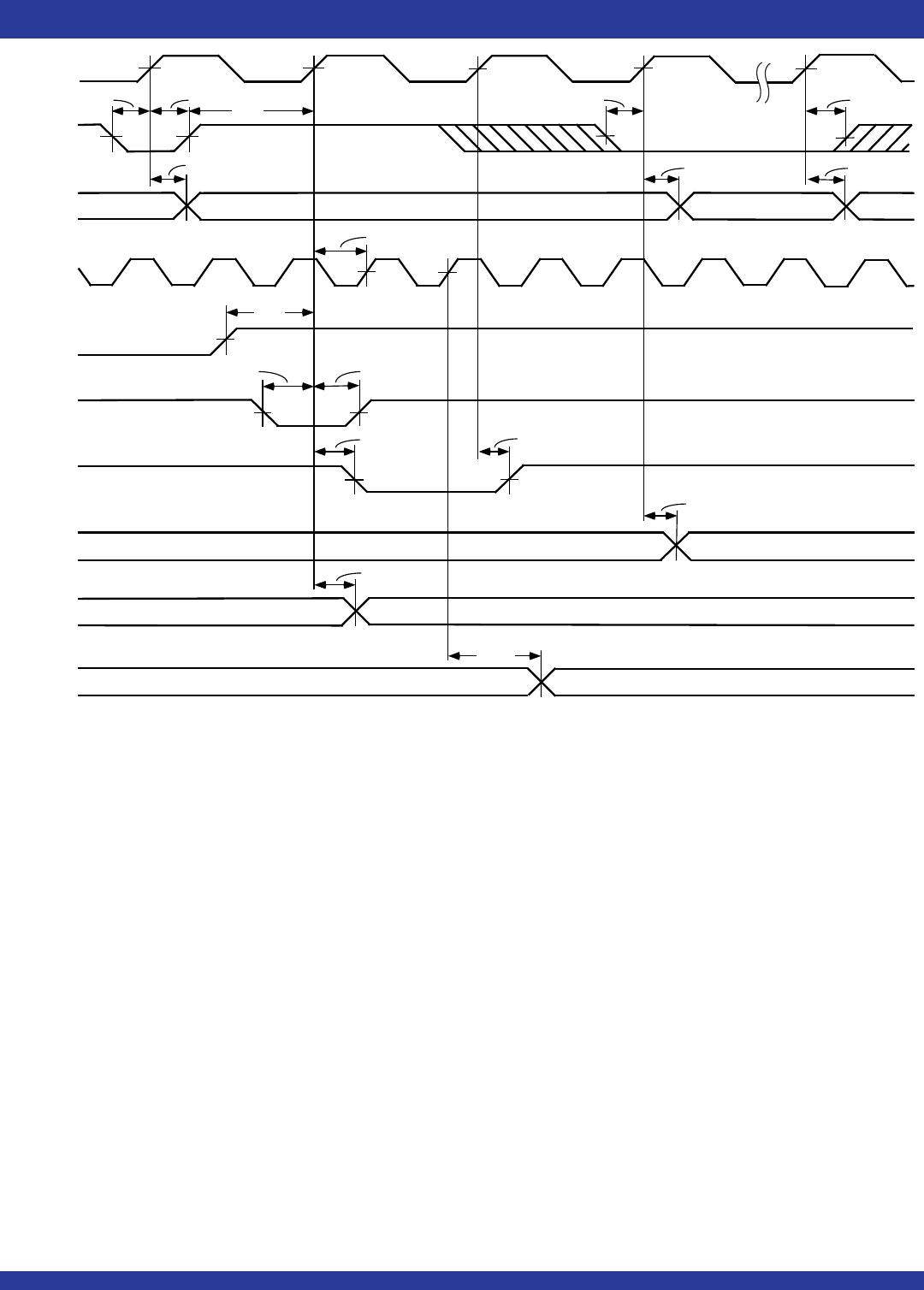

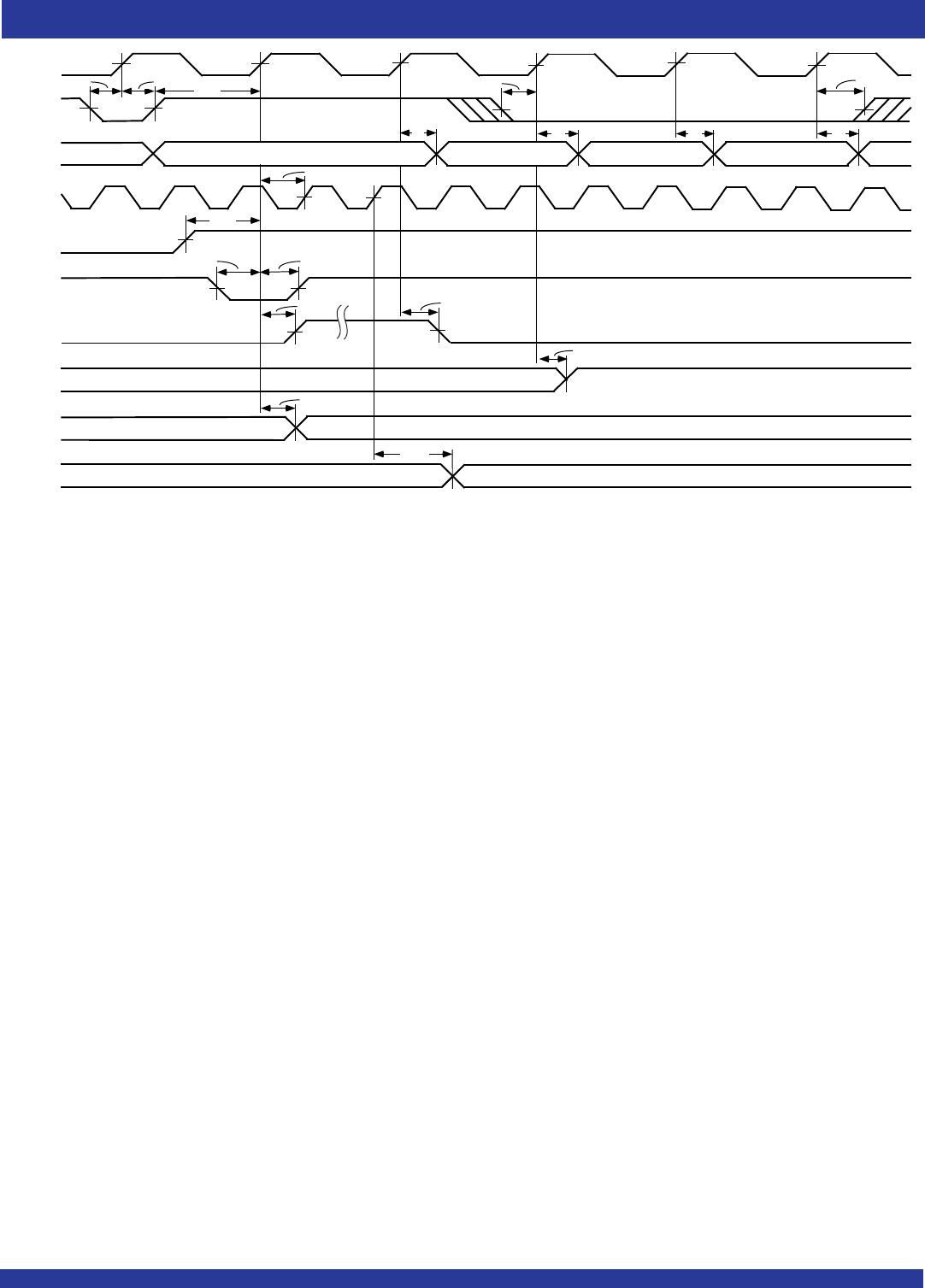

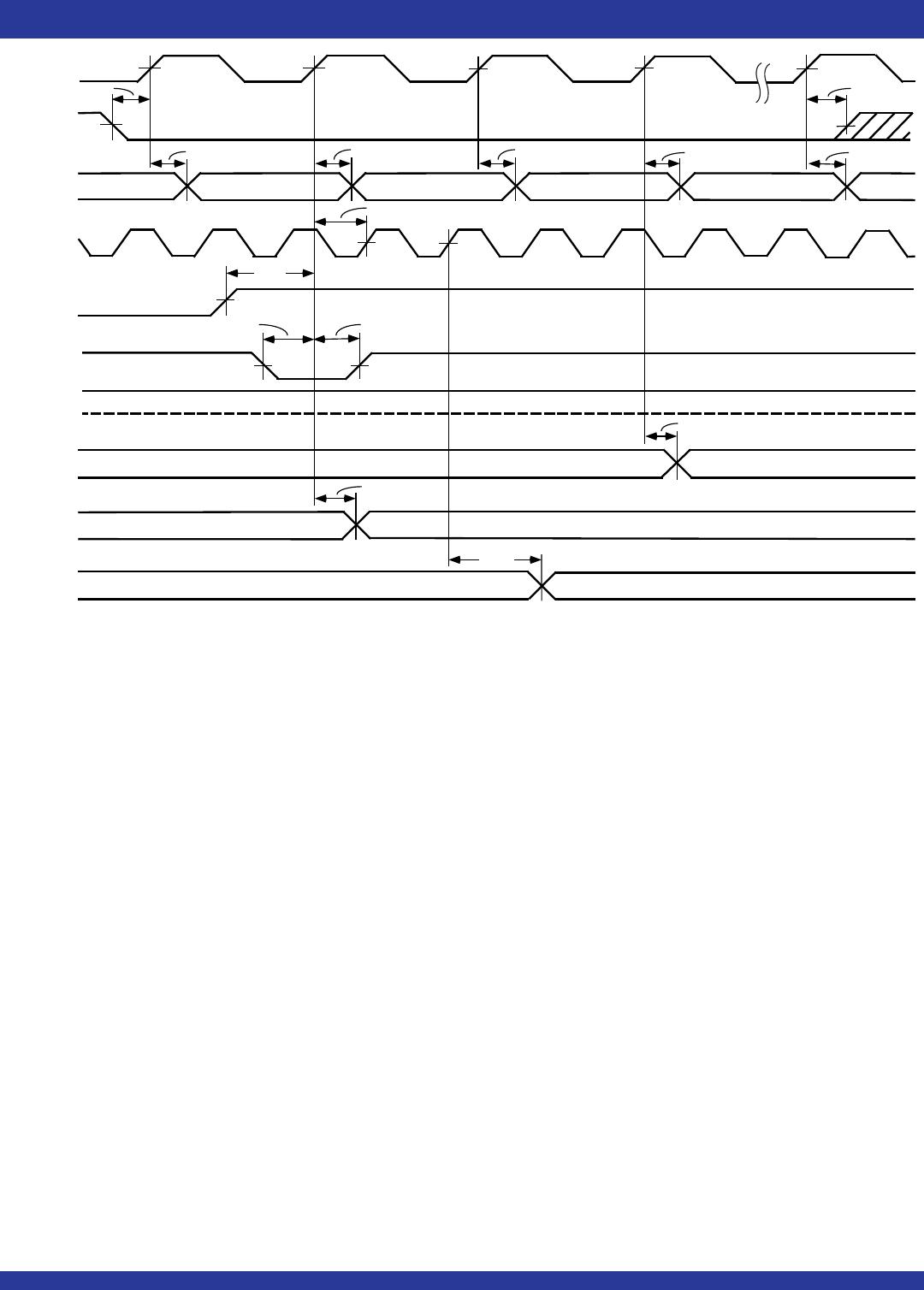

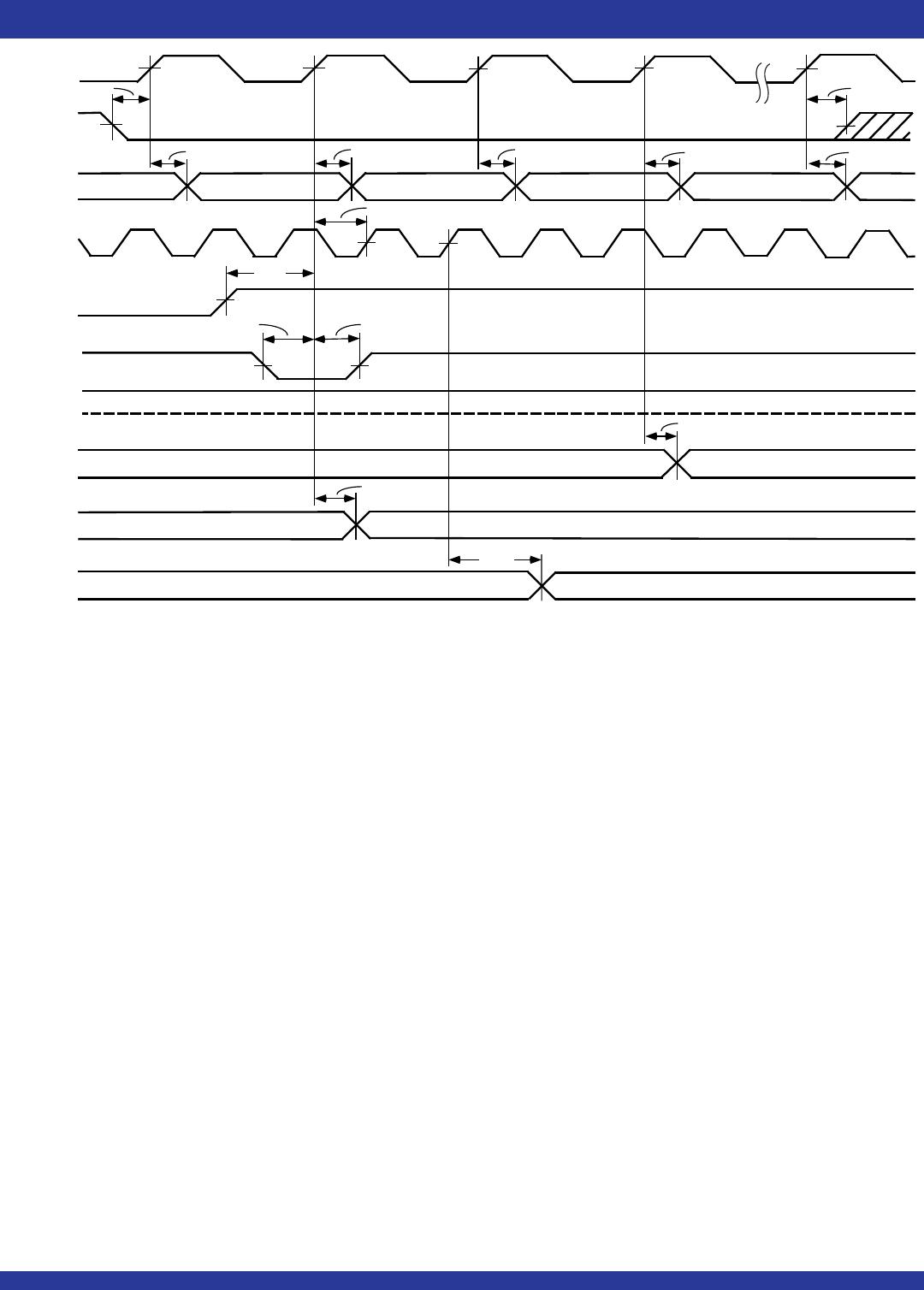

Figure 13. Zero Latency Retransmit Timing (IDT Standard Mode)

t

RTS

t

ENH

6117 drw18

t

A

t

ENS

W

x

WCLK

RCLK

REN

RT

EF

PAF

HF

PAE

Q

0

- Q

n

t

SKEW2

12

1

W

3

(3)

t

PAFS

t

HF

t

PAES

W

x+1

2

W

4

WEN

t

ENS

t

ENH

t

A

t

A

3

t

A

t

A

W

2

(3)

W

1

(3)