25

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72V36100/72V36110 3.3V HIGH DENSITY SUPERSYNC II

TM

36-BIT FIFO

65,536 x 36 and 131,072 x 36

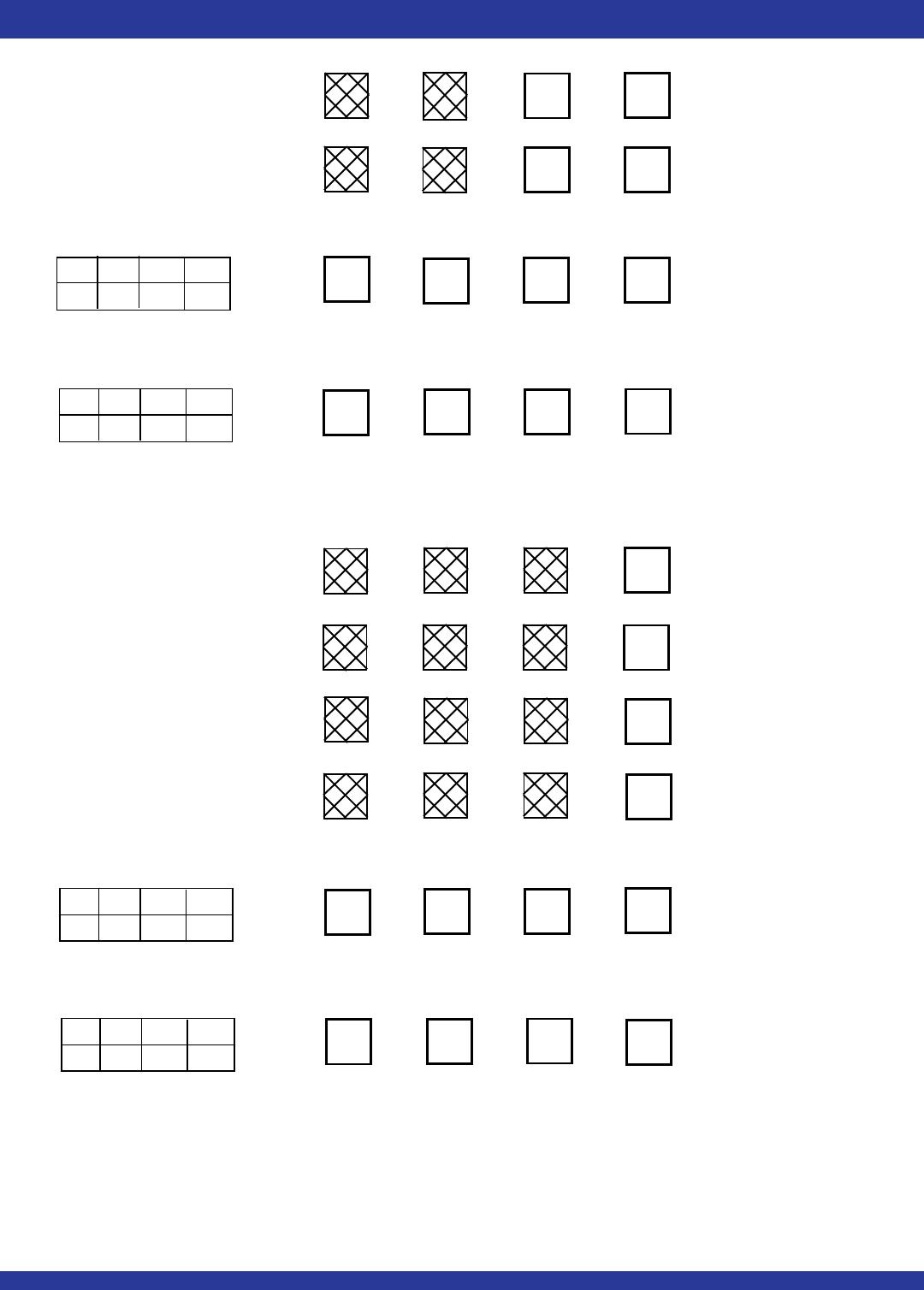

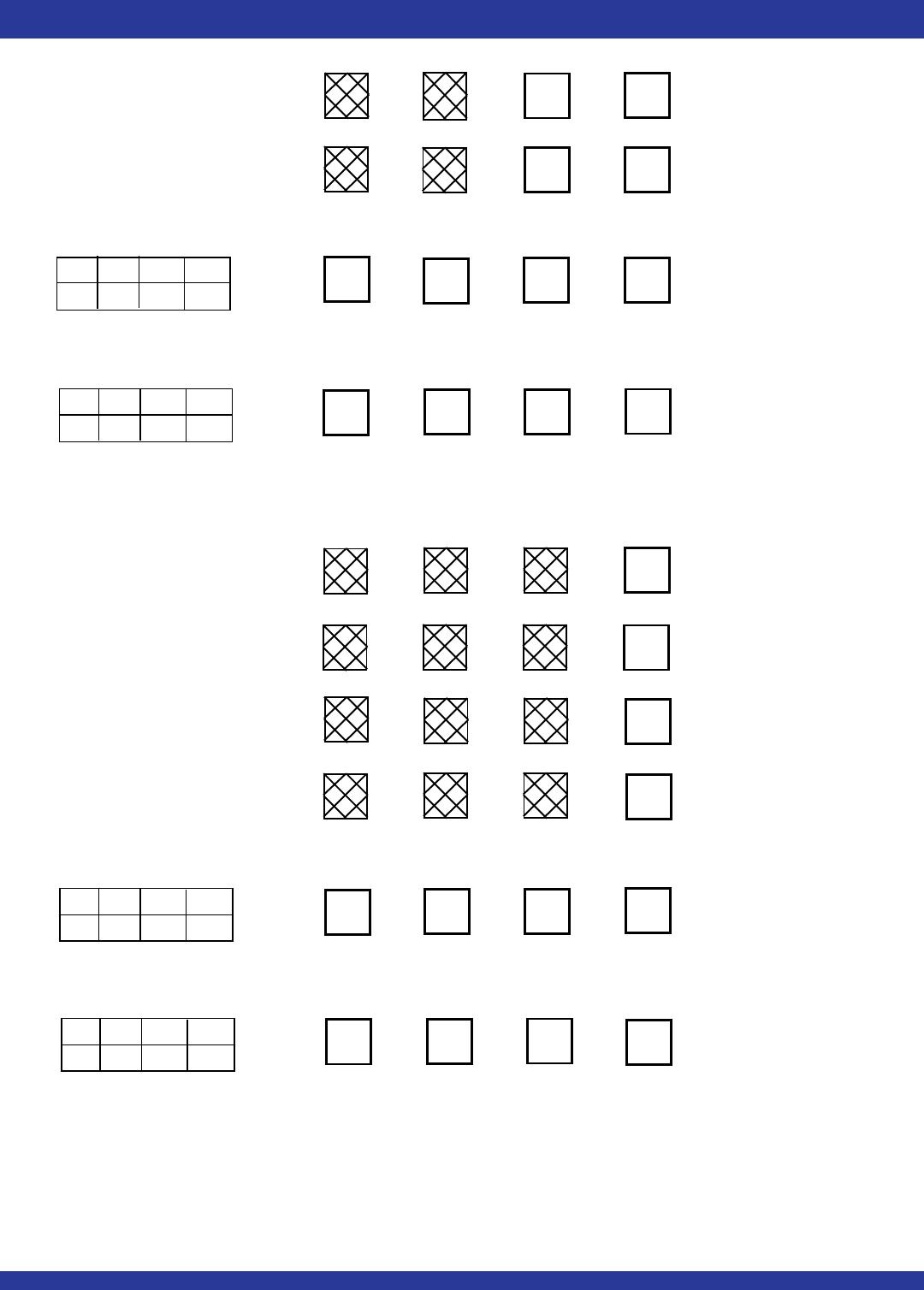

Q35-Q27 Q26-Q18 Q17-Q9 Q8-Q0

A

A

D

A

C

B

B

C

B

D

C

D

D35-D27 D26-D18 D17-D9 D8-D0

(a) x18 INPUT to x36 OUTPUT - BIG-ENDIAN

Read from FIFO

1st: Write to FIFO

BYTE ORDER ON INPUT PORT:

2nd: Write to FIFO

3rd: Write to FIFO

4th: Write to FIFO

D35-D27 D26-D18 D17-D9 D8-D0

1st: Write to FIFO

2nd: Write to FIFO

6117 drw09

BYTE ORDER ON OUTPUT PORT:

Q35-Q27 Q26-Q18 Q17-Q9 Q8-Q0

C

D

A

B

(b) x18 INPUT to x36 OUTPUT - LITTLE-ENDIAN

Read from FIFO

BE BM IW OW

H H H L

BYTE ORDER ON INPUT PORT:

ABCD

(a) x9 INPUT to x36 OUTPUT - BIG-ENDIAN

Read from FIFO

BE BM IW OW

L H H H

BYTE ORDER ON OUTPUT PORT:

D

C

B

A

(b) x9 INPUT to x36 OUTPUT - LITTLE-ENDIAN

Read from FIFO

BE BM IW OW

H H H H

BE BM IW OW

L H H L

D35-D27 D26-D18 D17-D9 D8-D0

D35-D27 D26-D18 D17-D9 D8-D0

D35-D27 D26-D18 D17-D9 D8-D0

D35-D27 D26-D18 D17-D9 D8-D0

Q35-Q27 Q26-Q18 Q17-Q9 Q8-Q0

Q35-Q27 Q26-Q18 Q17-Q9 Q8-Q0

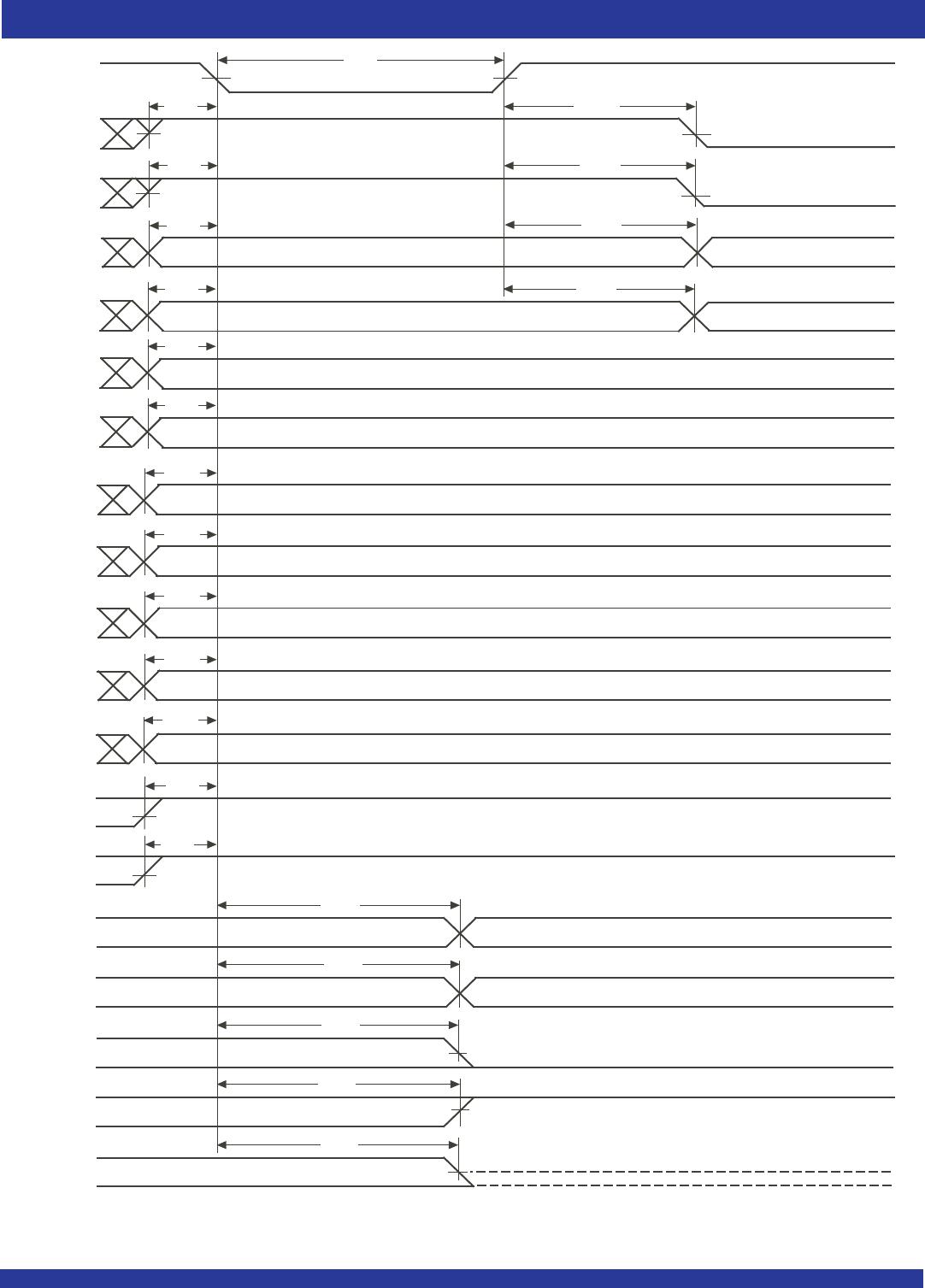

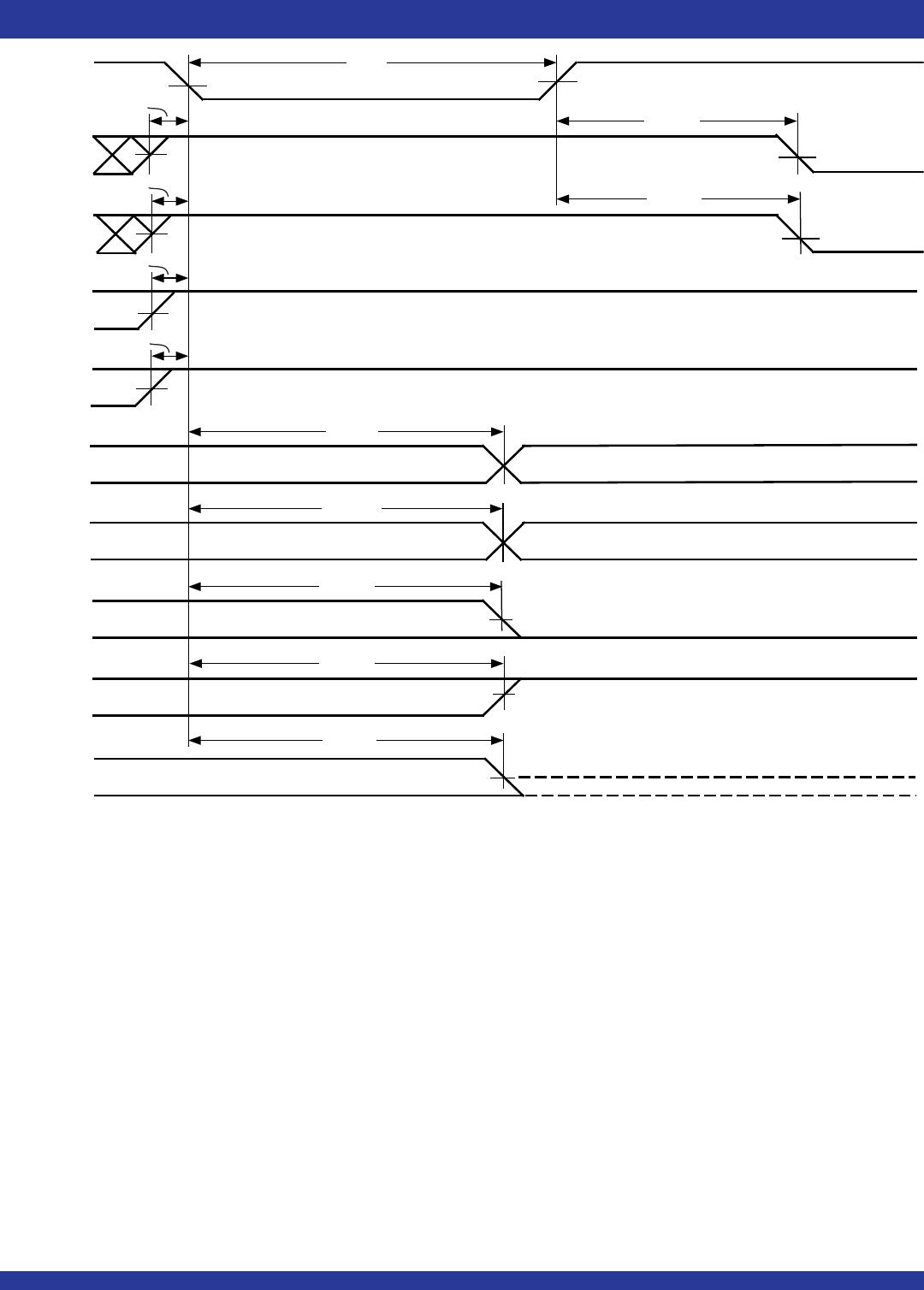

Figure 4. Bus-Matching Byte Arrangement (Continued)