Critical Link, LLC MitySOM

www.criticallink.com MitySOM-1808 Processor Card

5-MAR-2014

7 Copyright © 2013, Critical Link LLC

Specifications Subject to Change

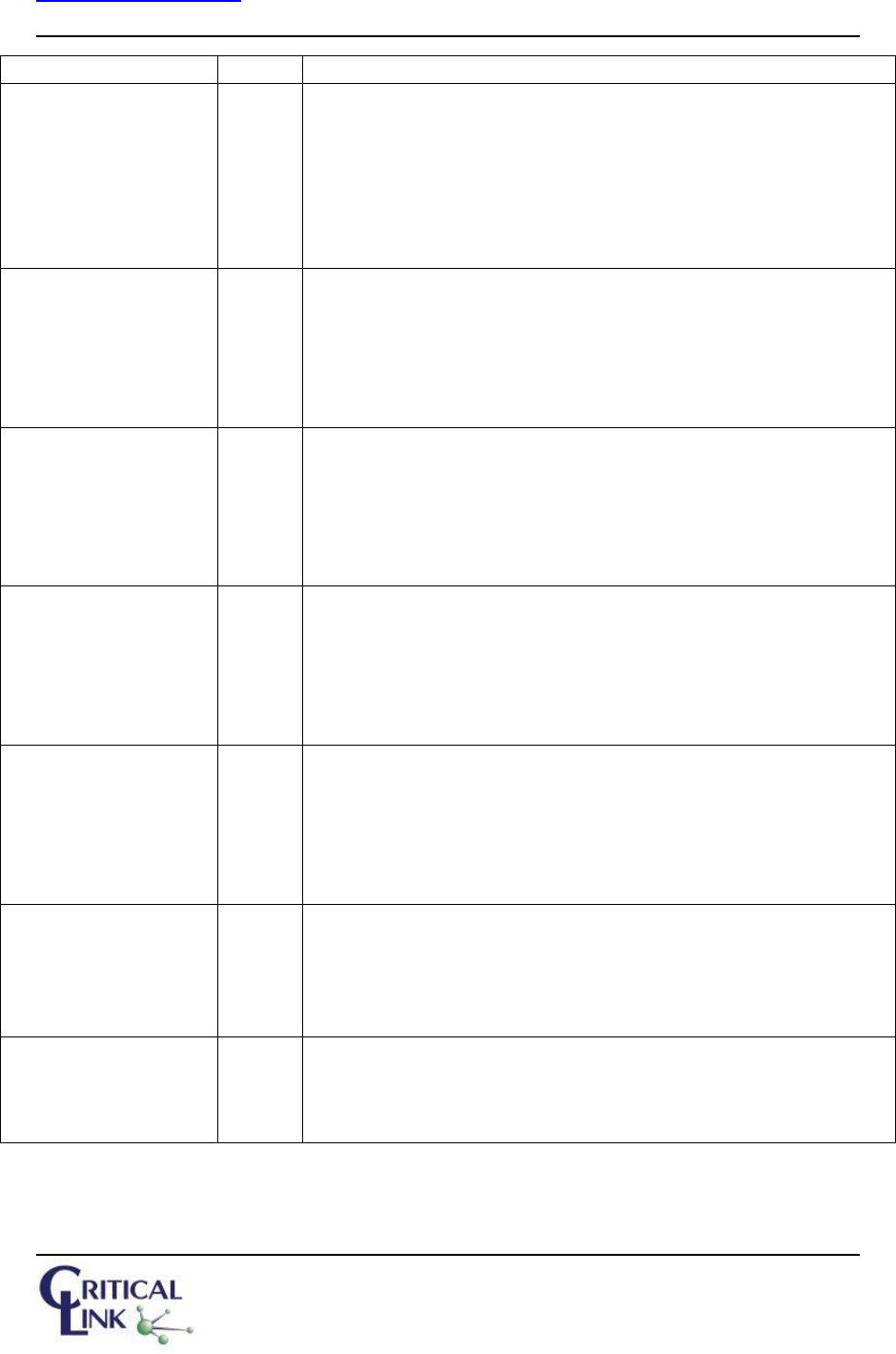

Table 2 Signal Group Description

3.3 volt input power referenced to GND.

Bootstrap configuration pin. Pull low to configure booting

from external UART1.

Manual Reset. When pulled to GND for a minimum of 1

usec, resets the processor.

Serial Peripheral Interface 1 pins.

These pins are direct connects to the corresponding SPI1_*

pins on the AM1808 processor. The SPI1_* function pins are

multiplexed with other functions. These include PWM,

Timers, UARTs, I2C0, and GPIO. For details please refer to

the AM1808 processor specifications.

Media Independent Interface (Ethernet) pins.

These pins are direct connects to the corresponding MII_*

pins on the AM1808 processor. The MII_* function pins are

multiplexed with other functions. These include SPI0, PWM,

Timers, UART0, MCBSP, MCASP, and GPIO. For details

please refer to the AM1808 processor specifications.

MII/RMII Management Interface pins.

The MDIO_CLK and MDIO_DAT signals are direct connects

to the corresponding MDIO_* signals on the AM1808

processor. The MDIO_* function pins are multiplexed with

other functions. These include SPI0 and Timer functions.

For details please refer to the AM1808 processor

specifications.

General Purpose / multiplexed pins. These pins are direct

connects to the corresponding GP0[*] pins on the AM1808

processor. The include support for the McASP, general

purpose I/O, UART flow control, and McBSP 1. For details

please refer to the AM1808 processor specifications.

Serial ATA Controller Transmit pins.

These pins are direct connects to the corresponding

SATA_TX_* pins on the AM1808 processor. For details

please refer to the AM1808 processor specifications.

Serial ATA Controller Receive pins.

These pins are direct connects to the corresponding

SATA_RX_* pins on the AM1808 processor. For details

please refer to the AM1808 processor specifications.