XC2C384 CoolRunner-II CPLD

24 www.xilinx.com DS095 (v3.2) March 8, 2007

Product Specification

R

Warranty Disclaimer

THESE PRODUCTS ARE SUBJECT TO THE TERMS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED

AT http://www.xilinx.com/warranty.htm

. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF THE

PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED ON THE

THEN-CURRENT XILINX DATA SHEET FOR THE PRODUCTS. PRODUCTS ARE NOT DESIGNED TO BE FAIL-SAFE

AND ARE NOT WARRANTED FOR USE IN APPLICATIONS THAT POSE A RISK OF PHYSICAL HARM OR LOSS OF

LIFE. USE OF PRODUCTS IN SUCH APPLICATIONS IS FULLY AT THE RISK OF CUSTOMER SUBJECT TO

APPLICABLE LAWS AND REGULATIONS.

Additional Information

Additional information is available for the following CoolRunner-II topics:

• XAPP784: Bulletproof CPLD Design Practices

• XAPP375: Timing Model

• XAPP376: Logic Engine

• XAPP378: Advanced Features

• XAPP382: I/O Characteristics

• XAPP389: Powering CoolRunner-II

• XAPP399: Assigning VREF Pins

To access these and all application notes with their associ-

ated reference designs, click the following link and scroll

down the page until you find the document you want:

CoolRunner-II Data Sheets and Application Notes

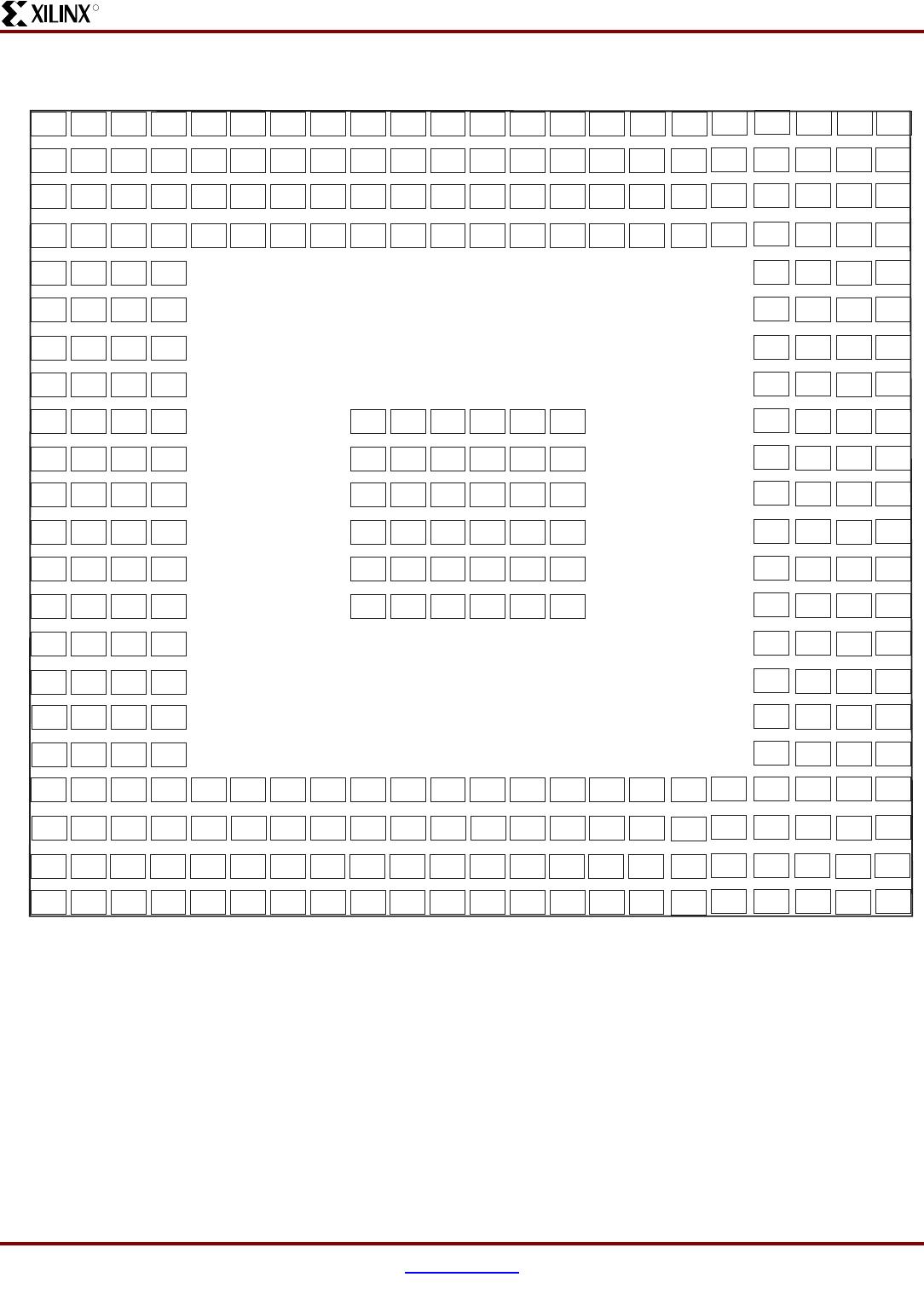

Device Packages

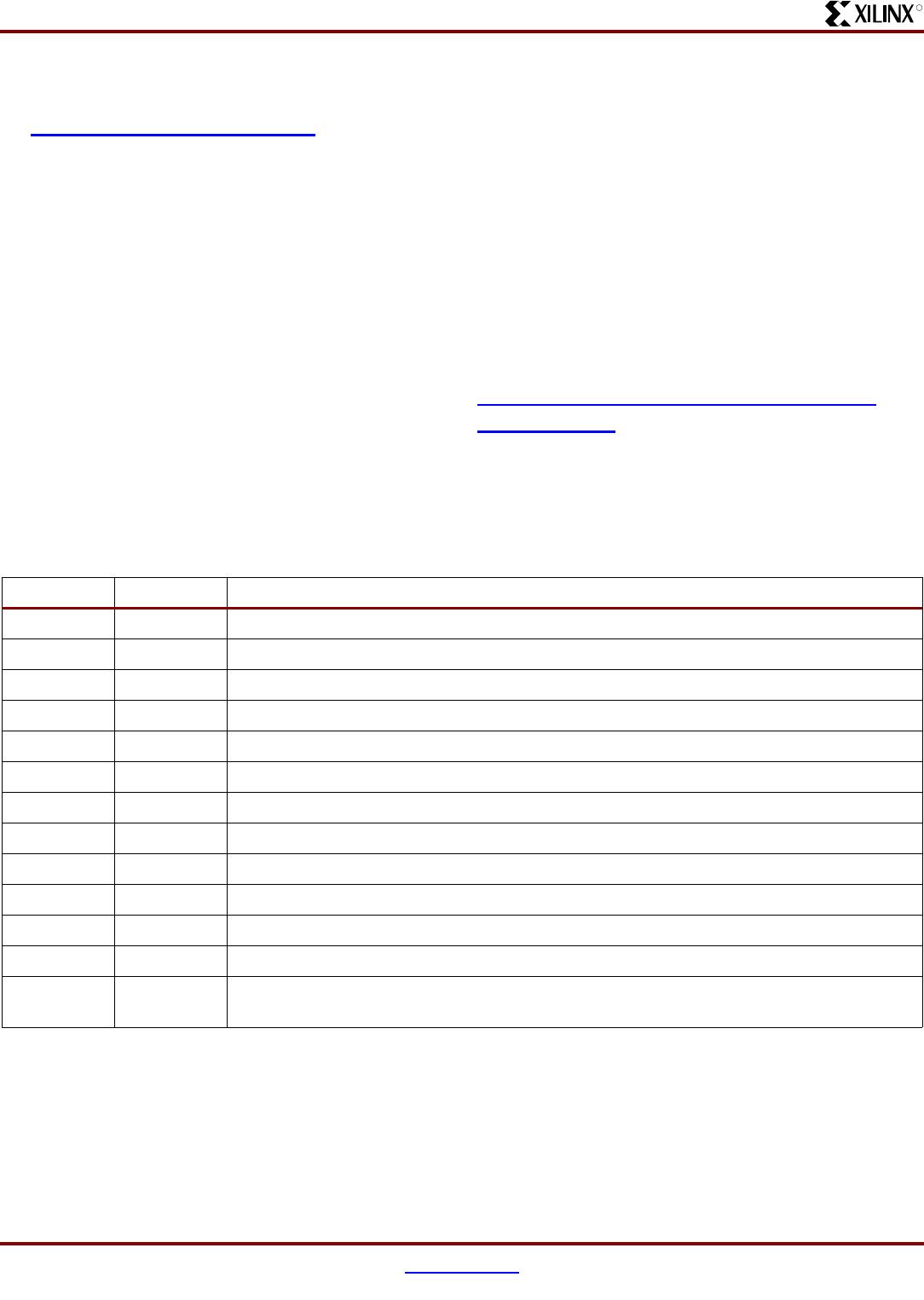

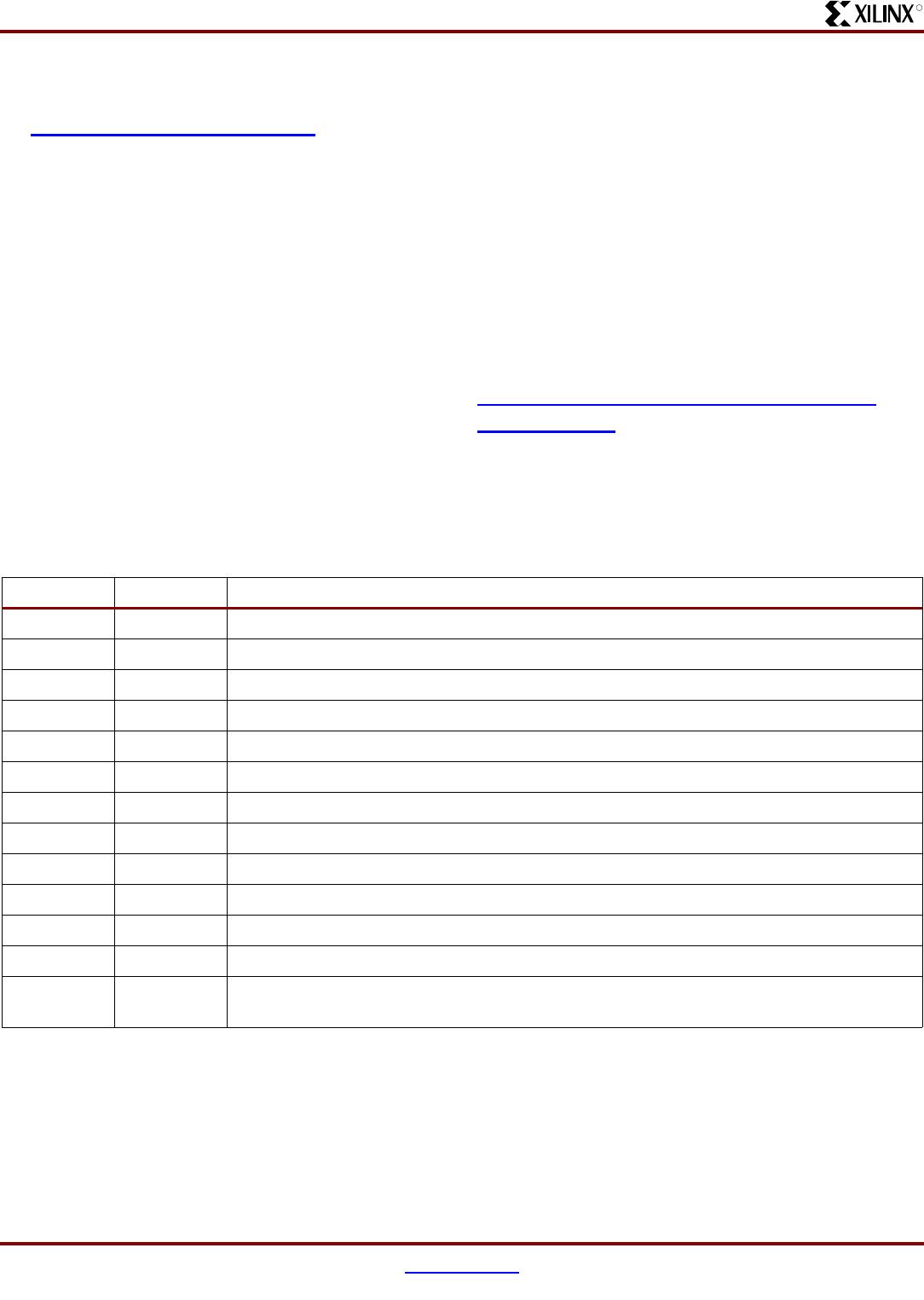

Revision History

The following table shows the revision history for this document.

Date Version Revision

5/31/02 1.0 Initial Xilinx release

9/23/02 1.1 Updated FT256 and TQ144 pinouts

4/16/03 1.2 Updated FG324 package, updated No Connect pins

5/30/03 2.0 Added -6, -10 characterization data

11/7/03 2.1 Corrected typo on page 1. 324-ball FG BGA package has ball pitch of 1.0mm

1/26/04 2.2 Added links to Application notes and Data sheets

5/7/04 2.3 Corrected error in package dimensions of XC2C384-10TQ144I

8/03/04 2.4 Pb-free documentation

10/01/04 2.5 Add Asynchronous Preset/Reset Pulse Width specification to AC Electrical Characteristics

01/30/05 2.6 Change to I

CCSB

MAX for Industrial devices

03/07/05 2.7 Deleted -6 speed grade. Modifications to Table 1, IOSTANDARDs

2/06/06 2.8 Change to T

SUI

for -7 speed grade. Previous value was typographical error

03/20/06 2.9 Add Warranty Disclaimer. Add note to Pin Descriptions that

GCK, GSR, and GTS pins can also

be used for general purpose I/O