1

DATASHEET

Dual LDO with Low Noise, Very High PSRR and Low I

Q

ISL9000A

ISL9000A is a high performance dual LDO capable of sourcing

300mA current from each output. It has a low standby current

and very high PSRR and is stable with output capacitance of

1µF to 10µF with ESR of up to 200m.

The device integrates an individual Power-On-Reset (POR)

function for each output. The POR delay for VO2 can be

externally programmed by connecting a timing capacitor to the

CPOR pin. The POR delay for VO1 is internally fixed at

approximately 2ms. A reference bypass pin is also provided for

connecting a noise filtering capacitor for low noise and high-

PSRR applications.

The quiescent current is typically only 42µA with both LDO’s

enabled and active. Separate enable pins control each

individual LDO output. When both enable pins are low, the

device is in shutdown, typically drawing less than 0.1µA.

Several combinations of voltage outputs are standard. Output

voltage options for each LDO range from 1.5V to 3.3V. Other

output voltage options may be available upon request.

Features

• Integrates two 300mA high performance LDOs

• Excellent transient response to large current steps

• ±1.8% accuracy over all operating conditions

• Excellent load regulation: < 0.1% voltage change across full

range of load current

• Low output noise: typically 30µV

RMS

@ 100µA (1.5V)

• Very high PSRR: 90dB @ 1kHz

• Extremely low quiescent current: 42µA (both LDOs active)

• Wide input voltage capability: 2.3V to 6.5V

• Low dropout voltage: typically 200mV @ 300mA

• Stable with 1µF to 10µF ceramic capacitors

• Separate enable and POR pins for each LDO

• Soft-start and staged turn-on to limit input current surge

during enable

• Current limit and overheat protection

• Tiny 10 Ld 3mmx3mm DFN package

• -40°C to +85°C operating temperature range

• Pb-free (RoHS compliant)

Applications

• PDAs, Cell Phones and Smart Phones

• Portable Instruments, MP3 Players

• Handheld Devices including Medical Handheld

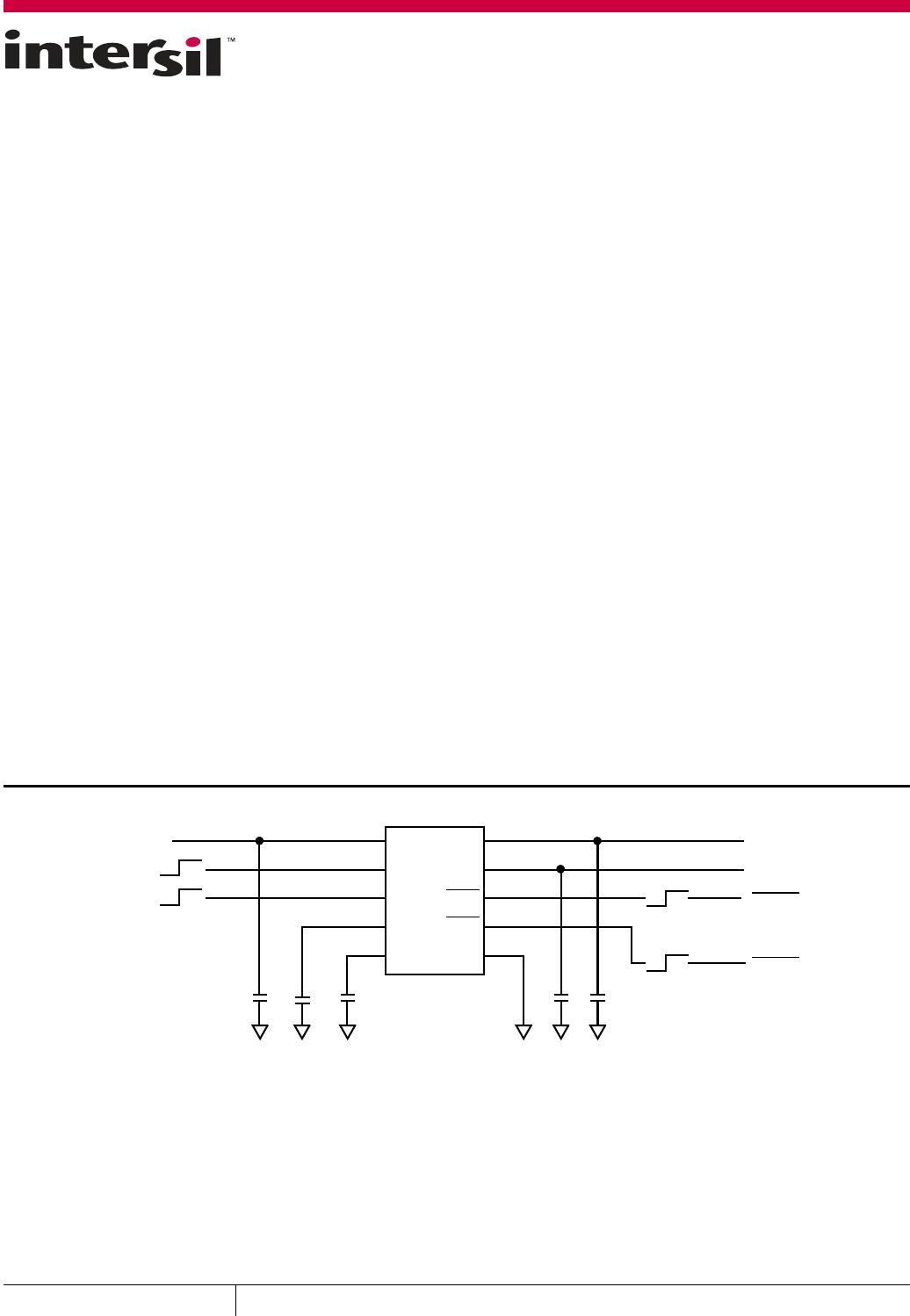

FIGURE 1. TYPICAL APPLICATION

C1, C4, C5: 1µF X5R CERAMIC CAPACITOR

C2: 0.1µF X7R CERAMIC CAPACITOR

ISL9000A

VIN

EN1

EN2

CBYP

CPOR

VO1

VO2

POR2

POR1

GND

10

9

8

7

6

1

2

3

4

5

VIN (2.3 TO 6.5V)

ENABLE1

ENABLE2

VO1

VO2

RESET1

RESET2

C1 C2 C3 C4 C5

C3: 0.01µF X7R CERAMIC CAPACITOR

OFF

ON

OFF

ON

(200ms DELAY,

C3 = 0.01µF)

(2ms DELAY)

VO2 TOO LOW

VO2 OK

VO1 TOO LOW

V

OUT1

OK

October 15, 2015

FN6391.3

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774

| Copyright Intersil Americas LLC 2007, 2008, 2015. All Rights Reserved

Intersil (and design) is a trademark owned by Intersil Corporation or one of its subsidiaries.

All other trademarks mentioned are the property of their respective owners.