17

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

IDT72V295/72V2105 3.3V HIGH DENSITY CMOS

SUPERSYNC FIFO

TM

131,072 x 18, 262,144 x 18

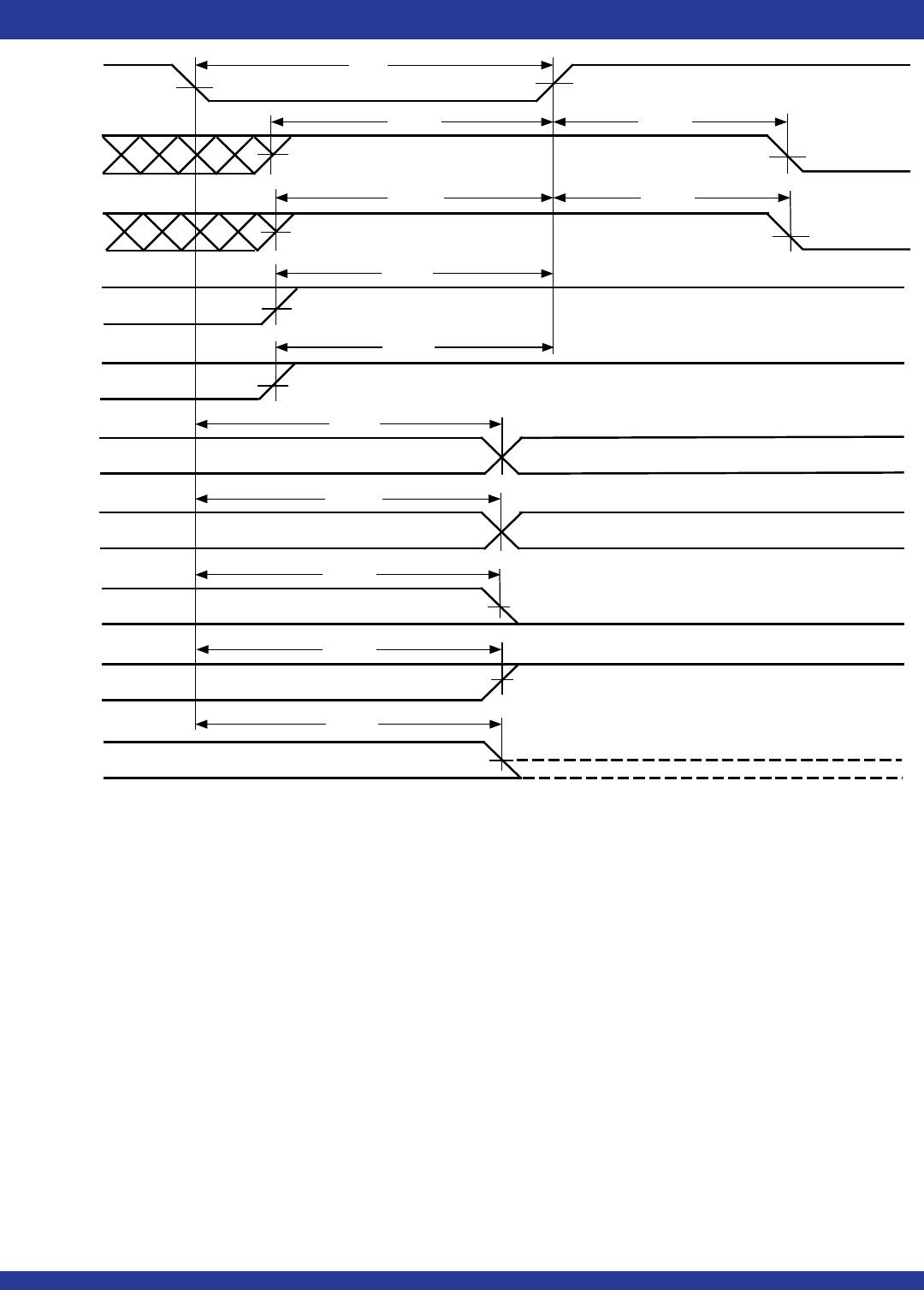

Figure 8. Read Cycle, Empty Flag and First Data Word Latency Timing (IDT Standard Mode)

NOTES:

1. tSKEW1 is the minimum time between a rising WCLK edge and a rising RCLK edge to guarantee that EF will go HIGH (after one RCLK cycle plus tREF). If the time between the rising edge

of WCLK and the rising edge of RCLK is less than tSKEW1, then EF deassertion may be delayed one extra RCLK cycle.

2. LD = HIGH.

3. First word latency: tSKEW1 + 1*TRCLK + tREF.

NOTES:

1. tSKEW1 is the minimum time between a rising RCLK edge and a rising WCLK edge to guarantee that FF will go high (after one WCLK cycle pus tWFF). If the time between the rising

edge of the RCLK and the rising edge of the WCLK is less than tSKEW1, then the FF deassertion may be delayed one extra WCLK cycle.

2. LD = HIGH, OE = LOW, EF = HIGH.

Figure 7. Write Cycle and Full Flag Timing (IDT Standard Mode)

D

0

- D

n

WEN

RCLK

REN

t

ENH

t

ENH

Q

0

- Q

n

DATA READ NEXT DATA READDATA IN OUTPUT REGISTER

t

SKEW1

(1)

4668 drw 10

WCLK

NO WRITE

1

2

1

2

t

DS

NO WRITE

t

WFF

t

WFF

t

WFF

t

A

t

ENS

t

ENS

t

SKEW1

(1)

t

DS

t

A

D

X

t

DH

t

CLK

t

CLKH

t

CLKL

D

X

+1

t

WFF

t

DH

FF

RCLK

REN

4668 drw 11

EF

t

CLK

t

CLKH

t

CLKL

t

ENH

t

REF

t

A

t

OLZ

t

OE

Q

0

- Q

n

OE

WCLK

t

SKEW1

(1)

WEN

D

0

- D

n

t

ENS

t

ENS

t

ENH

t

DS

t

DHS

D

0

1

2

t

OLZ

LAST WORD

D

0

D

1

D

1

t

ENS

t

ENH

t

DS

t

DH

t

OHZ

LAST WORD

t

REF

t

ENH

t

ENS

t

A

t

A

t

REF

t

ENS

t

ENH

NO OPERATION

NO OPERATION