DS12885/DS12887/DS12887A/DS12C887/DS12C887A

Real-Time Clocks

12 ____________________________________________________________________

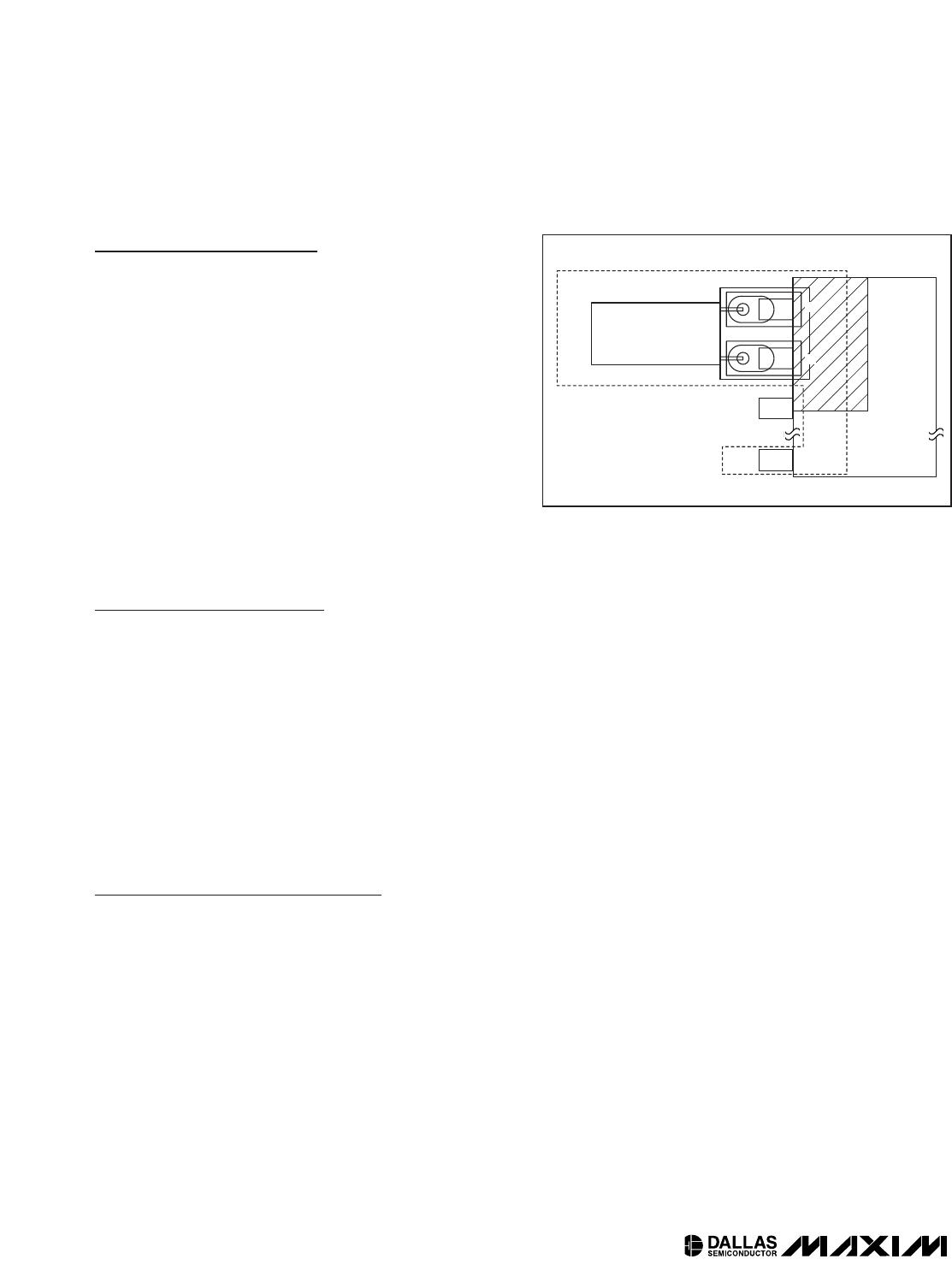

Clock Accuracy

The accuracy of the clock is dependent upon the accu-

racy of the crystal and the accuracy of the match

between the capacitive load of the oscillator circuit and

the capacitive load for which the crystal was trimmed.

Additional error is added by crystal frequency drift

caused by temperature shifts. External circuit noise cou-

pled into the oscillator circuit can result in the clock run-

ning fast. Figure 2 shows a typical PC board layout for

isolation of the crystal and oscillator from noise. Refer to

Application Note 58: Crystal Considerations with Dallas

Real-Time Clocks

for more detailed information.

Clock Accuracy for DS12887, DS12887A,

DS12C887, DS12C887A Only

The encapsulated DIP modules are trimmed at the fac-

tory to an accuracy of ±1 minute per month at +25°C.

Power-Down/Power-Up

Considerations

The real-time clock continues to operate, and the RAM,

time, calendar, and alarm memory locations remain

nonvolatile regardless of the V

CC

input level. V

BAT

must

remain within the minimum and maximum limits when

V

CC

is not applied. When V

CC

is applied and exceeds

V

PF

(power-fail trip point), the device becomes accessi-

ble after t

REC

—if the oscillator is running and the oscil-

lator countdown chain is not in reset (Register A). This

time allows the system to stablize after power is

applied. If the oscillator is not enabled, the oscillator-

enable bit is enabled on power-up, and the device

becomes immediately accessible.

Time, Calendar, and Alarm

Locations

The time and calendar information is obtained by read-

ing the appropriate register bytes. The time, calendar,

and alarm are set or initialized by writing the appropri-

ate register bytes. Invalid time or date entries result in

undefined operation. The contents of the 10 time, cal-

endar, and alarm bytes can be either binary or binary-

coded decimal (BCD) format.

The day-of-week register increments at midnight, incre-

menting from 1 through 7. The day-of-week register is

used by the daylight saving function, so the value 1 is

defined as Sunday. The date at the end of the month is

automatically adjusted for months with fewer than 31

days, including correction for leap years.

Before writing the internal time, calendar, and alarm reg-

isters, the SET bit in Register B should be written to logic

1 to prevent updates from occurring while access is

being attempted. In addition to writing the 10 time, calen-

dar, and alarm registers in a selected format (binary or

BCD), the data mode bit (DM) of Register B must be set

to the appropriate logic level. All 10 time, calendar, and

alarm bytes must use the same data mode. The SET bit

in Register B should be cleared after the data mode bit

has been written to allow the RTC to update the time and

calendar bytes. Once initialized, the RTC makes all

updates in the selected mode. The data mode cannot be

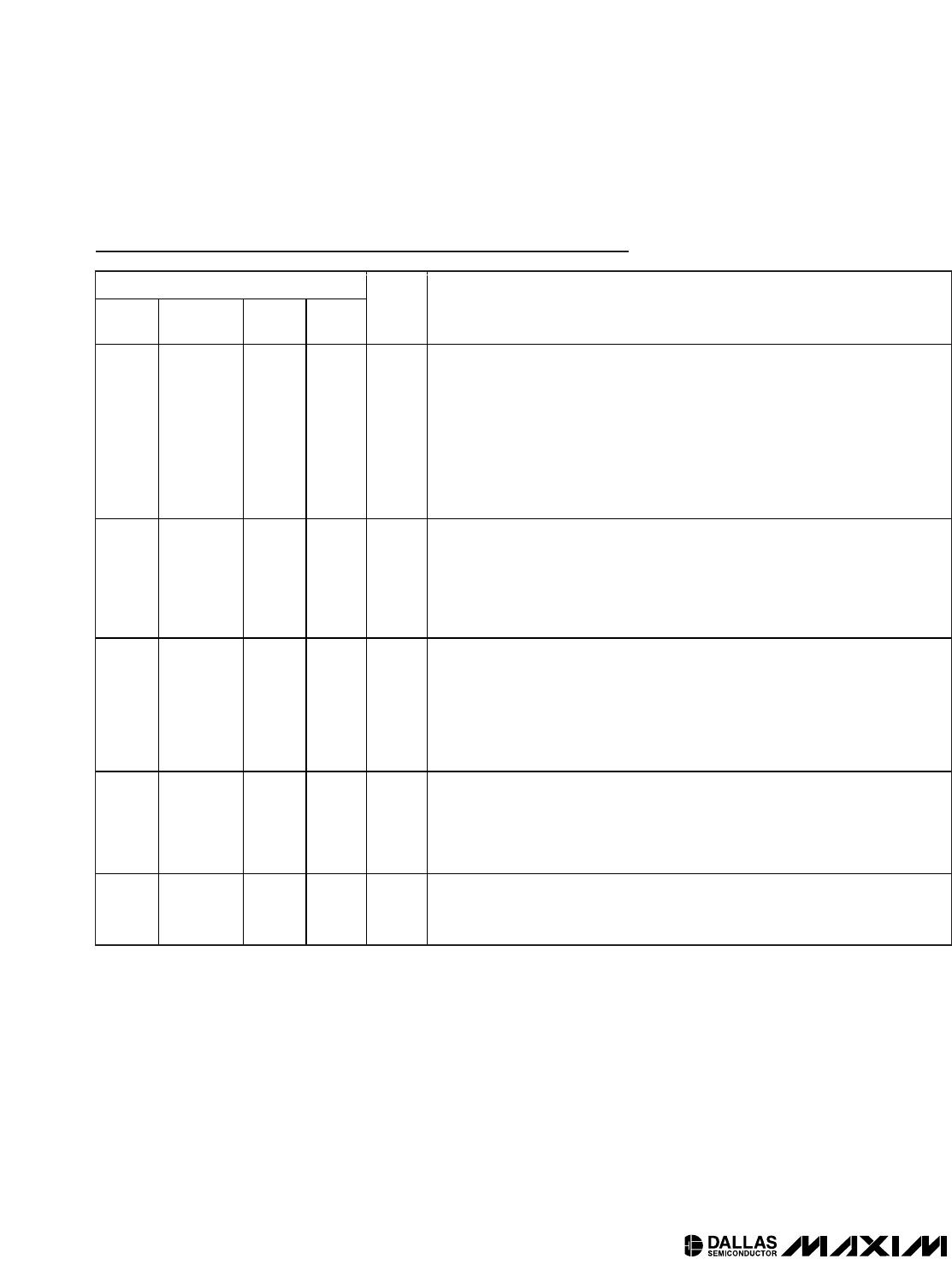

changed without reinitializing the 10 data bytes. Tables

2A and 2B show the BCD and binary formats of the time,

calendar, and alarm locations.

The 24-12 bit cannot be changed without reinitializing the

hour locations. When the 12-hour format is selected, the

higher-order bit of the hours byte represents PM when it

is logic 1. The time, calendar, and alarm bytes are always

accessible because they are double-buffered. Once per

second the seven bytes are advanced by one second

and checked for an alarm condition.

If a read of the time and calendar data occurs during

an update, a problem exists where seconds, minutes,

hours, etc., may not correlate. The probability of read-

ing incorrect time and calendar data is low. Several

methods of avoiding any possible incorrect time and

calendar reads are covered later in this text.

SIGNAL LINE AND THE DEVICE PACKAGE.