General Description

DDR3 SDRAM modules are high-speed, CMOS dynamic random access memory mod-

ules that use internally configured 8-bank DDR3 SDRAM devices. DDR3 SDRAM mod-

ules use DDR architecture to achieve high-speed operation. DDR3 architecture is essen-

tially an 8n-prefetch architecture with an interface designed to transfer two data words

per clock cycle at the I/O pins. A single read or write access for the DDR3 SDRAM mod-

ule effectively consists of a single 8n-bit-wide, one-clock-cycle data transfer at the inter-

nal DRAM core and eight corresponding n-bit-wide, one-half-clock-cycle data transfers

at the I/O pins.

DDR3 modules use two sets of differential signals: DQS, DQS# to capture data and CK

and CK# to capture commands, addresses, and control signals. Differential clocks and

data strobes ensure exceptional noise immunity for these signals and provide precise

crossing points to capture input signals.

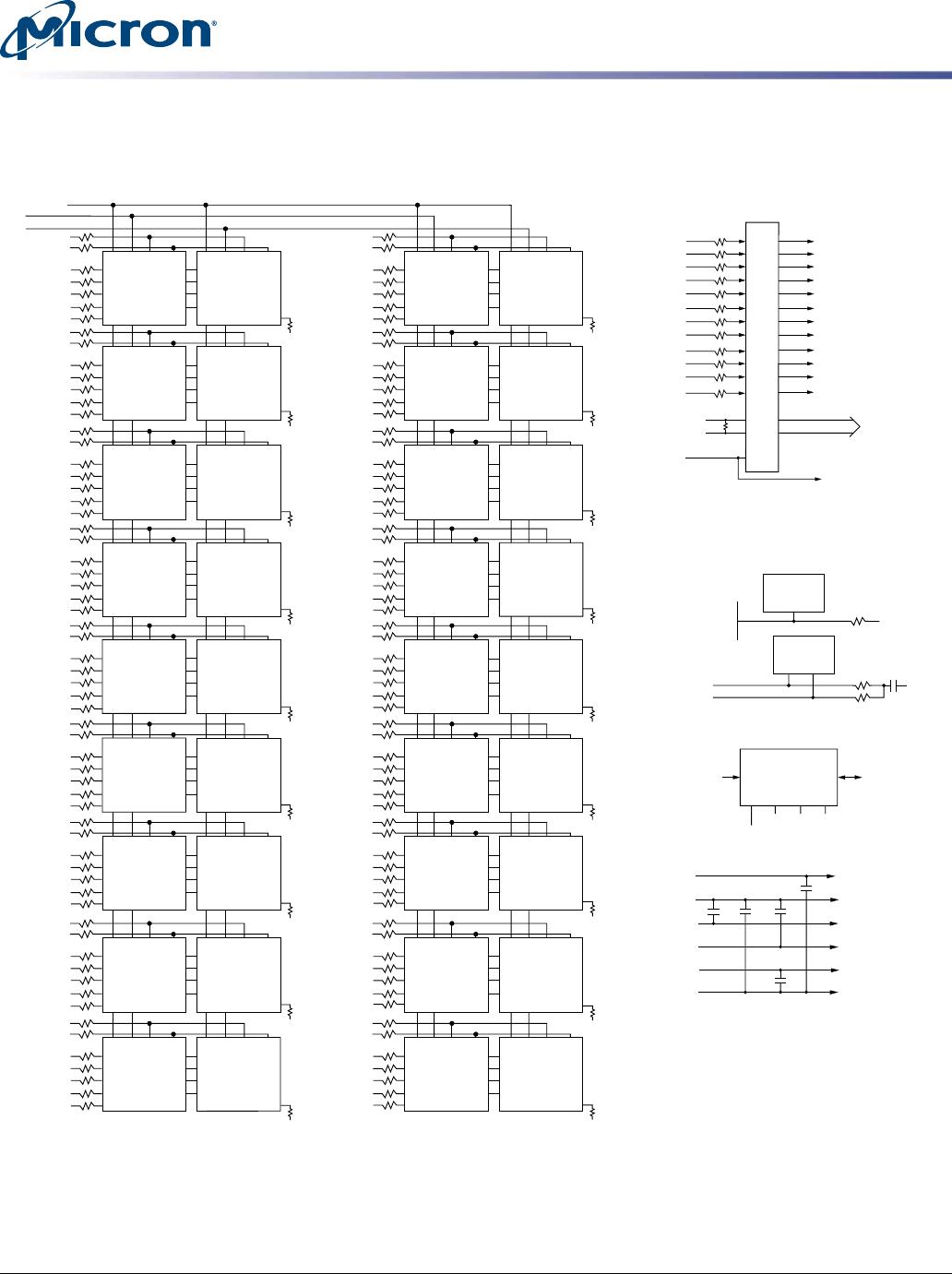

Fly-By Topology

DDR3 modules use faster clock speeds than earlier DDR technologies, making signal

quality more important than ever. For improved signal quality, the clock, control, com-

mand, and address buses have been routed in a fly-by topology, where each clock, con-

trol, command, and address pin on each DRAM is connected to a single trace and ter-

minated (rather than a tree structure, where the termination is off the module near the

connector). Inherent to fly-by topology, the timing skew between the clock and DQS sig-

nals can be easily accounted for by using the write-leveling feature of DDR3.

Registering Clock Driver Operation

Registered DDR3 SDRAM modules use a registering clock driver device consisting of a

register and a phase-lock loop (PLL). The device complies with the JEDEC standard

"Definition of the SSTE32882 Registering Clock Driver with Parity and Quad Chip Se-

lects for DDR3 RDIMM Applications."

The register section of the registering clock driver latches command and address input

signals on the rising clock edge. The PLL section of the registering clock driver receives

and redrives the differential clock signals (CK, CK#) to the DDR3 SDRAM devices. The

register(s) and PLL reduce clock, control, command, and address signals loading by iso-

lating DRAM from the system controller.

Parity Operations

The registering clock driver includes an even parity function for checking parity. The

memory controller accepts a parity bit at the Par_In input and compares it with the data

received on A[15:0], BA[2:0], RAS#, CAS#, and WE#. Valid parity is defined as an even

number of ones (1s) across the address and command inputs (A[15:0], BA[2:0], RAS#,

CAS#, and WE#) combined with Par_In. Parity errors are flagged on Err_Out#.

Address and command parity is checked during all DRAM operations and during con-

trol word WRITE operations to the registering clock driver. For SDRAM operations, the

address is still propagated to the SDRAM even when there is a parity error. When writ-

ing to the internal control words of the registering clock driver, the write will be ignored

if parity is not valid. For this reason, systems must connect the Par_In pins on the

DIMM and provide correct parity when writing to the registering clock driver control

word configuration registers.

16GB (x72, ECC, DR) 240-Pin 1.35V DDR3L RDIMM

General Description

PDF: X26P4QTWDSPK-13-10297

kds36c2gx72pz.pdf - Rev. A 2/16 EN

8

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2016 Micron Technology, Inc. All rights reserved.