LT6552

13

6552f

Layout and Passive Components

With a bandwidth of 75MHz and a slew rate of 600V/µs, the

LT6552 requires special attention to board layout and

supply bypassing. Use a ground plane, short lead lengths

and RF quality low ESR supply bypass capacitors. The

positive supply pin should be bypassed with a small

capacitor (typically 0.1µF) within 1 inch of the pin. When

driving loads greater than 10mA, an additional 4.7µF

electrolytic capacitor should be used. When using split

supplies, the same is true for the negative supply pin. The

parallel combination of the feedback resistor and gain

setting resistor on Pin 8 (FB) can combine with the input

capacitance to form a pole which can degrade stability. In

general, use feedback resistors of 1k or less.

Operating with Low Closed-Loop Gains

The LT6552 has been optimized for closed-loop gains of

2 or greater. For a closed-loop gain of 2 the response

peaks about 3dB. Peaking can be reduced by using low

value feedback resistors, and can be eliminated by placing

a capacitor across the feedback resistor (feedback zero).

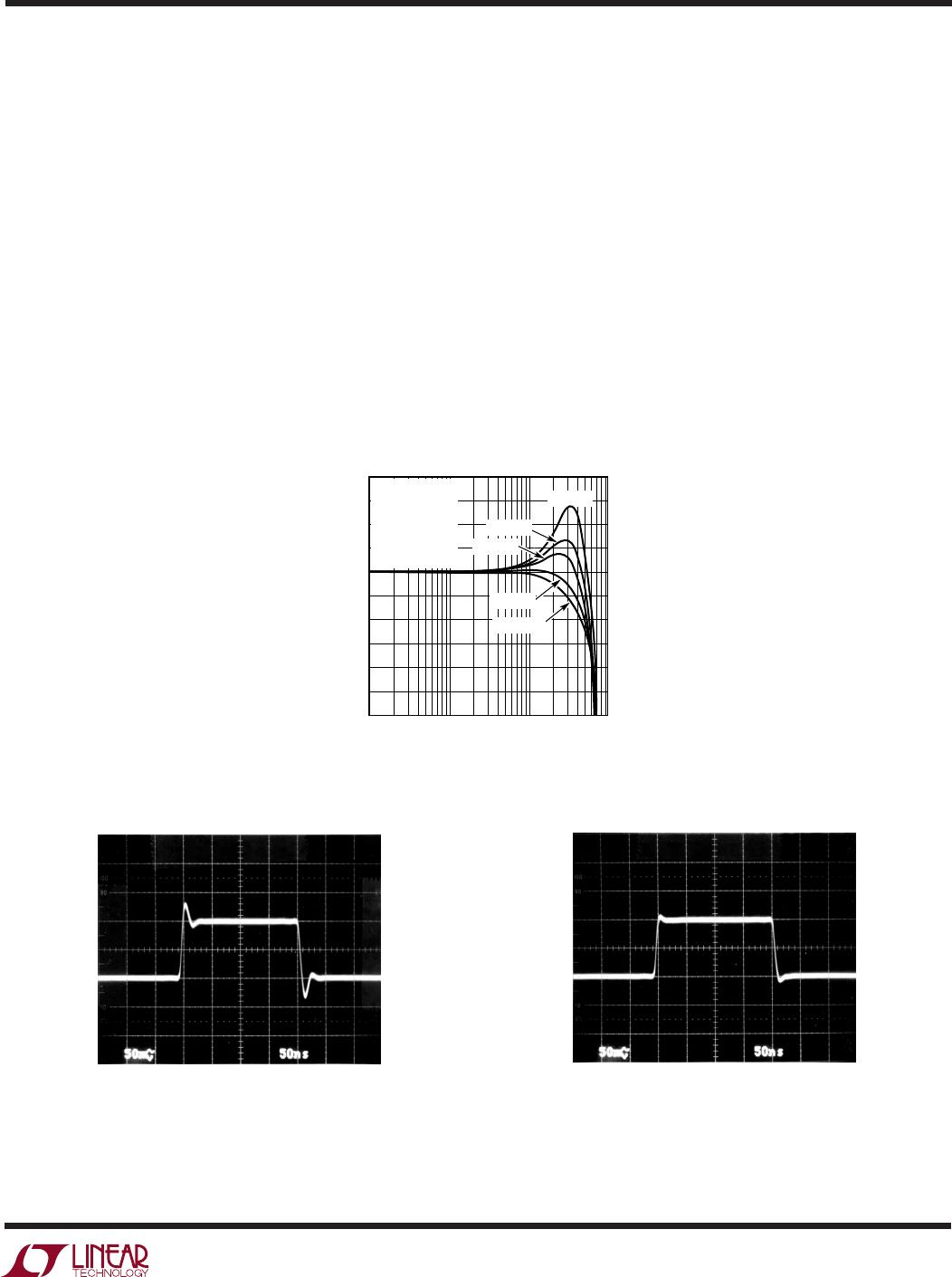

Figure 6 shows the closed-loop gain of 2 frequency

response with various values of the feedback capacitor.

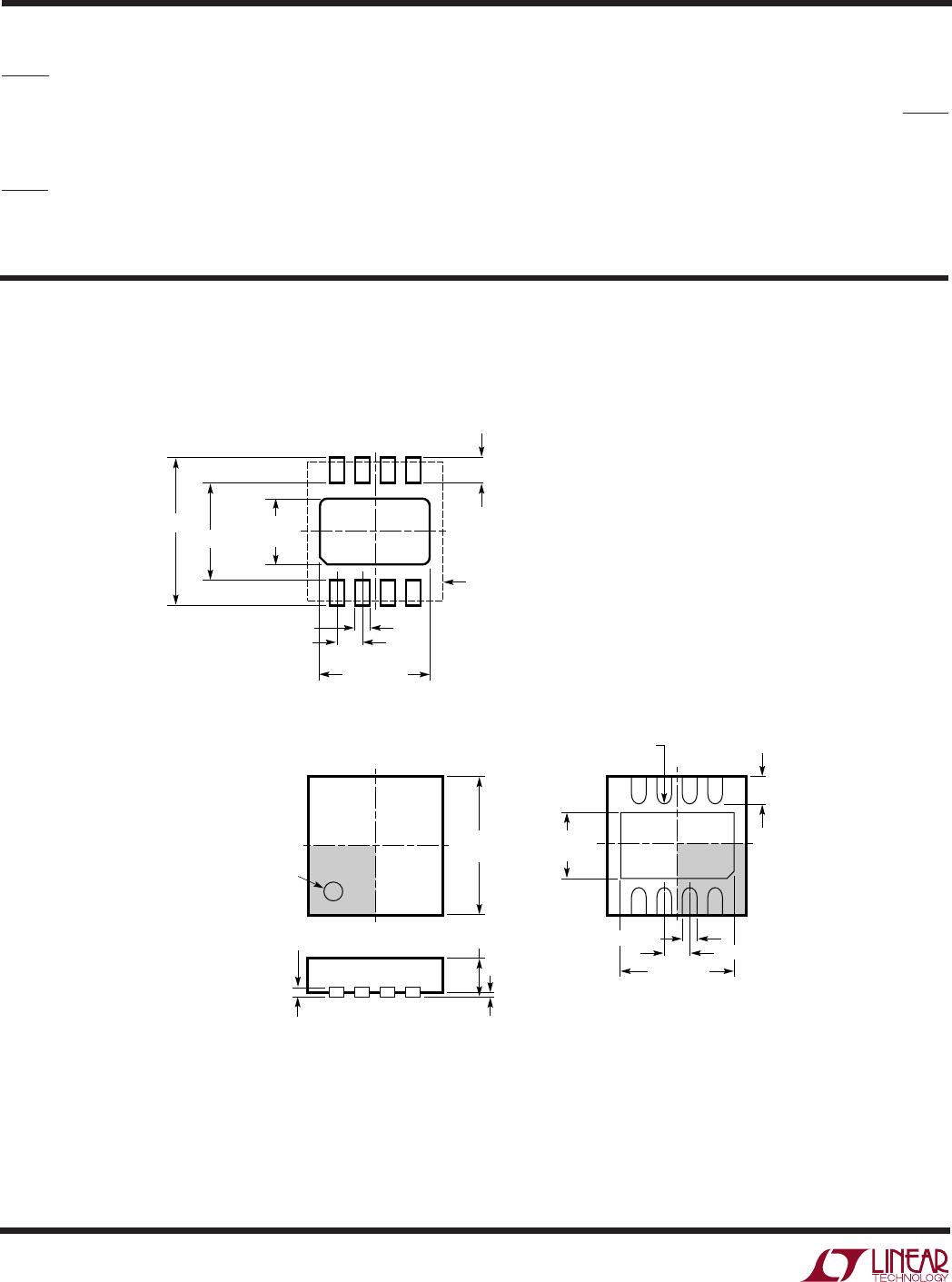

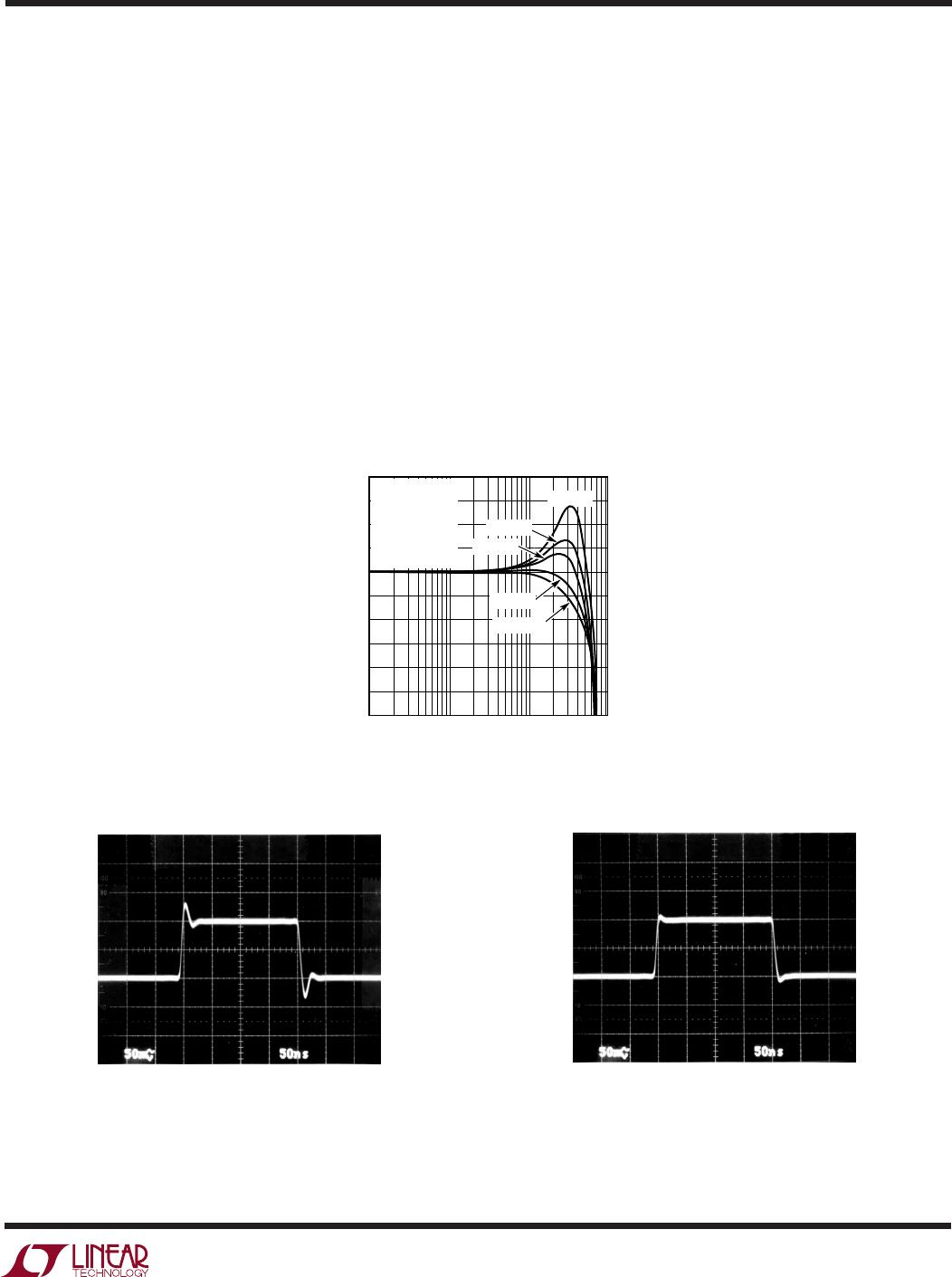

This peaking shows up as a time domain overshoot of

40%; with an 8pF feedback capacitor the overshoot is

eliminated. Figures 7A and 7B show the Small Signal

Response of the LT6552 with and without an 8pF feedback

capacitor.

Figure 6. Closed-Loop Gain vs Frequency

Figure 7A. Small Signal Transient

Response, V

S

= 3.3V, 0V

Figure 7B. Small Signal Transient Response,

V

S

= 3.3V, 0V with 8pF Feedback Capacitor

FREQUENCY (MHz)

0.1

CLOSED-LOOP VOLTAGE GAIN (dB)

10

9

8

7

6

5

4

3

2

1

0

1 10 100

6552 F06

A

V

= 2

R

F

= R

G

= 500Ω

R

L

= 150Ω

T

A

= 25°C

V

OUT

= 1.5V DC

V

S

= 3.3V, 0V

C

F

= 0pF

C

F

= 3pF

C

F

= 5pF

C

F

= 8pF

C

F

= 10pF

APPLICATIO S I FOR ATIO

WUUU

1.5V

1.5V

A

V

= 2

R

F

= R

G

= 500Ω

R

L

= 150Ω

A

V

= 2

C

F

= 8pF

R

F

= R

G

= 500Ω

R

L

= 150Ω

50ns/DIV

50mV/DIV

50mV/DIV

50ns/DIV

6552 F07a

6552 F07b