7

LTC1446/LTC1446L

Resolution (n)

Resolution is defined as the number of digital input bits,

n. It defines the number of DAC output states (2

n

) that

divide the full-scale range. The resolution does not imply

linearity.

Full-Scale Voltage (V

FS

)

This is the output of the DAC when all bits are set to one.

Voltage Offset Error (V

OS

)

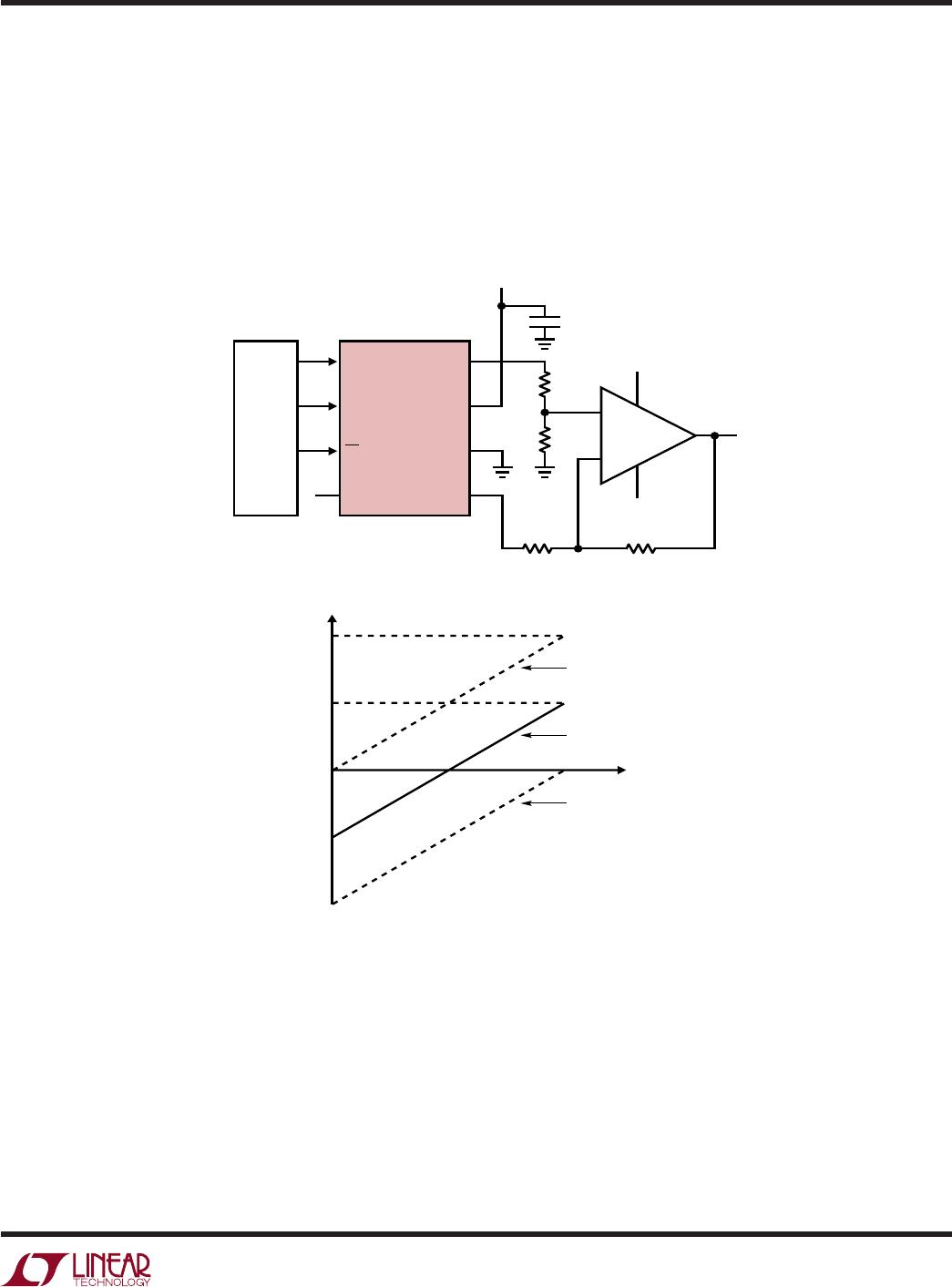

The theoretical voltage at the output when the DAC is

loaded with all zeros. The output amplifier can have a true

negative offset, but because the part is operated from a

single supply, the output cannot go below zero. If the

offset is negative, the output will remain near 0V resulting

in the transfer curve shown in Figure 1.

Nominal LSBs:

LTC1446 LSB = 4.095V/4095 = 1mV

LTC1446L LSB = 2.5V/4095 = 0.610mV

Zero Scale Error (ZSE)

The output voltage when the DAC is loaded with all zeros.

Since this is a single supply part this value cannot be less

than 0V.

Integral Nonlinearity (INL)

End-point INL is the maximum deviation from a straight

line passing through the end points of the DAC transfer

curve. Because the part operates from a single supply and

the output cannot go below 0, the linearity is measured

between full scale and the code corresponding to the

maximum offset specification. The INL error at a given

input code is calculated as follows :

INL = [V

OUT

– V

OS

– (V

FS

– V

OS

)(Code/4095)]/LSB

V

OUT

= the output voltage of the DAC measured at the given

input code

Differential Nonlinearity (DNL)

DNL is the difference between the measured change and

the ideal 1LSB change between any two adjacent codes.

The DNL error between any two codes is calculated as

follows:

DNL = (∆V

OUT

– LSB)/LSB

∆V

OUT

= The measured voltage difference between two

adjacent codes

Figure 1. Effect of Negative Offset

DAC CODE

1446/46L F01

OUTPUT

VOLTAGE

NEGATIVE

OFFSET

0V

DEFI ITIO S

UU

The offset of the part is measured at the code that corre-

sponds to the maximum offset specification:

V

OS

= V

OUT

– [(Code)(V

FS

)/(2

n

– 1)]

Least Significant Bit (LSB)

One LSB is the ideal voltage difference between two

successive codes.

LSB = (V

FS

– V

OS

)/(2

n

– 1) = (V

FS

– V

OS

)/4095