LTC1041

5

1041fa

APPLICATIO S I FOR ATIO

WUUU

R

S

• C

IN

. The ability to fully charge C

IN

from the signal

source during the controller’s active time is critical in

determining errors caused by the input charging current.

For source resistances less than 10kΩ, C

IN

fully charges

and no error is caused by the charging current.

For R

S

> 10kΩ

For source resistances greater than 10kΩ, C

IN

cannot fully

charge, causing voltage errors. To minimize these errors,

an input bypass capacitor, C

S

, should be used. Charge is

shared between C

IN

and C

S

, causing a small voltage error.

The magnitude of this error is A

V

= V

IN

• C

IN

(C

IN

+ C

S

). This

error can be made arbitrarily small by increasing C

S

.

The averaging effect of the bypass capacitor, C

S

, causes

another error term. Each time the input switches cycle

between the plus and minus inputs, C

IN

is charged and

discharged. The average input current due to this is

I

AVG

= V

IN

• C

IN

• f

S

, where f

S

is the sampling frequency.

Because the input current is directly proportional to the

differential input voltage, the LTC1041 can be said to have

an average input resistance of R

IN

= V

IN

/I

AVG

= I/(f

S

• C

IN

).

Since two comparator inputs are connected in parallel, R

IN

is one half of this value (see typical curve of R

IN

versus

Sampling Frequency). This finite input resistance causes

an error due to the voltage divider between R

S

and R

IN

.

The input voltage error caused by both of these effects is

V

ERROR

= V

IN

[2C

IN

/(2C

IN

+ C

S

) + R

S

/(R

S

+ R

IN

)].

Example: assume f

S

= 10Hz, R

S

= 1M, C

S

= 1µF, V

IN

= 1V,

V

ERROR

= 1V(66µV + 660µV) = 726µV. Notice that most of

the error is caused by R

IN

. If the sampling frequency is

reduced to 1Hz, the voltage error from the input

impedance effects is reduced to 136µV.

Figure 2. Equivalent Input Circuit

V

IN

R

S

C

S

LTC1041 • AI01

S1

S2

C

IN

(≈ 33pF)

V

–

LTC1041 DIFFERENTIAL INPUT

+

–

Input Voltage Range

The input switches of the LTC1041 are capable of

switching either to the V

+

supply or ground. Consequently,

the input voltage range includes both supply rails. This is

a further benefit of the sampling input structure.

Error Specifications

The only measurable errors on the LTC1041 are the

deviations from “ideal” of the upper and lower switching

levels (Figure 1b). From a control standpoint, the error in

the SET POINT and deadband is critical. These errors may

be defined in terms of V

U

and V

L

.

SET POINT error

V

SET POINT

deadband error V

U

U

≡

+

≡

()

V

V DELTA

L

L

2

2

–

––•

The specified error limits (see electrical characteristics)

include error due to offset, power supply variation, gain,

time and temperature.

Pulsed Power (V

P-P

) Output

It is often desirable to use the LTC1041 with resistive

networks such as bridges and voltage dividers. The power

consumed by these resistive networks can far exceed that

of the LTC1041 itself.

At low sample rates the LTC1041 spends most of its time

off. A switched power output, V

P-P

, is provided to drive the

input network, reducing its average power as well. V

P-P

is

switched to V

+

during the controller’s active time (≈ 80µs)

and to a high impedance (open circuit) when internal

power is switched off.

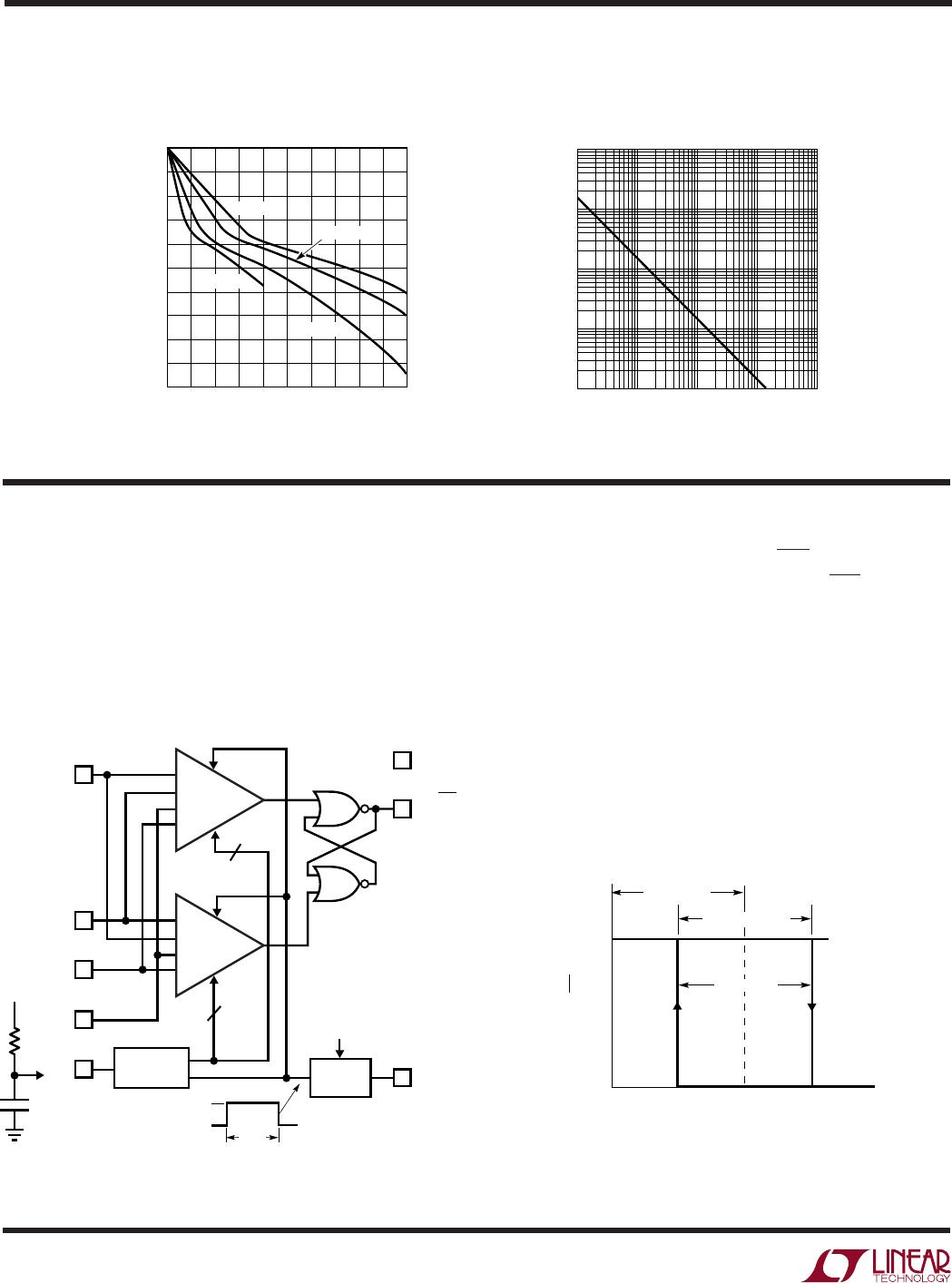

Figure 3 shows the V

P-P

output circuit. The V

P-P

output

voltage is not precisely controlled when driving a load

(see typical curve of V

P-P

Output Voltage vs Load Current).

In spite of this, high precision can be achieved in two ways:

(1) driving ratiometric networks and (2) driving fast set-

tling references.

In ratiometric networks all the inputs are proportional to

V

P-P

(Figure 4). Consequently, the absolute value of V

P-P

does not affect accuracy.